国際特許分類[G06F1/24]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | グループ3/00〜13/00および21/00に包含されないデータ処理装置の細部 (14,213) | リセット手段 (409)

国際特許分類[G06F1/24]に分類される特許

31 - 40 / 409

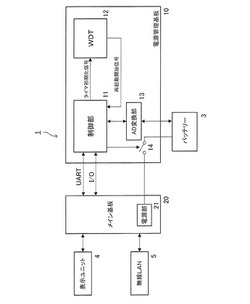

情報処理装置

【課題】情報処理装置において省電力化を図る。

【解決手段】本発明に係る情報処理装置1は、リセット時間よりも短い設定時間であって、動作状態毎に異なる設定時間の値を記憶し、変移した動作状態に対応する設定時間を周期としてタイマ初期化信号を出力するタイマ初期化処理と、再起動開始信号の入力に応じて再起動する再起動処理を実行する制御部11と、タイマ初期化信号が入力されてからの経過時間を計時するとともに、経過時間がリセット時間に至った場合、制御部に対して再起動開始信号を出力する監視部12と、を備えたことを特徴とするものである。

(もっと読む)

半導体装置

【課題】大きな外付け容量素子による時定数に依存することなく遅延時間を設定でき、ユーザが実装システム上でリセット解除に代表されるパルス変化の遅延時間を容易に変更する事ができ、電源瞬停時にリセット解除に代表されるパルス変化までの遅延時間が短くなる虞を抑制する。

【解決手段】発振回路(3)の発振動作で生成されるパルス信号をカウントし、カウント値が所定値に達したところでリセット解除に代表されるパルス変化のタイミングを生成する技術において、半導体装置の外部端(P1)子に接続される抵抗素子(R8)の抵抗値によって発振回路の発振周波数を可変にする。外付け抵抗素子によってリセット解除に代表されるパルス変化のタイミングを可変に設定することができ、それは、大きな外付け容量素子を用いる時定数に依存する遅延時間を必要とせず、故に、電源瞬停時にリセット解除に代表されるパルス変化までの遅延時間は短くならない。

(もっと読む)

リセット回路およびシステム

【課題】 パワーオンまたはパワーダウンを検出するリセット回路を誤動作することなく動作させ、パワーオン時にリセット信号を正常に出力する。

【解決手段】 電源検出回路は、電源電圧が第1電圧を超えたときにパワーオン状態を示すパワーオン信号を活性化するとともに、初期化信号の活性化中に初期化される。スタータ回路は、電源電圧線と接地線の間に直列に配置された抵抗素子、遮断スイッチおよびキャパシタを有し、抵抗素子と遮断スイッチとを接続する第1接続ノードから初期化信号を出力する。遮断スイッチは、パワーオン信号の活性化中にオフする。このため、パワーオン状態中に、抵抗素子を介してキャパシタが充電されることを防止できる。この結果、キャパシタのTDDBの劣化を確実に防止でき、リセット回路を搭載する半導体装置およびシステムの誤動作を防止できる。

(もっと読む)

不揮発性メモリの初期化装置および初期化方法

【課題】不揮発性メモリの初期化の手順の簡略化を図るとともに検査装置を検査に必要な最少限の構成とする。

【解決手段】予め不揮発性メモリの特定の値を書き換える信号を電子制御装置に入力し、電源投入により不揮発性メモリに対してイニシャル処理を行い、イニシャル処理で不揮発性メモリの初期化が必要と判断されたとき、前記書き換え信号により、不揮発性メモリに対して不揮発性メモリの特定の値を書き換える初期化処理を行う。

(もっと読む)

半導体装置及び半導体装置におけるリセット制御方法

【課題】外部からのリセット要求が入力されたとき、同期してリセット信号を出力するか、非同期でリセット信号を出力するかを、動作ステートに応じて適切に切り替えることができるようにする。

【解決手段】直列接続された複数の保持部を有するリセット要求保持部に外部からのリセット要求を保持し、リセット切替部が複数の保持部の出力のすべてを論理積演算して非同期リセット要求とするとともに複数の保持部の最終段の保持部の出力を同期リセット要求として非同期リセット要求と同期リセット要求を論理積演算して演算結果を出力するとともに、同期リセットモードでは非同期リセット要求をマスクし、リセット切替部での演算結果に基づいてリセット出力部よりリセット信号を出力する。

(もっと読む)

減電圧リセット回路及びこれを用いた電源装置

【課題】より確実に安定した減電圧監視を行うことが可能な減電圧リセット回路及び電源装置を提供する。

【解決手段】減電圧リセット回路15は、ドレインがリセット信号出力端子T5に接続されたNチャネル型の第1トランジスタ153と、ドレインがリセット信号出力端子T5に接続されたNチャネル型の第2トランジスタ154と、監視対象電圧V1の供給を受けて動作し、監視対象電圧V1が第1閾値電圧を下回っているときに第1トランジスタ153をオンさせる第1監視部151と、監視対象電圧V1とは異なる駆動電圧V0の供給を受けて動作し、監視対象電圧V1が第1閾値電圧よりも低く第1監視部151の下限動作電圧よりも高い第2閾値電圧を下回っているときに第2トランジスタ154をオンさせる第2監視部152と、を有する。

(もっと読む)

ICチップ、ICチップにおけるメモリ初期化方法、ICチップ用処理プログラム、携帯端末

【課題】インターフェースが行う処理動作に影響を与えることなく、効率よくメモリを初期化可能なICチップ等を提供する。

【解決手段】複数のインターフェースを備え、各インターフェースが非同期に他の通信端末と通信するために動作するICチップであって、すべての前記インターフェースの動作処理に用いられる共通の情報が記憶される共通領域、各インターフェースの動作処理のみで用いられる情報が記憶される専用領域、とを有するメモリと、1のインターフェースの起動を検出する第1の検出手段と、検出した前記インターフェースの起動後、各インターフェースの動作状態を検出する第2の検出手段と、前記各インターフェースの動作状態に応じて、当該共通領域又は少なくとも1のインターフェースの専用領域を初期化する初期化手段と、を備えている。

(もっと読む)

電子機器装置

【課題】電子機器装置において、電源供給が瞬間的に断たれたときに、マイコンが異常状態にならないようにする。

【解決手段】電子機器装置1は、マイコン6と、リセットIC7と、電圧低下回路8とを備える。マイコン6は、ハイレベルの信号が入力されている状態からローレベルの信号が入力される状態に変化すると、動作をリセットし、ローレベルの信号が入力されている状態からハイレベルの信号が入力される状態に変化すると、起動処理を実行し、その後、通常処理を実行する。リセットIC7は、所定電圧値未満の電圧が入力されているときには、マイコン6にローレベルの信号を入力し、所定電圧値以上の電圧が入力されているときには、マイコン6にハイレベルの信号を入力する。電圧低下回路8は、商用AC電源10から電子機器装置1への電源供給が瞬間的に断たれたときに、リセットIC7に入力される電圧を一時的に所定電圧値未満に低下させる。

(もっと読む)

検査装置及び方法

【課題】検査対象回路が正常に機能しているか否かを電源電圧の立ち上がり期間に拘らず高精度に検査することができる半導体集積回路、検査装置及び方法を提供する。

【解決手段】検査装置10を、POR回路102の出力端子102Cから第1入力端子14Aにリセット信号が入力されたときに出力端子14Cからリセット信号と同レベルのリセット実行信号の出力を開始し、制御装置18の出力端子から第2入力端子14Bにトリガ信号が入力されたときにリセット実行信号の出力を終了して出力端子14Cからリセット解除信号と同レベルの解除実行信号の出力を開始するリセット制御回路14と、リセット制御回路14から出力された信号が予め定められたレベルであるか否かを判定することによりPOR回路102が正常に機能しているか否かを判定するテスタ124と、を含んで構成した。

(もっと読む)

コンピュータのリセット方法およびコンピュータ

【課題】筐体を開放しないでRTCメモリをリセットする。

【解決手段】カレンダー時刻およびBIOSの設定情報を記憶するRTCメモリ25には、バックアップ電池51から電力が供給される。コンピュータがパワー・オフ状態のときにパワー・コントローラ31には電力が供給される。パワー・オフ状態においてキーボード63のFnキーおよびパワー・ボタン61を同時に押下すると、パワー・コントローラ31はリセット・スイッチ91を所定時間だけオフにしその後オンにする。その後、パワー・コントローラ31は自らに供給されている電力を一旦停止してから復帰させる。

(もっと読む)

31 - 40 / 409

[ Back to top ]