国際特許分類[G11C15/04]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 1つ以上の特徴表示部分を含む情報が書き込まれ,情報の読出しはそれらの1つ以上の特徴表示部分について探索することによって行なわれるデジタル記憶装置,すなわち連想記憶または内容アドレス記憶装置 (108) | 半導体素子を用いるもの (101)

国際特許分類[G11C15/04]に分類される特許

21 - 30 / 101

連想記憶装置

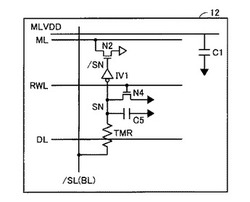

【課題】ソフトエラーおよびスタンバイ電流を発生させずに、高速検索が可能な連想記憶装置を提供する。

【解決手段】連想メモリセルは、一端がサーチ線SLに接続されるトンネル磁気抵抗素子TMRと、トンネル磁気抵抗素子TMRの他端に接続される容量素子C5と、トンネル磁気抵抗素子TMRの他端と接地電源との間に設けられ、制御電極がワード線RWLと接続される第1のMOSトランジスタN4と、マッチ線MLと接地電源との間に設けられ、制御電極がトンネル磁気抵抗素子TMRの他端に生じた電圧を受ける第2のMOSトランジスタN2とを含む。

(もっと読む)

データ一括比較処理回路、データ一括比較処理方法およびデータ一括比較プログラム

【課題】ブロック間のデータを一括で比較し、データ量に依存しないで高速にデータ比較が行える処理方法等を提供する。

【解決手段】各々の出力がメモリセルの列に対応して配置される一対のビットラインの各々に至る経路に接続されるクロスカップル接続された一対のインバータと、ビットラインとインバータの出力との間に設けられた一対のスイッチ部と、スイッチ部の導通を制御する1本のワードラインとから構成される1ビットのメモリセルが上段と下段に隣接し、隣接する2個のメモリセルのデータ保持ノード間にモード制御スイッチ部と、該モード制御スイッチ部の導通を制御する1本のモード制御ラインと、を備えたメモリセルペアを配列させたメモリセルアレイを用いる。メモリセルペアの上段・下段に比較すべきデータを書き込み、モード制御ラインを導通し、メモリセルペアのノードを接続し、電源電圧をフローティング状態にし、データの一致性を判定する。

(もっと読む)

連続検索サイクルを中断させない読み出し/書き込み機能を有するコンテントアドレサブルメモリ

【課題】コンテントアドレサブルメモリ(CAM)を提供する。

【解決手段】CAMは、各クロックサイクルで検索動作を実行するための検索ポート102bと、コンテントアドレサブルメモリのアドレス位置でデータの書き込みおよび読み出しをするためのメンテナンスポート103aと、を備える。また、インターロック信号が備えられており、検索ポートからメンテナンスポートに伝送されることにより、コンテントアドレサブルメモリに対してデータの書き込みおよび読み出しを実行すべき時を設定し、この結果、検索動作が中断することなく各クロックサイクルで継続する。インターロック信号は、検索動作の終了時および検索プリチャージ動作の開始時に伝送されることが好ましい。メンテナンスポートは、クロックサイクルの開始時に書き込み動作をセットアップし、検索動作の終了時および検索プリチャージ動作の開始時に書き込み動作を実行するように構成されている。

(もっと読む)

内容参照メモリ

【課題】検索動作を高速かつ低消費電流で実行することのできる内容参照メモリを提供する。

【解決手段】マッチ線(ML)の電位を検出するマッチアンプ(40)において、マッチ線を接地電圧レベルにプリチャージするプリチャージトランジスタ(60)と、検索データとの比較動作時にマッチ線に電流値が制限された電流をマッチ線に供給し、かつマッチ線の電圧レベルを比較動作時にクランプするとともにマッチ線の電圧レベルに応じた信号を生成するプルアップ電流供給/判定回路(100)とを設ける。

(もっと読む)

アドレス合計比較書込み再符号化および比較削減のための方法および装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

SeOIの連想メモリでデータを比較するデバイス

【課題】連想メモリの比較デバイス、比較デバイスを制御する方法、および連想メモリを提供する。

【解決手段】データビットを格納する第1のトランジスタT1およびデータビットの補数を格納する第2のトランジスタT2によって形成されたメモリセルであって、各トランジスタは、セミコンダクタ・オン・インシュレータ基板上に作られ、各々は、フロント制御ゲート、およびトランジスタを遮断するように制御するバック制御ゲートBG1、BG2を有する、メモリセルと、各々のフロント制御ゲートに公称読出し電圧を加えることによって読出しモードで動作させ、一方、バック制御ゲートBG1、BG2を、一方をビット(DATA)、他方をビットの補数(DATAb)で制御し、ビット(DATA)と格納されたビットが一致する場合には各々のうちの通過トランジスタを遮断し、各々のソースに連結されたソース線SLの電流の有無を検出する比較回路を備える。

(もっと読む)

連想記憶装置

【課題】低消費電力化と高速化の両立が可能な連想記憶装置を提供する。

【解決手段】マッチアンプAは、マッチラインMLAの電圧に応じて、メモリアレイAのエントリ内の連想メモリに記憶されたデータと検索データとの一致または不一致を判定する。マッチアンプBは、マッチラインMLBの電圧に応じて、メモリアレイBのエントリ内の連想メモリに記憶されたデータと検索データとの一致または不一致を判定する。

ブロックB制御回路210は、メモリアレイAでの検索を開始してから、2サイクル後に、メモリアレイBでの検索を開始させる。ブロックB活性化制御回路207は、メモリアレイAの検索後のマッチラインMLAの電圧に応じて、メモリアレイBでの検索動作を中止させる。

(もっと読む)

半導体装置およびベリファイ方法

【課題】CAMセルを備える半導体装置において、データの書き換えやベリファイを正常に行うことができる半導体装置およびベリファイ方法を提供する。

【解決手段】本発明の半導体装置は、半導体装置1の動作設定情報を記憶するCAM用セルアレイ4と、CAM用セルアレイの読出しと書込みを制御するコントローラ8、ローデコーダ5、コラムデコーダ6を有し、動作設定情報の異なる機能ブロックごとに異なるローアドレスを割り付ける構成を備えている。動作設定情報の機能毎に異なるローアドレスを割り付けるので、プログラム時に、選択されていない機能のCAM用セルアレイ4にストレスを与えることがない。

(もっと読む)

CAM装置及びそれを備えるトランスレーション・ルックアサイド・バッファ

【課題】従来のCAM装置では、一致判定が正確にできない場合があった。

【解決手段】仮想アドレスのビットパターンのうち所定のビットをマスク対象とすることで、仮想アドレス空間における第1のページを定義し、その第1のページを示す第1のエントリデータを格納するCAM装置であって、仮想アドレスのビットパターンのうち所定のビットをマスク対象とした入力データのビットパターンと、前記第1のエントリデータのビットパターンとを比較するとき、前記入力データのマスク対象のビットと対応する前記第1のエントリデータのビットが、マスク対象でない場合であっても、前記入力データのマスク対象のビットと対応する前記第1のエントリデータのビットを、一致しているものとみなすCAM装置。

(もっと読む)

半導体装置

【課題】CAMにおけるメモリセル面積の縮小化を図る。

【解決手段】データ線(D0,D1)を第1記憶部(MA)及び第2記憶部(MB)とで共有し、また、第1比較データ線(CD0)に結合された第1トランジスタ(MC0)と、第1記憶部の記憶ノードに結合された第2トランジスタ(MCA)とを直列接続して第1比較回路(11)を形成し、第2比較データ線(CD1)に結合された第3トランジスタ(MC1)と、上記第2記憶部の記憶ノードに結合された第4トランジスタ(MCB)とを直列接続して第2比較回路(12)を形成することは、拡散層や配線層のレイアウトにおける対称性を向上させ、メモリセルをその中心を通る中心線に対して線対称となるレイアウトの容易化を達成する。それにより製造プロセス条件を最適化し易くなり、製造プロセスのばらつきが低減されてメモリセルの微細化が達成される。

(もっと読む)

21 - 30 / 101

[ Back to top ]