国際特許分類[G11C15/04]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 1つ以上の特徴表示部分を含む情報が書き込まれ,情報の読出しはそれらの1つ以上の特徴表示部分について探索することによって行なわれるデジタル記憶装置,すなわち連想記憶または内容アドレス記憶装置 (108) | 半導体素子を用いるもの (101)

国際特許分類[G11C15/04]に分類される特許

41 - 50 / 101

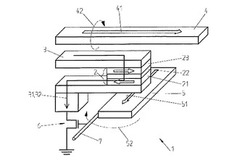

三値連想磁気抵抗ランダムアクセスメモリセル

【課題】磁気ランダムアクセスメモリ(MRAM)に基づいた三値連想メモリ(TCAM)に書き込んで検索する方法を提供する。

【解決手段】三値連想メモリセル1は、ストレージ層23から形成されている第1磁気トンネル接合2、ストレージ層の磁化に対して調整可能な磁化方向を有するセンス層21、及び、ストレージ層とセンス層との間の絶縁層22を有し、ストレージ層に接続されているセンス線3を有し、第1フィールド線4及び第2フィールド線5を有する。第1フィールド線は、第2フィールド線に対して直交し、第2フィールド線を介してストレージ層に対して第1書込みデータを提供して、高い論理状態又は低い論理状態を有する第1記憶データを記憶する。第1フィールド線を介してストレージ層に対して第1書込みデータを提供して、マスクされた論理状態を有する第1記憶データを記憶する。

(もっと読む)

ダイナミック連想メモリセル

【課題】2値または3値保存性能を有するダイナミック連想メモリを提供する。

【解決手段】ダイナミック連想メモリは、ビット・ラインとワード・ラインの交差部に位置する複数のダイナミック連想メモリセルを備える。各セルは、ワード・ラインに接続されるゲート端子およびビット・ラインに接続される第1ソース/ドレイン端子を有するアクセス・トランジスタと、アクセス・トランジスタの第2ソース/ドレイン端子に接続される第1プレートを有する第1メモリセル・キャパシタと、ポリシリコン相互接続層だけを介してアクセス・トランジスタの第2ソース/ドレイン端子に接続されるゲート端子を有する、マッチ・ラインの整合結果または不整合結果を示すための比較トランジスタとを含む。

(もっと読む)

連想メモリデータエラー検出装置及び連想メモリデータエラー検出方法並びにプログラム

【課題】データ検索時に、連想メモリ(CAM)の内部データのエラーをリアルタイムで検出できるようにする。

【解決手段】CAM5にデータを登録する際には、記憶媒体3にも同一内容のデータを登録しておく。データ検索時に、制御部21から検索キーeが出力されると、エラー監視部22は内部のレジスタ23に検索キーeをセットし、CAM5は検索キーeと同一内容のデータが登録されているアドレスを検索結果fとして出力する。エラー監視部22は、検索結果fをリードアドレスgとして記憶媒体3からデータhを読み出し、レジスタ23に保持されている検索キーeと比較する。そして、比較一致の場合は、データ検索が正常終了したと判断し、CPU4に対して検索結果fと正常終了通知iとを出力する。これに対して、比較不一致の場合は、CAM5の内部データにエラーが発生していると判断し、CPU4に対して異常終了通知jを出力する。

(もっと読む)

連想メモリ装置

【課題】DAアドレス及びSAアドレスの検索を高速に実施できるとともに、アドレス学習、エージングを確実に実施することが可能な連想メモリ装置を提供する。

【解決手段】メモリ制御回路が、検索対象のキー情報が連想メモリに記憶されていない場合、当該連想情報に対応するキー情報及び制御情報を各連想メモリに書き込むよう通知するとともに、当該通知が自己の連想メモリに関するものであると、自己の連想メモリに登録済みのオーナーフラグを自己の連想メモリに書き込むように制御し、通知が他の連想メモリに関するものであると、当該連想情報が自己の連想メモリに未登録であることが設定されたオーナーフラグを自己の連想メモリに書き込むように制御する。さらに、エージングを実施するにあたり、オーナーフラグが登録済に設定されたキー情報及び連想情報を削除対象とする。

(もっと読む)

相変化デバイスを用いた高密度コンテンツ・アドレス可能メモリ

【課題】 相変化デバイスを用いた高密度コンテンツ・アドレス可能メモリ・アレイを提供すること。

【解決手段】 ストアド・ワードをメモリ素子にストアするコンテンツ・アドレス可能メモリ・アレイを提供する。各メモリ素子は、少なくとも2つの相補的バイナリ・ビットのうちの1つを、少なくとも2つの相補的抵抗のうちの1つとしてストアする。各メモリ素子はアクセス・デバイスに電気的に結合される。コンテンツ・アドレス可能メモリ・アレイの一態様は、バイアス回路を用いて検索動作中にアクセス・デバイスにバイアスをかけることである。検索動作中、ビット・ストリングを含む検索ワードが受信される。各アクセス・デバイスはバイアスをかけられて、検索ワード内の対応する検索ビットの相補的な抵抗値になる。メモリ素子内にストアされたビットがアクセス・デバイス内の抵抗により表されるビットに対して相補的である場合に、検索ワードとストアド・ワードの間のマッチが指示される。

(もっと読む)

連想メモリ装置

【課題】DAアドレス(宛先アドレス)及びSAアドレス(送信元アドレス)の検索を高速に実施できる連想メモリ装置を提供する。

【解決手段】検索対象のMACアドレスから算出したハッシュ値に対応するバケットを選択し、選択された連想メモリのバケットから所定数の情報を一括して読み出し、検索対象のMACアドレスに対応するポート情報等を検索するとともに、検索されたMACアドレス及びこれに関連付けられたポート情報等を連想メモリに登録するにあたり、検索対象のMACアドレスに一致する情報が連想メモリに記憶されていないと判定されると、検索が実行された複数のバケット内の同一の空き領域アドレスに対して一括に、MACアドレス及びポート情報等を書き込む。

(もっと読む)

内容参照メモリ

【課題】内容参照メモリのアレイ面積および消費電力を低減する。

【解決手段】各々が検索対象データを記憶する複数のエントリ(ENT♯0−ENT♯N−1)に共通に、一致判定および大小判定を行なう比較回路(15)を設ける。各エントリにおいては、データを記憶するデータ記憶セル(CEL0)と、これより数か少ないマスクビットを記憶するマスクセル(CEL1)を設ける。比較回路に対してサーチデータをサーチデータバス(SLB)を介して伝達する。1つのエントリを所定の法則に従って選択し、比較回路により、マスクビットをデコードしてマスク指示信号を生成するとともに、サーチデータと選択されたエントリに記憶される検索対象データとの一致比較および大小比較を行なう。

(もっと読む)

連想メモリ

【課題】検索後、スタンバイ状態に戻る際に充電を必要とするマッチラインの数を減らし、消費電流の低減化を図ることができる連想メモリを提供する。

【解決手段】検索コマンド信号XSERが“0”とされ、検索が指示されると共に、検索データDINが与えられると、サーチドライバ部36を活性化し、メモリセルアレイ31を対象として検索を実行し、検索データDINがメモリセルアレイ31に記憶されているデータのいずれかと一致した場合には、サーチドライバ部37を非活性とし、メモリセルアレイ32を対象とした検索を実行せず、検索データDINがメモリセルアレイ31に記憶されているデータの全てと不一致の場合にのみ、サーチドライバ部37を活性化し、メモリセルアレイ32を対象とした検索動作を実行する。

(もっと読む)

連想メモリ

【課題】検索後、スタンバイ状態に戻る際に充電を必要とするマッチラインの数を減らし、消費電流の低減化を図ることができる連想メモリを提供する。

【解決手段】2m+1番地(但し、m=0、1、2、…、255である)のメモリセル3(2m+1、p)については、ゲートがサーチバスSB(p)又はXSB(p)に接続されているNMOSトランジスタ11(2m+1、p)、12(2m+1、p)のソースを2m番地のマッチラインML2mに接続する。例えば、1番地のメモリセル3(1、p)については、ゲートがサーチバスSB(p)又はXSB(p)に接続されているNMOSトランジスタ11(1、p)、12(1、p)のソースを0番地のマッチラインML0に接続する。

(もっと読む)

連想メモリおよびそれを用いた検索システム

【課題】検索データに近い複数の参照データを出力可能な連想メモリを提供する。

【解決手段】メモリアレイ部10は、複数の参照データの各々と検索データとの比較を並列に実行し、その比較結果を示す複数の比較電流信号C1〜CRを生成する。WLA回路20は、複数の比較電流信号C1〜CRを複数の電圧VC1〜VCRに変換する。そして、WLA回路20は、第1周期において、複数の電圧VC1〜VCRのうち、最も低い電圧をWinnerとし、残りの電圧をLoserとして検出する。第2周期以降、WLA回路20は、フィードバック信号FB1〜FBRに基づいて、前回、Winnerとして検出した電圧を除く残りの電圧を検出し、その検出した残りの電圧のうち、最も低い電圧をWinnerとし、残りの電圧をLoserとして検出する。WLA回路20は、この動作をk回繰り返す。

(もっと読む)

41 - 50 / 101

[ Back to top ]