国際特許分類[G11C29/00]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 正確な動作のための記憶装置のチェック;スタンバイまたはオフライン動作中の記憶装置のテスト (2,382)

国際特許分類[G11C29/00]の下位に属する分類

故障した周辺回路の検出またはその位置の特定 (62)

故障したメモリ素子の検出またはその位置の特定 (1,973)

メモリ内容の保護;メモリ内容の誤りの検出

試験回路を設計するための装置,例.テスト容易化設計ツール

静的記憶のための外部試験装置,例.自動検査装置;そのインターフェース (267)

国際特許分類[G11C29/00]に分類される特許

51 - 60 / 80

半導体記憶装置

【課題】連続して発生するAF Hit信号の切り替わりにギャップが無い状態を生成するためのテスト時間の短縮化を図ること。

【解決手段】第1および第2のアンチヒューズセットは、イネーブルヒューズ回路と、バンクアドレスおよびXアドレスがヒットでLowを出力するバンク/Xアドレス一致判定回路と、バンクアドレスがヒットでLowを出力するバンクアドレス一致判定回路と、YアドレスがヒットでLowを出力するYアドレス一致判定回路と、テスト信号の反転信号と、バンク/Xアドレス一致判定回路の出力信号と、のANDを演算するAND回路と、イネーブルヒューズ回路の出力信号の反転信号と、AND回路の出力信号と、バンクアドレス一致判定回路の出力信号と、Yアドレス一致判定回路の出力信号と、のNORを演算するNOR回路と、を有する。

(もっと読む)

半導体記憶装置

【課題】2個の隣接する列ブロックのいずれにも欠陥がある場合でも、これらの列ブロックの救済が可能な半導体記憶装置を提供する。

【解決手段】データ線シフト回路58は、偶数番目の正規ブロックに欠陥がある場合に、偶数番目の正規ブロックおよび偶数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、偶数番目の内部正規データ線NIOXおよび偶数番目の内部スペアデータ線SIOXと偶数番目の外部データ線EIOXとの接続を行ない、奇数番目の正規ブロックに欠陥がある場合に、奇数番目の正規ブロックおよび奇数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、奇数番目の内部正規データ線NIOXおよび奇数番目の内部スペアデータ線SIOXと奇数番目の外部データ線EIOXとの接続を行なう。

(もっと読む)

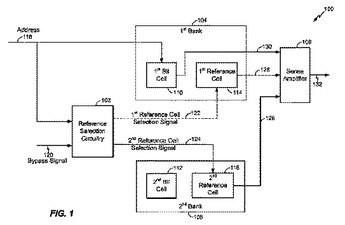

参照セルを選択するためのシステムおよび方法

参照セルを選択するためのシステムおよび方法が開示される。ある特定の実施形態では、メモリの第1のバンクの中のビットセルに対応するアドレスを受け取るステップを含む、方法が開示される。方法はまた、第1のバンクの第1の参照セルがバイパスされるものとして示されることに応答して、メモリの第2のバンクの第2の参照セルにアクセスするステップも含む。  (もっと読む)

(もっと読む)

DRAMエラー訂正用のビット交換技術

【課題】 不良セルを交換セルに効率的にリマッピングすること。

【解決手段】 開示した実施形態は、ダイナミックメモリセルセットおよび交換ダイナミックメモリセルセットを含むダイナミックメモリ装置を提供する。交換ダイナミックメモリセルセットには、ダイナミックメモリセルセットにおける所定の不良セル用の交換データビットを含むデータセルと、不良セルを識別するアドレスビットを含むアドレスセルと、が含まれ、各データセルは、ダイナミックメモリセルセットにおける関連する不良セルを識別するアドレスセルのグループに関連付けられる。ダイナミックメモリ装置にはまた、リマッピング回路が含まれ、このリマッピング回路は、ダイナミックメモリセルセットにおける不良セルを、交換セルのセットにおける関連する交換セルにリマッピングする。

(もっと読む)

エラーを管理するための書き込み後読み出しおよび適応再書き込みを伴う不揮発性メモリおよび方法

不揮発性メモリにおけるデータエラーは、使用されると、またセル当たりに格納されるビットの密度が高くなると、必然的に増える。メモリは、より少数のエラーで動作するけれども記憶密度がより低い第1の部分と、より高い密度で動作するけれども記憶装置の堅固性がより低い第2の部分とを有するように構成される。入力データは、第2の部分にコピーされる前に第1の部分に書き込まれステージされる。エラー管理は、コピーされたデータの品質を、過多なエラービットがあるかないかを検査する。そのコピーすること、また検査することは、所定の品質が満たされるかあるいは反復の回数が所定の限度を超えるまで、第2の部分の別の位置で反復される。エラー管理は、メモリが新しくてエラーがほとんどあるいは全くない時には開始されないが、メモリが、それ自体が経験した消去/プログラムのサイクルの数により判定される所定量まで古くなった後に、開始される。  (もっと読む)

(もっと読む)

抵抗変化メモリのテスト装置、方法および抵抗変化メモリ装置

【課題】任意のテストサイクルにおけるサイクル時間を局所的に自由に調整する。

【解決手段】一定周期で信号変化する第1のライトイネーブル信号と、ワード線の活性化/非活性化制御とビット線の活性化/非活性化制御との間の限界時間の確認を行う時間部分で信号変化する第2のライトイネーブル信号とを入力し、入力された第1および第2のライトイネーブル信号に基づいて、複数のコア制御信号が信号変化する時間間隔が局所的に第1のライトイネーブル信号の周期よりも短い複数のコア制御信号を発生し、発生された複数のコア制御信号を用いて抵抗変化メモリの動作確認を行う。

(もっと読む)

半導体集積回路およびその検査方法

【課題】機密データを格納するメモリに対して、メモリに格納されるデータの機密性を確保しつつ、メモリ不良時の解析を容易にする半導体集積回路およびその検査方法を提供する。

【解決手段】機密データを格納するメモリ100と、メモリのWrite/Read動作させる制御回路104と、メモリからの出力データを圧縮するデータ圧縮回路108と、データ圧縮回路から出力される信号を外部モニターできる外部端子110と、メモリからの出力データと正常時に出力されるデータとの比較を行う期待値比較回路109と、期待値比較回路から出力される比較結果の信号を外部モニターできる外部端子111と、メモリからの出力データをテストパスから取り込むことができるテスト回路101bとで構成される。

(もっと読む)

半導体装置

【課題】 不揮発性半導体メモリを搭載した半導体装置の試験時間を短縮する。

【解決手段】 遮断回路(16)は、電圧供給回路(11)から不揮発性のメモリブロック(14)への電源電圧(VDD1)の供給を遮断する。放電回路(18)は、安定化キャパシタ(17)に蓄積された電荷を放電する。自己試験回路(15)は、メモリブロックのデータ保持に関する試験の際に、メモリブロックに所定データを書き込んだ後に遮断回路に動作開始を指示し、遮断回路への動作開始の指示から所定時間が経過した後にメモリブロックの所定データの保持を確認するために遮断回路に動作停止を指示する。更に、自己試験回路は、メモリブロックのデータ保持に関する試験の際に、遮断回路への動作開始の指示に合わせて放電回路に動作開始を指示し、遮断回路への動作停止の指示に合わせて放電回路に動作停止を指示する。

(もっと読む)

連想メモリおよびそのテスト方法

【課題】テストを簡便に行うことができる連想メモリおよびそのテスト方法を提供する。

【解決手段】入力された参照情報を記憶するメモリセルの出力と入力された検索情報とを比較する比較器を備えた比較器付きメモリセル1〜8が行および列方向に配列され、行方向の比較器付きメモリセルの比較器から出力される信号の論理積演算を行って出力するAND回路17〜20を行毎に備えた連想メモリであって、AND回路から出力される一致フラグを行毎に記憶するスキャンセル44〜47が列方向に直列に接続されたスキャンレジスタとを備える。

(もっと読む)

CAM装置及びCAM装置の救済方法

【課題】低電力消費化が図れ、また製造歩留まりの向上が図れるCAM装置を得ること。

【解決手段】分割したサブアレイ毎に、3値メモリと一致比較回路とサーチライン活性化制御回路とを設け、まず、分割した複数のサブアレイを任意に指定できる第2の検索要求と3値メモリの保持値との一致比較によって任意のサブアレイを選択し、その選択されたサブアレイの一致比較回路において第1の検索要求によるデータ列をサーチライン活性化制御回路に与えるようにしたので、簡単なハードウェアの追加によって低消費電力化が図れる。このとき、分割した複数のサブアレイを検索対象となる場合とならない場合とに自在に制御することができるので、経路検索機器に用いる場合に、アプリケーションの要求する自由度に追従する分割が行えるようになる。

(もっと読む)

51 - 60 / 80

[ Back to top ]