国際特許分類[H01L21/283]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571) | 電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/283]の下位に属する分類

気体または蒸気からの析出,例.凝結 (1,528)

液体からの析出,例.電解液からの析出 (1,357)

国際特許分類[H01L21/283]に分類される特許

461 - 470 / 487

半導体装置の製造方法

【課題】 High−k膜を用いてヒステリシスの増加の小さい半導体装置の製造方法を提供する。

【解決手段】 シリコン基板上に第1の絶縁膜および第2の絶縁膜を形成した後、0.2体積%以上の濃度の酸素を含む雰囲気中で熱処理を行う。第2の絶縁膜は、高誘電率絶縁膜であるとともに、第1の絶縁膜と第2の絶縁膜との界面で酸化還元反応が起こるのを抑制できる量の酸素を透過する膜厚で形成される。第2の絶縁膜は、膜厚3.0nm以下、好ましくは2.4nm以下のHfAlOx膜とすることができる。

(もっと読む)

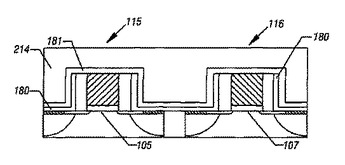

置換金属ゲート形成のための半導体構造の平坦化

窒化物および充填層を含む犠牲ゲート構造は、金属ゲート電極と置換される。金属ゲート電極は、充填層で被覆された窒化物層で再度被覆される。窒化物および充填層の置換によって、歪みが再導入され、エッチング停止層が提供される。  (もっと読む)

(もっと読む)

ウェハ接合によって製造される半導体−誘電体−半導体デバイス構造体

【課題】 デバイス性能を犠牲にすることなく様々なゲート材料の使用を可能にする、半導体基板上に少なくとも部分的にゲート・スタックを作るための技術を提供する。

【解決手段】 高k誘電材料を含む少なくとも1つの構造体のウェハ接合を利用して、半導体電子デバイスのためのゲート・スタックを形成する方法が提供される。本発明の方法は、まず、それぞれが主面を有する第1及び第2の構造体を選択するステップを含む。本発明によれば、第1及び第2の構造体の少なくとも一方又は両方は、少なくとも高k誘電材料を含む。次に、第1及び第2の構造体の主面同士を接合して、ゲート・スタックの高k誘電材料を少なくとも含む接合構造体を形成する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】 高い信頼性を有する半導体素子を提供する。

【解決手段】

ドリフト領域11の表面領域にはベース領域13が形成され、ベース領域13の表面領域にはソース電極14が形成され、ドリフト領域11上には、酸化膜20、ゲート電極30、及び、層間絶縁膜40が形成されている。ソース領域14、酸化膜20、及び、層間絶縁膜40には、層間絶縁膜40上のソース電極50とベース領域13及びソース領域14とを接続するためのソース開孔50aが形成されている。酸化膜20は、ゲート電極30下の厚い第1酸化膜と、ソース開孔50aの外縁から延伸する薄い第2酸化膜と、第1酸化膜と第2酸化膜との間に配置され、第1酸化膜と第2酸化膜との中間の厚さを有する第3酸化膜と、から構成される。これにより、酸化膜20の厚さは、ソース開孔50aの外縁からゲート電極30に向かって階段状に増加する。

(もっと読む)

異なるゲート誘電体を用いたNMOS及びPMOSトランジスタを具備する相補型金属酸化物半導体集積回路

相異なるゲート誘電体を有するNMOSトランジスタ及びPMOSトランジスタを具備する相補型金属酸化物半導体集積回路が形成され得る。相異なるゲート誘電体は、例えば、置換プロセスによって形成され得る。ゲート誘電体は、幾つか例を挙げると、材料、厚さ又は形成技術において異なる。

(もっと読む)

(もっと読む)

ゲート酸化膜形成法

【課題】厚さを異にする複数のゲート酸化膜を1回の熱酸化処理により形成する際に厚いゲート酸化を効率的に行なう。

【解決手段】半導体基板10の一方の主表面にフィールド絶縁膜12を形成した後、酸化膜14a,14bとして犠牲酸化膜又はゲート酸化膜を形成する。素子孔12a内にレジスト層16をマスクとし且つ酸化膜14aを介してアルゴン(又はフッ素)イオンを1又は複数回の注入処理により注入してイオン注入層18を形成する。酸化膜14a,14bを犠牲酸化膜としたときはレジスト層16及び酸化膜14a,14bの除去後に素子孔12a,12b内にゲート酸化膜を形成する。酸化膜14a,14bをゲート酸化膜としたときはレジスト層16の除去後に酸化膜14a,14bをエッチングで薄くしてから酸化膜14a,14bを厚くする。イオン注入層18を形成したことで14b対応のゲート酸化膜より14a対応のゲート酸化膜が厚くなる。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】 本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】 半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 遷移金属化合物膜を含むゲート絶縁膜を有する半導体装置のリーク電流及び閾値電圧のシフトを抑制する。

【解決手段】 半導体装置は、高誘電率材料である遷移金属化合物膜からなるゲート絶縁膜104と、n型又はp型のドーパントを含み且つ多結晶シリコン又はシリコン化合物からなるゲート電極105とを備え、ゲート絶縁膜104に含まれる炭素及びハロゲン元素の総量が0.1atomic%以下となっている。このような純度の膜は、遷移金属をターゲットとするスパッタ法によって成膜することによって実現でき、特に、純度が99.999atomic%以上の遷移金属をターゲットとして用いると確実に実現できる。

(もっと読む)

ナノクラスタ電荷蓄積デバイスの形成方法

一実施形態では、ナノクラスタ電荷蓄積デバイスを形成する方法が提供される。半導体装置(10)の第1の領域(26および30)が1つまたは複数の非電荷蓄積デバイスを配置するために特定される。この半導体装置の第2の領域(28)が1つまたは複数の電荷蓄積デバイスを配置するために特定される。この1つまたは複数の非電荷蓄積デバイスのゲート絶縁体として使用されるゲート酸化物(22)がこの半導体装置の第1の領域(26および30)中に形成され、引き続きナノクラスタ電荷蓄積層がこの半導体装置の第2の領域(28)中に形成される。  (もっと読む)

(もっと読む)

ドープ窒化膜、ドープ酸化膜、およびその他のドープ膜

【課題】一般に、半導体デバイスの製造に使用される被膜、特に窒化被膜および酸化被膜を提供すること。

【解決手段】窒化シリコン、酸化シリコン、酸窒化シリコン、または炭化シリコン被膜の形成中、少なくとも1つの非シリコン前駆体(ゲルマニウム前駆体や炭素前駆体など)を添加することによって、堆積速度が改善され、または被膜の応力を調整するなどこの被膜の特性を調整することが可能になり、あるいはその両方が可能になる。また、ドープ型酸化シリコンまたはドープ型窒化シリコンまたはその他のドープ型構造では、ドーパントが存在することを利用して、このドーパントに関連する信号(目印)をエッチング・ストップとして測定することができ、またはその他の場合にはエッチング中の制御を実現することができる。

(もっと読む)

461 - 470 / 487

[ Back to top ]