国際特許分類[H01L21/76]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 構成部品間の分離領域の形成 (3,154)

国際特許分類[H01L21/76]の下位に属する分類

国際特許分類[H01L21/76]に分類される特許

91 - 100 / 2,201

半導体装置およびその製造方法

【課題】 JFET等のような低ノイズ特性が要求される半導体装置において、発生するノイズを低減すると共に、半導体装置を小さい寸法で製造する。

【解決手段】 半導体装置は、半導体層(101)に形成された素子分離(102)、第1導電型の不純物層(104)、第1導電型のソース領域(106)、第1導電型のドレイン領域(107)、第2導電型のゲート領域(105)、絶縁膜(108)を介して形成された制御電極(109)を備える。制御電極(109)に電圧を印加すると、半導体装置の動作中に制御電極(109)の下の不純物層(104)に空乏層を発生させることができ、キャリアは絶縁膜(108)と不純物層(104)の界面から離れて流れる。

(もっと読む)

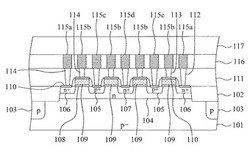

半導体装置およびその製造方法

【課題】ウェル給電領域の面積を縮小して、半導体装置の微細化を行う。素子形成領域間のウェル電位のばらつきを抑制する。分離部の幅を細くする。

【解決手段】半導体装置は、半導体基板の表面に形成され、底部がウェル領域内に位置する溝状の分離部を有する。分離部は、ウェル領域と電気的に接続された導体配線と、底部に導体配線を埋め込む絶縁膜とを有する。分離部に囲まれるようにして区画されたウェル領域の一部は素子形成領域を形成し、素子形成領域には半導体素子が配置される。

(もっと読む)

半導体基板または半導体装置の製造方法

【課題】平板状空洞を形成する際におけるホール半径Rと、ホールとホールの最短距離Sのプロセスマージンを広げ、信頼性の高い半導体装置の製造方法を提供すること。

【解決手段】半導体基板1の表面にホール4を複数形成し、非酸化性雰囲気のアニール処理により、該半導体基板1の表面を半導体の表面マイグレーションを利用して平坦化し、基板内部に平板状空洞6を形成する際に、前記ホール4の開口部が閉じる前に半導体のソースガスを供給する。

(もっと読む)

半導体装置及びその製造方法

【課題】製造プロセスが複雑になるといったことを防ぎつつ、n型及びp型MOSトランジスタについて両方の性能を向上させた半導体装置を提供する。

【解決手段】半導体基板1の面内に、n型MOSトランジスタと、p型MOSトランジスタとを備える半導体装置であって、n型MOS型トランジスタが形成される第1の拡散層2aの間を絶縁分離する第1の絶縁層3aと、p型MOS型トランジスタが形成される第2の拡散層2cの間を絶縁分離する第2の絶縁層3bとを備え、第1の絶縁層3aは、半導体基板1の表層に形成された第1の溝部4aに、シリコン窒化膜5と、このシリコン窒化膜5の上にシリコン酸化膜6とを埋め込むことによって形成され、第2の絶縁層3bは、半導体基板1の表層に第1の溝部4aよりも幅広となるように形成された第2の溝部4bに、シリコン酸化膜6を埋め込むことによって形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 層間絶縁膜をCMP法で研磨、平坦化する際、MOS型トランジスタのチャネル領域に応力を与えるためにゲート電極を覆うように形成される応力ライナー膜が研磨されて、トランジスタ特性の変動やバラツキが発生しないようにする。

【解決手段】 第1活性領域(例えばPチャネルトランジスタ形成領域)上のゲート電極(シリコン膜14と金属シリサイド膜15との積層膜)上には第1応力膜(圧縮応力ライナー膜)16のみを形成し、第2活性領域(例えばNチャネルトランジスタ領域)上のゲート電極上には第2応力膜(引っ張り応力ライナー膜)18のみを形成する。一方、素子分離10上のゲート電極上には第1および第2応力膜16、18の積層膜を形成する。層間絶縁膜20のCMP法による研磨は、素子分離10上の第2応力膜18の露出後に停止する。

(もっと読む)

プラズマ処理方法、及び素子分離方法

【課題】 STIプロセスにおけるシリコンのトレンチの内壁面に沿って、酸素の拡散に対するバリア性を有する数nm程度の厚みの薄膜を形成する方法を提供する。

【解決手段】 プラズマ処理装置100では、平面アンテナ31からマイクロ波透過板28を経て処理容器1内に放射されたマイクロ波により、処理容器1内で電磁界が形成され、ArガスおよびN2ガスがそれぞれプラズマ化する。プラズマ中の活性種の作用によりウエハWのトレンチの内壁面が極薄く窒化されることにより、緻密なライナーSiN膜が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板を貫通する貫通電極の周囲に形成される環状の絶縁分離部において、絶縁分離部を構成する酸化膜の応力により絶縁分離部周囲の半導体基板が変形する。

【解決手段】絶縁分離部の基板側に深さ方向に圧縮応力を与える第1の膜4を形成し、第1の膜4上に深さ方向に引張応力を与える第2の膜6膜を形成し、その際、第1及び第2の膜の膜厚を圧縮応力と引張応力とがほぼ釣り合うように調整する。

(もっと読む)

プラズマ窒化処理方法

【課題】低温ALD法で形成された窒化珪素膜のエッチング耐性を向上させる。

【解決手段】プラズマ窒化処理方法は、上部に開口を有する処理容器1と、ウエハWを載置する載置台2と、処理容器1の開口を塞ぐとともにマイクロ波を透過させるマイクロ波透過板28と、処理容器1内にマイクロ波を導入するための複数のスロットを有する平面アンテナ31と、を備えたプラズマ処理装置100を用いる。処理容器1内で、窒素含有ガスと希ガスとを含む処理ガスのプラズマを生成させて、ウエハW上の窒化珪素膜をプラズマ窒化処理する。窒化珪素膜は、ALD法により400℃以下の成膜温度で成膜された窒化珪素膜であり、プラズマ窒化処理は、ALD法における成膜温度を上限とする処理温度で行う。

(もっと読む)

半導体装置

【課題】安定したボディ固定動作と共に、高集積化、低寄生容量化や配線容量の低減化を図ることができる、SOI基板上に形成される半導体装置を得る。

【解決手段】ソース領域1,ドレイン領域2及びゲート電極3で形成されるMOSトランジスタにおいて、ゲート一端領域及びゲート他端領域に部分分離領域11a及び11bが形成され、部分分離領域11aに隣接してタップ領域21aが形成され、部分分離領域11bに隣接してタップ領域21bが形成される。部分分離領域11a,11b、タップ領域21a,21b及び活性領域1,2の周辺領域は全て完全分離領域10が形成される。

(もっと読む)

半導体の製造方法及び半導体装置

【課題】複雑な工程を経ることなく、通常の半導体製造装置を使用して、低コストで、半導体装置の、低電圧動作、高集積性を実現する。

【解決手段】次の工程(1)〜(5)で半導体装置を製造する。(1)シリコン結晶製の半導体支持基板の表面を洗浄し、酸化被膜を除去して、結晶面を露出させる工程、(2)該結晶面上に高誘電率非晶質薄膜を低温で堆積する工程、(3)該高誘電率非晶質薄膜の結晶化開始温度よりも低いプレアニール温度で該高誘電率非晶質薄膜をプレアニールする工程、(4)該半導体支持基板を選択的に急速加熱することにより該高誘電率非晶質薄膜内部に基板界面から該薄膜表面方向に向けて温度が低くなる急峻な温度勾配を形成することにより該高誘電率非晶質薄膜を結晶化して、エピタキシャル薄膜を形成する工程、(5)該エピタキシャル薄膜の上面に半導体結晶の配向膜を形成する工程を有する。

(もっと読む)

91 - 100 / 2,201

[ Back to top ]