国際特許分類[H01L21/76]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 構成部品間の分離領域の形成 (3,154)

国際特許分類[H01L21/76]の下位に属する分類

国際特許分類[H01L21/76]に分類される特許

111 - 120 / 2,201

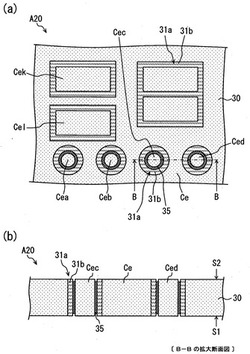

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】基板を貫通するトレンチによって複数の部分領域に分割されてなる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法であって、部分領域の側壁に導電層を形成するメリットだけを享受して、該導電層の形成に伴う悪影響を排除することのできる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ce,Cea〜Ced,Cek,Celに分割され、前記複数の部分領域のうち、一部の部分領域Cea〜Cedの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、トレンチ31aに絶縁体31bが埋め込まれてなる領域分割基板A20とする。

(もっと読む)

半導体装置

【課題】基板を介したクロストークを抑制でき、放熱性が高い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置1は、半導体基板10を備える。前記半導体基板の内部には空洞11が形成されている。また、前記半導体基板の内部には、前記空洞を前記半導体基板の上面に連通させる連通孔12も形成されている。前記半導体装置は、さらに、前記空洞及び前記連通孔の内面上に設けられた絶縁膜13と、前記空洞及び前記連通孔の内部に埋め込まれ、熱伝導率が前記絶縁膜の熱伝導率よりも高い伝熱部材14と、前記半導体基板における前記空洞の直上域に形成された素子21,22と、を備える。

(もっと読む)

半導体装置

【課題】より確実に画素間クロストークを抑制することが可能な、固体撮像素子を備える半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に配置された第1導電型の不純物層DPWと、不純物層DPW上に、第1導電型の不純物領域と第2導電型の不純物領域とが互いに接合する構成を含む光電変換素子と、光電変換素子を含む単位画素を構成し、光電変換素子と電気的に接続されるトランジスタM1〜M4とを備えている。平面視において光電変換素子の外周部の少なくとも一部には、内部に空隙AGが含まれ、光電変換素子と、光電変換素子に隣接する光電変換素子とを、互いに電気的に絶縁する分離絶縁層SIが配置されている。上記分離絶縁層SIは、第1導電型の不純物層DPWの最上面に接する。

(もっと読む)

超接合半導体素子

【課題】電流検出用センス素子領域を備える超接合半導体素子において、主素子領域とセンス素子領域とを電気的に分離しても耐圧の低下を抑えることができること。

【解決手段】n型基板の一方の主面の垂直に長い形状の複数のn型領域1とp型領域2が、前記主面方向に平行に交互に隣接配置してなる並列pn層100を共通のドリフト層として備え、前記一方の主面に、主ゲート電極14と主ソース電極16aを有する主素子領域7と、センスゲート電極14とセンスソース電極16bを有するセンス素子領域8とを備え、他方の主面に共通のドレイン電極を備え、前記一方の主面の主素子領域7とセンス素子領域8の間に分離領域9を有し、該分離領域9が、n型領域3中に前記並列pn層に平行および直交する方向で電気的にフローティング状態に配設される複数のp型領域4を備える超接合半導体素子30とする。

(もっと読む)

半導体装置

【課題】内蔵ダイオードを有する半導体装置において、逆回復時のサージ電圧の大きさを低減する。

【解決手段】半導体装置は、素子部とその素子部の周囲に位置する終端部とを有する半導体基板を備えている。半導体基板の素子部には、内蔵ダイオード構造を含むトランジスタ構造が形成されている。半導体基板の終端部には、トランジスタ構造がオフしたときに、インパクトイオンを発生させるインパクトイオン発生構造62が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離用ゲート電極のみのしきい値電圧を高くすることができ、素子分離用ゲート電極の底部にチャネルが形成されない半導体装置を提供する。

【解決手段】半導体基板1に形成された複数の活性領域と、これら活性領域同士を区画する素子分離領域と、活性領域内を複数の素子領域に区画する第1素子分離用トレンチ32Aと、隣接する第1素子分離用トレンチ32A間に設けられ、第1素子分離用トレンチ32Aの深さよりも浅く形成されたゲートトレンチ31Aと、絶縁膜25を介して第1素子分離用トレンチ32A内に形成された素子分離用電極32と、ゲート絶縁膜26Aを介してゲートトレンチ31A内に形成されたゲート電極31と、を具備してなり、素子分離用電極32底部に成膜されている絶縁膜25の膜厚が、ゲート電極31の底部に成膜されているゲート絶縁膜26Aの膜厚よりも厚いことを特徴とする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】隣接セル間干渉を抑制した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1メモリストリングと、ソースコンタクトと、第2メモリストリングと、シールド導電層と、を備えた不揮発性半導体記憶装置を提供する。第1メモリストリングは、第1軸に沿って並ぶ第1メモリセル及び第2メモリセルを含む。ソースコンタクトは、第1メモリストリングのソース側の端に設けられる。第2メモリストリングは、第1軸に対して直交する第2軸に沿って第1メモリセルと並ぶ第3メモリセルを含み、第1軸に沿って延在する。シールド導電層は、第1メモリストリングと第2メモリストリングとの間において第1軸に沿って延在し、ソースコンタクトと電気的に接続される。

(もっと読む)

二酸化ケイ素膜の製造方法

【課題】低収縮かつ低応力である絶縁膜を製造することができる方法の提供。

【解決手段】基板表面にポリシラザン組成物を塗布して塗膜を形成させ、引き続き前記塗膜を過酸化水素雰囲気下、50〜200℃で加熱することを含んでなることを特徴とする、二酸化ケイ素膜の製造方法。この二酸化ケイ素膜の製造方法によって各種絶縁膜などのアイソレーション構造を形成させることができる。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】シリコン層又はシリコン基板に補償ドープのために不純物を注入する必要がなく、安定的に高調波歪を低減する。

【解決手段】第1絶縁層20は、シリコン基板10上に形成されており、当該シリコン基板10に接している。また、配線40は、第1絶縁層20上に形成されている。ここで、第1絶縁層20下の不純物濃度は、2.0×1014cm−3以下である。

(もっと読む)

111 - 120 / 2,201

[ Back to top ]