国際特許分類[H01L21/76]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 構成部品間の分離領域の形成 (3,154)

国際特許分類[H01L21/76]の下位に属する分類

国際特許分類[H01L21/76]に分類される特許

141 - 150 / 2,201

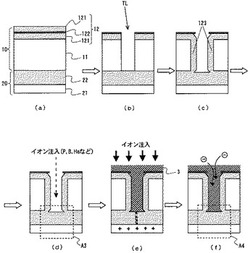

SOIウェハの製造方法

【課題】SOIウェハの支持基板ウェハの帯電を除去することのできるSOIウェハの製造方法を提供する。

【解決手段】活性層基板10と支持基板20との貼り合わせ面に酸化膜22を形成する酸化膜形成工程と、活性層基板10と支持基板20とを貼り合わせる貼り合わせ工程と、支持基板20に向けて活性層基板10に酸化膜22に達するまでのトレンチを形成するトレンチ形成工程と、トレンチから酸化膜22に向けて予め定められたイオンを注入するイオン注入工程と、トレンチ内部をポリシリコン3で充填する充填工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して貼り合わせられ、島状に絶縁分離されたGe層8(第2の半導体層)が設けられ、このGe層8に高濃度のソースドレイン領域(14、15)が形成されたPチャネルのMISFETと、Si基板1上にシリコン窒化膜2及び一部に空孔5を有するシリコン酸化膜3を介して、空孔5直上の歪みSi層7を挟み、左右にSiGe層6を有する構造からなるエピタキシャル半導体層(第1の半導体層)が島状に絶縁分離されて設けられ、歪みSi層7には概略チャネル領域が形成され、SiGe層6には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成されたNチャネルのMISFETとから構成したCMOS。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数を削減して生産性を向上できる構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体層1にトレンチ20を形成する工程と、トレンチ2の内壁およびトレンチ2外の表面を覆うように半導体層1上に絶縁膜3を形成する工程と、トレンチ2を埋め尽くし、トレンチ2外の絶縁膜3上に堆積されるように導電性のポリシリコン膜4を形成する工程と、トレンチ2内、およびトレンチ2外の絶縁膜3上の所定領域にポリシリコン膜4が残るように、当該ポリシリコン膜4を選択的に除去するポリシリコンエッチング工程とを含む。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】信頼性の高いLocalSOI構造を有する基板を低コストで作製する。

【解決手段】第1の半導体からなる基板10上に、結晶成長により第2の半導体からなる層及び前記第1の半導体からなる層12を順次形成する半導体層形成工程と、前記第2の半導体からなる層をエッチングにより除去し開口領域13を形成する開口領域形成工程と、前記開口領域に、窒化物膜、炭化物膜又は酸化物膜を含む材料により形成される酸化遅延膜14を前記開口領域の入口における膜厚が所定の膜厚となるように成膜する酸化遅延膜成膜工程と、前記第1の半導体からなる基板及び前記第1の半導体からなる層の前記第1の半導体の一部を熱酸化することにより、前記開口領域に熱酸化膜15を形成する熱酸化工程とを有することを特徴とする、Local SOI半導体基板の製造方法。

(もっと読む)

トレンチの埋め込み方法および成膜装置

【課題】 トレンチの微細化がさらに進展しても、トレンチの内部に、膨張可能な膜及び酸化障壁となる膜を形成することが可能なトレンチの埋め込み方法を提供すること。

【解決手段】 トレンチ内部に酸化障壁膜の形成工程(ステップ3)、酸化障壁膜上に膨張可能な膜の形成工程(ステップ4)、焼成することで収縮する埋め込み材でトレンチを埋め込む工程(ステップ5)、埋め込み材の焼成工程(ステップ6)と、を含み、ステップ3の工程が、アミノシラン系ガスを供給して、トレンチの内部に第1のシード層を形成する工程(ステップ31)、第1のシード層上に窒化シリコン膜を形成する工程(ステップ32)と、を含み、ステップ4の工程が、アミノシラン系ガスを供給して、窒化シリコン膜上に第2のシード層を形成する工程(ステップ41)と、第2のシード層上にシリコン膜を形成する工程(ステップ42)と、を含む。

(もっと読む)

基板処理装置、及び成膜システム

【課題】1つの実施形態は、例えば、CVD装置による成膜処理に対する新規な前処理を行うことができる基板処理装置及び成膜システムを提供することを目的とする。

【解決手段】1つの実施形態によれば、CVD装置による成膜処理を行う基板の前処理を行なうための基板処理装置であって、前記基板を保持する基板ステージが配された基板処理室と、前記基板処理室内で前記基板ステージを介して前記基板を加熱する加熱部と、前記基板処理室内で、前記加熱部により加熱された前記基板の表面を酸化する酸化処理部と、前記基板処理室内で、前記酸化処理部により酸化された前記基板の表面に有機溶剤を塗布する塗布処理部とを備えたことを特徴とする基板処理装置が提供される。

(もっと読む)

半導体装置

【課題】逆耐圧を高くしてもオン抵抗が高くなることのない半導体装置を提供する。

【解決手段】n型半導体層116と、n+型半導体層116よりも低濃度のn型不純物を含有するn型のドリフト層112と、ドリフト層112の表面に形成した、拡散深さが深いボディ部分118aと、拡散深さが浅いチャネル部分118bとからなるp型のボディ領域118と、ボディ領域118の表面に形成したn+型のソース領域120と、チャネル部分118bの上にゲート絶縁層122を介して形成したゲート電極124とを備える半導体装置であって、平面的に見てボディ領域118と重ならない領域に位置するドリフト層112には、ドリフト層112よりも高濃度のn型不純物を含有するn型の低抵抗領域144aがn+型半導体層116と接するように形成されている半導体装置100。

(もっと読む)

素子間分離層の形成方法

【課題】半導体基板上に形成された絶縁膜の研磨工程における制御性を向上させ、優れた素子間分離性能を有する素子間分離層を形成する方法を提供する。

【解決手段】半導体基板の表面上にパッド酸化膜及び窒化膜を順次形成する工程と、パッド酸化膜及び窒化膜を貫通し、半導体基板内部に到達するトレンチを形成する工程と、トレンチを充填し且つ窒化膜を覆うように埋め込み酸化膜を形成する工程と、窒化膜上に埋め込み酸化膜が残存するように第1の研磨材を用いて埋め込み酸化膜を研磨する工程と、第1の研磨材の窒化膜に対する埋め込み酸化膜の研磨選択比よりも大なる研磨選択比を備える第2研磨材を用いて埋め込み酸化膜を研磨し、窒化膜を露出させるとともに窒化膜及び埋め込み酸化膜の露出面を平坦化する工程と、を有すること。

(もっと読む)

半導体装置の製造方法

【課題】素子分離領域に用いる微細化したトレンチを、ボイドを発生させることなく絶縁膜で埋設する。これにより、素子分離領域を介して隣接して配置する素子間の短絡を防止し、製造歩留まりの低下を抑制する。

【解決手段】半導体装置の製造方法は、半導体基板内のトレンチ内に、内部にボイドを有する第1絶縁膜を形成する。この後、エッチングにより、トレンチ内に第1絶縁膜の一部が残留すると共にボイドが露出するように第1絶縁膜を除去する。次に、ALD法により、ボイド内及びトレンチの露出した内壁上に第2絶縁膜を成膜した後、エッチングステップとデポジションステップを有するHDP−CVD法のサイクルを1サイクル以上、行うことにより、素子分離領域を形成する。

(もっと読む)

半導体装置の製造方法

【課題】注入した不純物の拡散を抑制しつつ結晶欠陥を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、リンまたはボロンを分子状イオンの形態で含有する第1の不純物80と、リンまたはボロンよりも注入量が少ない炭素、フッ素または窒素を分子状イオンの形態で含有する、もしくは、リンまたはボロンよりも注入量が少ない炭素を原子イオンの形態で含有する第2の不純物81と、を半導体層1に注入して不純物注入層9を形成する工程を含む。

(もっと読む)

141 - 150 / 2,201

[ Back to top ]