国際特許分類[H01L21/822]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844)

国際特許分類[H01L21/822]の下位に属する分類

バイポーラ技術 (534)

電界効果技術 (17,660)

バイポーラ技術と電界効果技術の組み合わせ (497)

国際特許分類[H01L21/822]に分類される特許

31 - 40 / 9,153

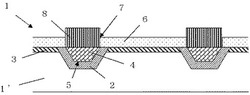

半導体基板の評価方法および評価用半導体基板

【課題】例えばCCD、CMOSセンサ等の高歩留まりが要求される製品に使用される高品質ウェーハに関して、接合リーク電流特性を高精度で評価することが可能な半導体基板の評価方法および評価用半導体基板を提供する。

【解決手段】評価する半導体基板1に、複数のPN接合5と、該複数のPN接合5同士を分離する分離酸化膜6と、該分離酸化膜6の下に位置するチャネルストップ層3とを形成してから、前記複数のPN接合5における接合リーク電流を測定して評価を行う半導体基板の評価方法。

(もっと読む)

リレーデバイスを有するメモリ要素

【課題】メモリ要素有する集積回路を提供すること。

【解決手段】上記集積回路は、基板において形成された回路網と、回路網の上における複数の機械的リレーメモリ回路とを含む。集積回路は、回路網と複数の機械的リレーメモリ回路との間に配置された誘電スタックをさらに含む。誘電スタックは、複数の金属ルーティング層およびビア層を含む。回路網は、相補型金属酸化物半導体回路網を含む。回路網は、複数の機械的リレーメモリ回路に対する制御信号を生成するように動作可能である。

(もっと読む)

半導体装置

【課題】電磁適合性(EMC)の問題を改善することができる半導体装置を提供する。

【解決手段】第1主面と第2主面とを有する半導体基板10と、第1主面上に形成され、入射光を電気信号に変換するセンサ部31と、第1主面上に形成されたロジック回路12と、センサ部31及びロジック回路12上に形成され、電磁波を遮断するシールド層14と、第2主面上に配置されたカラーフィルタ37と、カラーフィルタ37上に配置されたマイクロフィルタ38とを有する。

(もっと読む)

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

半導体集積回路

【課題】本発明の目的は,論理回路に電源電圧を供給するレギュレータを有する半導体集積回路において,C端子の数を削減する。

【解決手段】

半導体集積回路30は,第1,第2の出力端OTa,OTbと,外部容量C4に接続する外部接続端子CT4との間に設けられたスイッチ回路35を有し,

スイッチ回路35の一端は第1の出力端OTaに接続され,スイッチ回路35の他端は外部接続端子CT4および第2の出力端OTbに接続され,

スイッチ回路35は,第1のレギュレータA31が第1の電源電圧Vaを第1の論理回路A32に対して供給する期間はオンし,第1のレギュレータA31が第1の論理回路A32に対する電源電圧供給を停止する期間はオフする。

(もっと読む)

半導体装置

【課題】本発明は、電圧測定回路における電流損失を抑え、異常動作の場合であっても電圧測定回路が破壊されない半導体装置を提供する。

【解決手段】

本発明は、第1導通電極と、第2導通電極とを有する半導体スイッチ素子10と、半導体スイッチ素子10の第1導通電極および第2導通電極間の電圧を測定するための電圧測定回路31とを備える半導体装置101である。電圧測定回路31は、半導体スイッチ素子10と並列に接続され、半導体スイッチ素子10の導通方向に印加される電圧を所定値に制限するダイオード素子11と、ダイオード素子11に直列に接続された制御用スイッチ7と、半導体スイッチ素子10がオフ状態のときに制御用スイッチ7をオフ状態にし、半導体スイッチ素子10がオン状態のときに制御用スイッチ7をオン状態にするスイッチ制御部15とを含む。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】SETUP時間とHOLD時間のどちらも満足させるタイミングの調整が可能な技術を提供する。

【解決手段】半導体集積回路の配置配線レイアウトを決定した後に、所定の信号線を伝搬するデータのタイミング情報に基づいて、タイミング違反を有する違反データの遅延情報を抽出する。その抽出された遅延情報に基づいて、タイミング違反を解消するための追加すべき容量値を算出する。また、違反データを伝搬する配線のレイアウト配置情報に基づいて、違反データを伝搬する配線の近傍の電源容量セルを検出する。また、算出された容量値に基づいて、検出された電源容量セルを、電源容量セルとレイアウト外形・電源/GND配線配置位置が同じ調整容量セルに置き換える。そして、置き換えた調整用容量セルのゲートと違反データを伝搬する配線とを接続して再配線を実行する。

(もっと読む)

半導体装置

【課題】半導体装置の回路ブロックへの電力供給復帰時に、無駄な充放電を削減すること。

【解決手段】半導体装置は、第1電源電圧を供給する第1電源線と、第1電源電圧よりも高い第2電源電圧を供給する第2電源線と、前段回路ブロックと、前段回路ブロックの出力信号に基づいて動作する後段回路ブロックと、前段回路ブロック及び後段回路ブロックに対する第1電源電圧及び第2電源電圧の供給を制御する電力供給制御回路と、を備える。電力供給制御回路は、後段回路ブロックへの第1電源電圧の供給開始タイミングを前段回路ブロックへの第1電源電圧の供給開始タイミングよりも遅延させる。更に、電力供給制御回路は、前段回路ブロック及び後段回路ブロックに第1電源電圧が供給された後に、第2電源電圧を前段回路ブロックと後段回路ブロックの両方に供給する。

(もっと読む)

半導体可変容量素子

【課題】PN接合構造の可変容量素子は、逆電圧を印可するため、少なからぬリーク電流を生じる。リーク電流の小さい理想的な半導体可変容量素子を提供する。

【解決手段】P型半導体層1とN型半導体層2よりなる積層体と電極との間に絶縁層3を設けることにより、リーク電流の流れない半導体可変容量素子が可能となった。また、電極への逆方向バイアス電圧の印加により、低周波において、印加された逆方向バイアス電圧に比例する可変容量を生じる。

(もっと読む)

31 - 40 / 9,153

[ Back to top ]