国際特許分類[H01L21/8242]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | ダイナミックランダムアクセスメモリ構造 (2,471)

国際特許分類[H01L21/8242]に分類される特許

1,031 - 1,040 / 2,471

基板処理方法

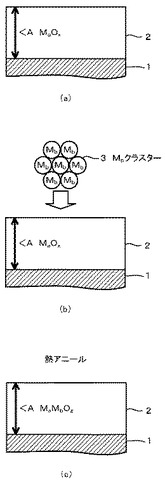

【課題】膜厚が薄い場合や導入物質の濃度が低い場合であっても、導入物質を導入することのできる基板処理方法を提供する。

【解決手段】基板1上に薄膜2を形成する工程と、薄膜2に、導入物質のガスクラスターをイオン化して加速したガスクラスターイオンビーム3を照射して薄膜中2に導入物質を導入する工程とを具備し、基板1上に導入物質が導入された薄膜2を形成する。

(もっと読む)

チタン酸ストロンチウムベースの誘電体層を有するキャパシタを備えたメモリセルの形成方法およびそれから得られるデバイス

【課題】低い等価酸化膜厚(EOT)および低い漏洩電流を有する金属−絶縁体−金属キャパシタを提供する。

【解決手段】低温原子層堆積(ALD)法を用いて、SrxTiyO3ベースの金属−絶縁体−金属(MIM)キャパシタを製造する方法が開示される。好ましくは、下部電極を形成するためにTiNが用いられる。キャパシタのSrxTiyO3誘電体層でのSr/Ti比率は、キャパシタの電気的特性を調整するために変化できる。SrxTiyO3誘電体層の誘電率および漏洩電流は、このSrxTi1−xO3誘電体層のSr含有量とともに単調に減少する。SrxTiyO3誘電体層とTiN下部電極との間の界面でのSr含有量を増加させることによって、界面の等価酸化膜厚(EOT)をさらに低減できる。

(もっと読む)

欠陥解析方法、プログラム及び電子デバイスの製造方法

【課題】測定スループットを向上させ、かつ正確な解析結果を得ることができる欠陥解析方法を得る。

【解決手段】ステップS1で、検査装置の面積縮小機能を用いて所定の工程後に所定の工程による新規欠陥の座標及び検出サイズを抽出する欠陥検出処理を行い、ステップS3で、検出されたすべての新規欠陥を有効とする識別条件で新規欠陥の有無をチップ単位に判定する。その後、ステップS5において、面積縮小機能による欠陥検査対象領域の全欠陥検査可能領域に対する面積比を求め、ステップS6において、上記面積比に基づき、推定欠陥有りチップ数を推定換算する。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、周辺回路素子領域に配置した補償容量素子により信号遅延が生じる問題があった。

【解決手段】本発明にかかる半導体装置は、メモリセルが配置される第1の領域と、機能回路が配置される第2の領域10と、第1の領域に形成されるセルコンデンサと、第2の領域10に形成される補償容量素子(36〜38)と、を備え、補償容量素子(36〜38)は、セルコンデンサと同一の下部電極36と、容量絶縁膜37と、上部電極38とからなり、機能回路のトランジスタのドレイン拡散層44、46又はゲート電極32の上方を除いて、第2の領域10の上層を覆うように形成される。

(もっと読む)

半導体装置と半導体装置の製造方法

【課題】複数層の半導体装置を製造する工程数を単層の半導体装置を製造する工程ステップ数と同一にする半導体装置と半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置は、同じ方向に延び、所定間隔をおいて平行に配される第1アクティブ領域と、第1アクティブ領域が配されるレイヤより上位レイヤに配され、第1アクティブ領域の伸張方向と同じ方向に延び、所定間隔をおいて平行に配される第2アクティブ領域と、を備え、第1アクティブ領域と第2アクティブ領域の各々は、第1又は第2アクティブ領域の両側エッジに沿って各々形成される第1及び第2不純物ドーピング領域を有する。

(もっと読む)

半導体記憶装置

【課題】ツインセル方式のDRAMは一般的なシングルセル方式のDRAMに比べて大きな面積を必要とするため、ツインセル方式のDRAMセルのさらなる微細化を図る。

【解決手段】ツインセル方式のDRAMのメモリセル内において、キャパシタ21の側面にアクセストランジスタ22を隣接させ、キャパシタ21とアクセストランジスタ22を一体化させてメモリセルを形成することにより素子間の余分な面積を省き、メモリセルを微細化することができる。

(もっと読む)

金属シリサイド形成のための方法および装置

本明細書で述べられる実施形態は、無拡散アニールプロセスを使用して金属シリサイド層を形成する方法を包含する。一実施形態では、基板上に金属シリサイド材料を形成するための方法が、提供される。その方法は、基板のシリコン含有表面を覆って金属材料を堆積させるステップと、金属材料を覆って金属窒化物材料を堆積させるステップと、金属窒化物材料を覆って金属接点材料を堆積させるステップと、基板を無拡散アニールプロセスにさらして金属シリサイド材料を形成するステップとを含む。無拡散アニールプロセスの短い時間枠は、窒素がシリコン含有界面に拡散して窒化シリコンを形成する時間を低減し、それ故に界面抵抗を最小限にする。  (もっと読む)

(もっと読む)

成膜方法および成膜装置

【課題】結晶化しており、かつリーク電流も小さいジルコニア系膜を成膜することができる成膜方法を提供すること。

【解決手段】真空保持可能な処理容器内に被処理体を挿入し、処理容器内を真空に保持した状態とし、処理容器内にジルコニウム原料と酸化剤とを交互的に複数回供給して基板上にZrO2膜を成膜する工程と、処理容器内にシリコン原料と酸化剤とを交互的に1回または複数回供給して基板上にSiO2膜を成膜する工程とを、膜中のSi濃度が1〜4atm%になるように供給回数を調整して行い、これら供給回数のZrO2膜成膜とSiO2膜成膜とを1サイクルとし、このサイクルを1以上行い所定膜厚のジルコニア系膜を成膜する。

(もっと読む)

半導体記憶装置

【課題】低消費電力、および入出力バッファの転送レートの向上を実現させると共に、製造コストの増加を抑える。

【解決手段】太い破線で囲まれるメモリセルアレイ33、ロウデコーダ30、センスアンプ32は、厚膜のトランジスタを用いる。太線で囲まれる入力バッファ11〜13、入出力バッファ26は、同じ厚膜トランジスタであって当該トランジスタよりも低い閾値電圧を有するトランジスタを用いる。クロック発生部16、コマンドデコーダ17、モードレジスタ18、制御部20、ロウアドレスバッファ&リフレッシュ回路21、カラムアドレスバッファ&バーストカウンタ22、データ制御回路23、ラッチ回路24、DLL25、カラムデコーダ31は、薄膜のトランジスタを用いる。

(もっと読む)

半導体集積回路および半導体記憶装置

【課題】チップの内部バスやチップ間を接続する外部バスにおける消費電力の低減や、データ転送速度の向上を実現する。

【解決手段】論理レベル‘H’か‘L’かその中間レベルとなる‘M’を採り得る複数本のバスDB[0]〜DB[n−1]と、データD[0]〜D[m−1]を符号化し、これに基づいて複数本のバスのそれぞれを論理レベル‘H’、‘L’、‘M’のいずれかに駆動する送信回路TXと、複数本のバスを互いにショートするバスイコライズ回路BEQを設ける。送信回路TXは、データの符号化を行う際に、論理レベル‘H’に駆動するバスの本数(k本)と論理レベル‘L’に駆動するバスの本数(k本)が同数となるような組み合わせを用いる。バスイコライズ回路BEQは、データが送信された後にショート動作を行うことで、各バスを論理レベル‘M’にプリチャージする。

(もっと読む)

1,031 - 1,040 / 2,471

[ Back to top ]