国際特許分類[H01L23/52]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 動作中の装置内の1つの構成部品から他の構成部品へ電流を導く装置 (7,814)

国際特許分類[H01L23/52]の下位に属する分類

半導体本体上に分離できないように形成された導電層及び絶縁層の多層構造からなる外部の相互接続を含むもの (2,851)

内部の相互接続を含むもの,例.クロスアンダ構造

絶縁基板の上または中に形成される複数の半導体チップ間の相互接続構造 (17)

国際特許分類[H01L23/52]に分類される特許

1,001 - 1,010 / 4,946

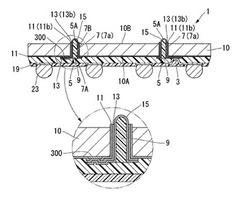

電子装置、電子装置の製造方法、電子機器

【課題】端子間の接合性に優れ高い信頼性を備えたものにするとともに、端子の狭ピッチ化も容易に対応できる電子装置、電子装置の製造方法、電子機器を提供する。

【解決手段】本発明の半導体装置1は、半導体基板10と、半導体基板10に形成された貫通孔7内に設けられるとともに半導体基板10の能動面10A側に部分的に突出する貫通電極5と、を有し、貫通電極5は、樹脂コア9と、樹脂コア9の少なくとも一部を覆う導電膜15と、を有する。

(もっと読む)

半導体パッケージ及びその製造方法

【課題】 半導体パッケージに熱が加えられた場合に、半導体装置と配線基板とを接合する接合部に生じる応力を緩和し、クラックの発生を防止できる半導体パッケージ、及び、その製造方法を提供することを課題とする。

【解決手段】 この半導体パッケージは、配線基板と、前記配線基板上に形成された半導体装置と、を有し、前記半導体装置は、半導体チップと、一方の端部が前記半導体チップの一方の面に固定され、他方の端部が前記半導体チップを貫通して、前記半導体チップの他方の面に固定された貫通電極と、を有し、前記貫通電極は、前記半導体チップに形成された空間部により、前記半導体チップの壁面と接触しないように前記半導体チップを貫通し、前記配線基板と前記半導体装置とは、前記貫通電極を介して電気的に接続されていることを要件とする。

(もっと読む)

半導体装置

【課題】窒化シリコン膜と電極パッドとの界面から水分が浸入することを抑制し、半導体装置の信頼性を向上させること。

【解決手段】半導体層2と、半導体層2上に設けられたAuからなる電極パッド10と、電極パッド10上にその端部が位置するように、半導体層2上及び電極パッド10上に設けられた窒化シリコン膜6と、電極パッド10の上面の一部及び窒化シリコン膜6の端部に接し、かつ電極パッド10の上面の他部が露出するように設けられたTi、Ta及びPtのいずれかからなる金属層14と、を具備する半導体装置。

(もっと読む)

半導体装置

【課題】外部からの電気的な干渉が十分に低減されるとともに、所望の特性を発揮する容量素子が形成される半導体装置、を提供する。

【解決手段】半導体装置は、主表面1aを含む半導体基板1と、主表面1a上に規定された容量形成領域22に形成され、所定の方向に延在する複数の配線11と、容量形成領域22の周縁に配置された配線11pに隣り合い、所定の方向に延在し、電位固定された複数の配線12と、主表面1a上に形成され、複数の配線11の各々の間と、隣り合う配線11および配線12の間とを充填する絶縁体層5とを備える。複数の配線11および12は、主表面1aに平行な平面21内においてほぼ等しい間隔を隔てて配置され、かつ所定の方向に対してほぼ直角方向に並んで配置されている。

(もっと読む)

冷却機構を含む接合型半導体構造体とその形成方法

【課題】 冷却機構を有する接合型半導体基板を形成するための構造体、設計構造体、及びその形成方法を提供すること。

【解決手段】 2つの半導体基板を備える接合型基板が提供される。各々の半導体基板は、半導体デバイスを含む。少なくとも1つの基板貫通ビアが2つの半導体基板の間に設けられ、それらの間に単一の経路を提供する。2つの半導体基板の底側は、冷却機構を含む少なくとも1つの接合材料層によって接合される。1つの実施形態において、冷却機構は冷却チャネルであり、その中を通って冷却流体が流動し、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。別の実施形態において、冷却機構は、2つの端部とそれらの間の連続した経路を備えた導電性冷却フィンである。冷却フィンはヒートシンクに接続され、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】酸素ガスを主に含有したガスでエッチングを行う必要がある金属材料を用いてピラー型電極を形成する際に、ピラー型電極のアスペクト比が高くなると製造が困難になるという課題があった。

【解決手段】層間絶縁膜上に第1〜第6の絶縁膜を積層した後、第1のフォトレジスト膜を形成する工程と、前記第1のフォトレジスト膜をマスクとして第1の溝部を形成する工程と、前記第1の溝部を充填するように電極材料を堆積する工程と、前記第4の絶縁膜上に第7〜第9の絶縁膜を形成した後、第2のフォトレジスト膜を形成する工程と、前記第2のフォトレジスト膜をマスクとして第2の溝部を形成すると共に、前記電極材料をピラー型に残存させる工程と、前記第8、前記第7、前記第4および前記第2の絶縁膜を除去して、前記電極材料からなるピラー型電極を露出する工程と、を有する半導体装置101の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】多層配線構造の半導体装置のパッケージ工程や環境試験において、膜剥れが起き難い技術を提供する。

【解決手段】絶縁層中に配線層が構成された下層配線層、前記下層配線層上に設けられた層間絶縁層、前記層間絶縁層の上に設けられた絶縁層中に配線層が構成された上層配線層、及び前記層間絶縁層に構成された前記下層配線層の配線層と前記上層配線層の配線層とを電気的に接続する為の接続層とを具備する半導体装置において、

前記層間絶縁層A7に、該層間絶縁層A7の上層および/または下層に繋がる埋設層A15が構成され、前記埋設層A15および接続層A12を有する層間絶縁層A7の平均弾性率が10GPa以上であるよう構成されてなる半導体装置。

(もっと読む)

半導体チップ

【課題】外部回路との入出力用電極パッドを周辺部に高密度に配設した半導体チップに対する電源供給時のIRドロップを抑え、かつ、特性試験にも対応できる半導体チップを提供する。

【解決手段】半導体チップ1には半導体基板主面の周辺部に複数の第1の電極パッド2、第1の電極パッド2より内側の領域に少なくとも1個の第2の電極パッド3が配設されている。第1の電極パッド2の配列間には第2の電極パッド3の数以上の間隙部が設けられている。これにより、特性試験時には間隙部を通じてプローブカードとのワイヤ接続を容易に行なうことができ、実装時には、主面に第1の電極パッド2と接続するための第1のボンディングパッド5を、反対面には第2の電極パッド3と接続するための第2のボンディングパッド8が配設された配線基板4を用いることにより、第2の電極パッド3とのワイヤ接続を通じて、回路ブロックに短い配線で電源を供給することができる。

(もっと読む)

半導体構造、半導体構造を形成する方法、および半導体デバイスを操作する方法(信号忠実度および電気的分離が強化されたSOI無線周波スイッチ)

【課題】SOI(セミコンダクタ・オン・インシュレータ)基板内の底部半導体層からの半導体デバイスについて強化された信号分離を可能とする半導体構造、これを製造する方法、およびこれを操作する方法を提供する。

【解決手段】底部半導体層10と反対の導電性タイプを有するドープ接点領域18は底部半導体層10内の埋め込み絶縁体層20の下に設ける。少なくとも1つの導電ビア構造47,77は、相互接続レベル金属ライン94から、中間工程(MOL)誘電体層80、最上部半導体層30内の浅いトレンチ分離構造33、および埋め込み絶縁体層20を通り、ドープ接点領域18まで延びる構造とする。

(もっと読む)

空隙を充填するべく低抵抗率のタングステン膜を堆積させる方法

【課題】抵抗率が低く、表面粗度が低く反射率が高いタングステンを、CVD法により基板上の間隙または凹状特徴部分に充填する方法を提供する。

【解決手段】基板に設けられた凹状部分を部分的に充填するタングステンバルクを堆積した後で、堆積されたタングステンの上部分を除去する。上部分の除去は、活性化されたフッ素種に基板を暴露することによって行われる。堆積されたタングステン粒子のうち急峻で突出している突起の頂点を選択的に除去することによって、除去処理は、凹状部分の側壁に沿ってタングステンを研磨することになる。堆積−除去のサイクルを複数回実行して、凹状部分を埋める。このようにして凹状部分が充填されると、CMPにおいてコアリング(coring)が発生しにくくなる。

(もっと読む)

1,001 - 1,010 / 4,946

[ Back to top ]