国際特許分類[H01L23/52]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 動作中の装置内の1つの構成部品から他の構成部品へ電流を導く装置 (7,814)

国際特許分類[H01L23/52]の下位に属する分類

半導体本体上に分離できないように形成された導電層及び絶縁層の多層構造からなる外部の相互接続を含むもの (2,851)

内部の相互接続を含むもの,例.クロスアンダ構造

絶縁基板の上または中に形成される複数の半導体チップ間の相互接続構造 (17)

国際特許分類[H01L23/52]に分類される特許

71 - 80 / 4,946

半導体装置及びその製造方法

【課題】本発明は、半導体素子上に形成される配線の接続性の歩留まりを向上し、支持板に半導体素子をマウントする際に高精度が要求されない半導体装置及びその製造方法を提供する。

【解決手段】半導体装置において、支持板と、支持板上に載置され、複数の第1電極が形成された回路素子面を有する半導体素子と、半導体素子の回路素子面を被覆し、複数の第1電極を露出する複数の第1開口を有する第1絶縁層と、支持板の上部と第1絶縁層が形成された半導体素子の側部とを被覆する第2絶縁層と、第1絶縁層及び第2絶縁層の上部に接して形成され、複数の第1電極と電気的に接続される配線層とを備えることを特徴とする。本発明に係る半導体装置の製造方法によれば、熱的ストレスによる支持板の反りを軽減して配線の接続性の歩留まりを向上させ、開口形成時に要求される高度な半導体素子のマウント精度が不要となる半導体装置を製造することができる。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】1つの実施形態は、例えば、検査工程における検査用パッドへのコンタクトを容易化することに適した半導体装置、及び半導体装置の製造方法を提供する。

【解決手段】1つの実施形態によれば、半導体装置は、表面に垂直な方向から見た場合にチップエリアを内側に含む半導体基板と、前記チップエリアを保護するように、前記表面上における前記チップエリアの周囲に配されたエッジシールと、前記表面上における縁部に配された複数のパッド片と、前記表面上における前記チップエリアに対して第1の方向の少なくとも片側と第2の方向の少なくとも片側とのそれぞれにおいて、前記パッド片における前記エッジシールの側の縁部を覆う絶縁膜パターンとを備える。

(もっと読む)

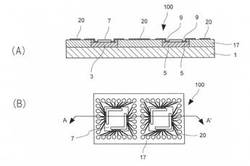

半導体装置及びそのレイアウト方法

【課題】再配線層形成工程、メタルポスト形成工程及び樹脂封止工程を経てウェハレベルで樹脂封止される半導体装置について、パッケージング工程の前後での素子の特性変動を低減させる。

【解決手段】素子が形成された半導体基板に対して、再配線層形成工程、メタルポスト形成工程及び樹脂封止工程を経てウェハレベルで樹脂封止される半導体装置について、上方から見てメタルポスト21の周縁と重なる位置に素子33,35,37を配置しないようにする。また、製造時におけるメタルポスト21に起因して生じる応力の影響を受ける、メタルポスト21の周縁から所定の範囲に素子の配置禁止領域21aを設け、配置禁止領域21aに素子33,35,37を配置しないようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、半導体装置及びその製造方法に係り、浮動構造体の支持基板への当接を他の当接を生じさせることなく実現させて、浮動構造体と支持基板との電気的接続を確保することにある。

【解決手段】半導体からなる支持基板と、支持基板上に設けられる絶縁層と、絶縁層上に設けられる活性層と、を備える半導体装置において、絶縁層の一部がエッチング除去されることにより活性層の一部に浮動構造体を形成し、その後、導電性部材を少なくとも浮動構造体を含む活性層に押し付けることで、その浮動構造体を支持基板に当接させて、浮動構造体と支持基板とを導通させる。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体集積回路のレイアウト変更方法および、レイアウト装置及び半導体集積回路

【課題】 最小限度の層の変更のみでレイアウト変更を可能にし、マスク製作費用を最小限に抑え、変更箇所以外でのタイミングを保持する。

【解決手段】 半導体集積回路のレイアウト変更方法は、半導体集積回路のレイアウト上の所定の箇所に、既存の配線層とは接続しない不接続層を含む複数層にわたるスタック構造のダミービアをあらかじめ配置し、レイアウト変更時に、所望の位置のスタック構造のダミービアに接続する新規配線を配置し、当該選択されたダミービアの前記不接続層にビア層を挿入する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】低伝導度領域ができるだけ少なくなるグラフェン配線構造が可能な半導体装置を提供する。

【解決手段】半導体装置は、触媒金属膜220と、グラフェン膜230と、コンタクトプラグ240と、調整膜250と、を備える。触媒金属膜は、基板上に形成される。グラフェン膜は、触媒金属膜上に形成される。コンタクトプラグは、グラフェン膜と接続する。調整膜は、前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に形成され、ディラック点位置をフェルミ準位に対してコンタクトプラグと接続する領域と同方向に調整する。

(もっと読む)

化合物半導体デバイス

【課題】高温にさらされても、Au配線表面に析出物が発生することを抑制できる半導体デバイスの製造方法を提供する。

【解決手段】化合物半導体基板1上の、Auからなる下部配線層3aと上部配線層3bの上部を覆って、Auより薄膜応力が小さく高融点を有する金属であるタンタルあるいはチタンからなる配線被覆層5と5’をスパッタにより形成する。

(もっと読む)

配線の形成方法及びその配線を有する表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】配線の形成方法及び配線を有する表示装置の形成方法は、基板上若しくは回路素子上に設けられた第1の金属拡散防止膜上に、金属シード層をCVD法により形成し、フォトレジストマスクを用いて選択的に無電解メッキ法、又は電解メッキ法により、金属配線層を形成し、金属シード層及び第1の金属拡散防止膜の不要領域除去と、金属シード層及び金属配線層及び第1の金属拡散防止膜の側面を含む表面を覆うように無電解メッキ法による第2の金属拡散防止膜の選択的な形成とにより配線及び電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】実施の形態の半導体装置は、シリコンを含む半導体基板10上の層間絶縁膜11に形成されたコンタクトホール12の底部14に形成され、コンタクトホール12に形成されるコンタクトプラグ21と電気的に接続するニッケルシリサイド膜18を有する。このニッケルシリサイド膜18は、ニッケルシリサイド膜18とコンタクトプラグ21の界面18aが半導体基板10と層間絶縁膜11の界面10aより高い。

(もっと読む)

71 - 80 / 4,946

[ Back to top ]