国際特許分類[H01L27/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153)

国際特許分類[H01L27/04]の下位に属する分類

複数の個々の構成部品を反復しない形で含むもの (2,326)

1種類の半導体構成部品だけを含むもの (8,288)

複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/04]に分類される特許

9,651 - 9,660 / 9,686

半導体装置

容量素子の形成方法

強誘電体メモリ

【目的】この発明は、酸化物強誘電体表面の還元反応、変質を阻止するとともに、MOSシンター工程において強誘電体薄膜と上下電極間の剥離を防止することを主要な目的とする。

【構成】半導体基板(1) と、この基板(1) 上に設けられ、下部電極(10),酸化物強誘電体薄膜(11),上部電極(12)の順次積層して構成される誘電体薄膜キャパシタ(9) と、このキャパシタ(9) 表面に被覆された、アルミニウム,シリコンもしくはチタンの窒化物薄膜を主要な構成要素とする保護膜(12)とを具備したことを特徴とする強誘電体メモリ。

(もっと読む)

単一電子トンネリング素子

【構成】第1及び第2の電極3、4と、これら第1及び第2の電極3,4に対してそれぞれ単一電子トンネル接合6を介して接続され、電子スピンの方向が揃った第3の電極5と、この第3の電極5に対して絶縁膜8を介して接続され、該第3の電極5及び絶縁膜9とともにキャパシタを構成する第4の電極10とを具備したことを特徴とする単一電子トンネリング素子。

【効果】本発明によって、電子がトンネルする際に電子のスピンの自由度に対する情報も含んだ形で、電流一電圧特性を引き出す事が可能になり、電子一個から究極の情報を取り出し、更にその特性を用いて多種類の演算を可能にする基本素子を提供することができる。

(もっと読む)

半導体装置及びその製造方法

【目的】 容量電極を有する半導体装置において、容量電極とコンタクトホールとの目合せずれを解消し、かつ容量電極の機械的強度の向上を図る。

【構成】 半導体基板101上にコンタクトホール111を介して半導体基板と電気的に導通され、かつその一部が上方に向けて筒状に形成された容量電極112と、この容量電極の上層に絶縁膜114を介して形成される対向電極115とでキャパシタを構成する半導体装置において、容量電極112の平面方向の外形状がコンタクトホール111の平面方向の外形状から一定の間隔で拡大した形状となるようにする。

(もっと読む)

半導体メモリ装置及びその製造方法

【目的】 半導体装置及びその製造方法を提供すること。

【構成】 セルアレイ領域と周辺回路領域から構成される半導体メモリ装置において、前記セルアレイ領域と周辺回路領域の間の境界領域に、前記セルアレイ領域を囲む形でその上部が除去された形のトンネルが形成される。

【効果】 従来半導体メモリ装置で問題となったセルアレイ領域と周辺回路領域の間の段差による導電層の信頼度低下を防止できるだけではなく、周辺回路領域の表面平坦化を同時に達成できる。

(もっと読む)

キャパシタの形成方法

【目的】 本発明は、スタックト型キャパシタ形成プロセスの短縮を目的とする。

【構成】 拡散層4を有する半導体基板1上に層間絶縁膜6を堆積し、この絶縁膜6上に第1のマスクパターンを形成し、このパターンを用いて前記層間絶縁膜6をエッチングして前記拡散層4上に接続孔7を形成する工程と、この接続孔7の内部及び開口部周囲に第1の導電膜8を選択的に形成する工程と、この第1の導電膜8上にキャパシタ絶縁膜9を形成する工程と、全面に第2の導電膜10を堆積する工程と、この第2の導電膜10上に第2のマスクパターンを形成し、このパターンを用いて前記第2の絶縁膜をエッチングして電極パターンを形成する工程とを有する。

(もっと読む)

高誘電率キャパシタおよびその製法

【目的】 半導体記憶装置用キャパシタで、製造プロセスの熱処理においてもキャパシタ特性が劣化しない高誘電率キャパシタを提供すると共に、熱処理の有無にかかわらず高誘電率で漏れ電流の小さいキャパシタ、その製法およびキャパシタ用誘電体膜を提供する。

【構成】 金属酸化物を主成分とする誘電体材料からなる誘電体膜4と、該誘電体膜を挟んで対向する1対の下部および上部電極3、5が設けられ、上部電極5の上に酸素欠損を防止する保護膜1が形成されている。

(もっと読む)

高電圧発生回路

【目的】電流供給能力を低下することなく、効果的にパタ−ン面積を縮小化し得る高電圧発生回路を提供する。

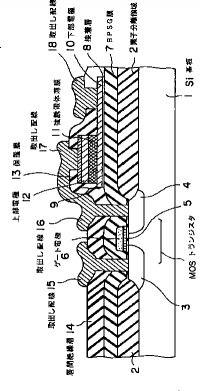

【構成】昇圧入力電圧ノードと昇圧出力電圧ノードとの間に直列に接続され、ドレイン・ゲート相互が接続された複数個のMOSトランジスタT0、T1、T2と、このトランジスタの各相互間接続ノードの奇数または偶数番目と第1または第2のクロック入力ノードとの間に各対応して接続された昇圧容量素子とを具備し、奇数番目の1個の昇圧容量と、これに接続された偶数番目の1個のトランジスタと、次段の偶数番目の1個の昇圧容量と、これに接続された奇数番目の1個のトランジスタとを含む昇圧基本回路100aが複数個縦続接続されてなる高電圧発生回路において、複数個の昇圧容量素子C11、C21、C12、C22の絶縁膜として2種類以上の厚さを有することを特徴とする。

(もっと読む)

薄膜の加工方法、容量素子の製造方法及び半導体装置の製造方法

【目的】非単結晶シリコン薄膜の表面に再現性良く微細な凹凸を形成すること。

【構成】基板31上に多結晶シリコン薄膜32からなる半導体層を設け、ゲート絶縁膜33で被覆し、ゲート電極34を形成した後ソース・ドレイン領域形成のため不純物導入を行い層間絶縁膜35を形成する。コンタクトホール開口用のフォトレジスト36を形成した後プラズマ中で絶縁膜除去処理を行い、その処理の際、自己整合的に下地の多結晶シリコン表面に微細な凹凸が形成される。その後、ソース電極37及び絵素電極38を形成することにより絵素電極部38には下地の凹凸が転写され微細な凹凸が形成され、ソース電極部37は接合面積が増大して接触抵抗が低減され薄膜トランジスタの高性能化が図れる。半導体メモリーの容量素子の電極や反射型液晶表示装置の絵素電極あるいは半導体/金属接合部の特性改善を実現できる。

(もっと読む)

9,651 - 9,660 / 9,686

[ Back to top ]