国際特許分類[H01L27/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153)

国際特許分類[H01L27/04]の下位に属する分類

複数の個々の構成部品を反復しない形で含むもの (2,326)

1種類の半導体構成部品だけを含むもの (8,288)

複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/04]に分類される特許

9,661 - 9,670 / 9,686

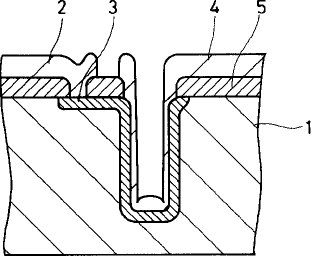

ダイオード素子

【目的】 半導体装置の静電気保護回路に用いた場合でも、その占有平面積が小さく高集積化が可能なショットキーダイオードを提供する。

【構成】 シリコン基板1にトレンチを形成し、このトレンチの内面を含む基板表面に拡散層3を形成し、Al電極4をこのトレンチの内面で拡散層3に接触させる。

(もっと読む)

薄膜装置および薄膜装置の形成方法

【目的】 電極および薄膜をICB法(イオンクラスタビーム法)を利用して形成する場合に蒸発源としてのるつぼの数を減らすことができる薄膜装置を提供する。誘電体薄膜の誘電率の低下を招くことなく電極を形成できる薄膜装置の形成方法を提供する。

【構成】 4はシリコンウェハからなる基板であり、41は基板4上に形成された白金よりなる下部電極、5はPZTの強誘電体薄膜、51はTi/TiN層で形成される上部電極である。薄膜5及び上部電極51は同一真空槽内でICB法でもって形成する。上部電極51の構成材料がTi及びTiNであり、TiはPZTの構成材料の1つであるので、電極51及び薄膜5をICB法を利用して形成する場合に蒸発源としてのるつぼを兼用し得る。薄膜5に続いて電極51を同一真空槽内で形成でき、薄膜5の表面が大気に触れることによる酸化を防止でき、誘電率の低下を防止し得る。

(もっと読む)

電子回路装置

電子回路装置

【目的】 電子回路が高密度に実装された電子回路装置において、電子回路の動作時の電流ノイズに起因して電源配線系に生じる電圧ノイズを低減するとともに、その電圧ノイズの伝播を阻止する電源配線系のノイズ低減構造を提供する。

【構成】 電源配線101は、電子回路装置を構成する個々の電子回路に電源を供給する。電源配線101には、電子回路動作時のノイズ電流のパルス幅の約半分の時間で電源配線に生じた電圧ノイズが到達する範囲内に負荷回路105、106、107が接続される。これらの負荷回路105、106、107は、抵抗と容量の直列回路で構成される。

【効果】 負荷回路の接続点において発生する反射波により、発生する電圧ノイズを低減するとともに、電源配線を伝播する電圧ノイズを減衰させることができる。

(もっと読む)

半導体集積回路のトリミング装置

【目的】 半導体集積回路のトリミング装置を簡略化し、またプリント基板の設計の自由度を増大させる。

【構成】 D/Aコンバータ20の複数の入力端子21〜24と接地電位間にそれぞれトリミング用ダイオードD21〜D24を接続し、D/Aコンバータ20の出力電流を出力端子25を介してカレントミラー回路19の入力端191に調整電流として入力する。

(もっと読む)

回路図による素子のグループ化方法

【目的】LSIレイアウト設計段階において、より効果的な配置配線を行うため、配置・配線の前段階として、接続の強い素子同士を近くに集める処理を行うが、この処理中に回路図を表示するという処理を加えることによって、処理の容易化を可能にすること。

【構成】接続の強い素子同士をグループとして近くに置くために、素子の判別を行う方法として、従来表示している素子名称と、これにつながる信号線名、制限の記述一覧表示に加え、回路図も表示することにより、両方を参照しての素子のグループ化を行う。

(もっと読む)

半導体装置

【目的】 過電流による素子破壊を防止するための電流制限回路を有する半導体装置において、制限動作時に発生する電流値の振動を防止し、安定的に電流を制限することが可能な半導体装置を実現する。

【構成】 スイッチング素子であるIGBT10のセンス用エミッタ14の下流に接続されたセンス用抵抗21の降下電圧で駆動されるMOSFET30によりバイパス制御されるゲート電圧を、IGBT10のゲート電極13の直前に挿入された緩和抵抗41を介してIGBT10に印加する。そして、IGBT10の応答速度を低下させることにより、センス用抵抗21における電圧の急増を防止し、安定的に電流を制限することができる。

(もっと読む)

絶縁ポリシリコン・ラインド・キャビィティを製造する半導体加工法、及びキャパシタを作る方法

【構成】 ウェーハ10上にポリシリコン含有構成要素に対して電気接続される面積15b及び選択的にエッチングすることができる第一材料層18を提供し;所定の開口横寸法を有する接触開口部20提供し;ポリシリコンの層22を蒸着させて、上記面積と接触させるがこのとき該選択された厚さは開口寸法の1/2未満でありかつポリシリコンによって接触開口部が完全に充填されなくその結果として外側に開口しているポリシリコン・ラインド・キャビィティ24が画定されるようにし;選択エッチング可能なネガ型フォトレジスト材料で被覆してキャビィティ24を完全に充填し;レジストとポリシリコンをレジストが溶解でき且つpHが10以上である現像成分を含むスラリーを用いて、第一材料層の上面まで化学的機械的に研磨し;キャビィティ24からレジストを選択的にエッチングする。

【効果】 キャビィティ中にスラリー残留物を残さない。

(もっと読む)

半導体装置およびその製造方法

【目的】スタックトキャパシタ構造のDRAMにおいて、全面に半球面状の凹凸を有する蓄積電極を形成して、表面積を増大させてキャパシタ容量を増やす。

【構成】P型シリコン基板1にフィールド酸化膜2を形成したのち、ゲート酸化膜3およびゲート電極4を形成する。つぎにソース5aおよびドレイン5bを形成する。つぎに層間絶縁膜6を形成したのち、ドレイン5bに接続する蓄積電極7を形成する。つぎにLPCVD法によりアモルファスシリコン8を成長したのち、エッチバックして各蓄積電極7間を分離する。つぎに500〜600℃で弗化水素処理を行なったのち、窒素雰囲気でアニールしてHSG−Si膜8aを形成する。

(もっと読む)

半導体集積回路装置およびその製造方法

【目的】 スタンダードセル方式の半導体集積回路装置およびそのチャネル型レイアウトにおけるレイアウト方法に関し,論理変更に伴うレイアウト変更時の配線チャネルの確保を容易にして,改版のコストを低減すると共に,TATの短縮を実現する。

【構成】 各種の単位論理機能を有するセルが複数個配置されるセル配置領域11,12,13が複数列設けられている。隣接するセル配置領域の間,およびセル配置領域の周囲に配線チャネル14が設けられている。配線チャネル14の全ての領域に電源配線17が挿入されている。配線のレイアウト変更が生じた場合には,信号配線の追加が必要な個所の電源配線17を電源から遮断して,追加の信号配線18として使用する。

(もっと読む)

9,661 - 9,670 / 9,686

[ Back to top ]