国際特許分類[H01L27/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153)

国際特許分類[H01L27/04]の下位に属する分類

複数の個々の構成部品を反復しない形で含むもの (2,326)

1種類の半導体構成部品だけを含むもの (8,288)

複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/04]に分類される特許

9,671 - 9,680 / 9,686

半導体装置

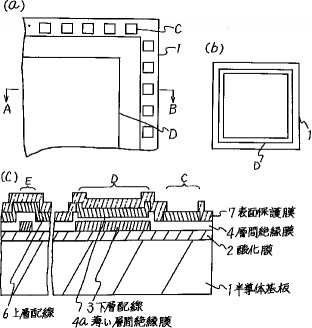

【目的】内部回路から発生する電源ノイズを低減するためのバイパスコンデンサを、半導体チップ内部に形成してシステムの小型化およびノイズ低減能力の向上を図る。

【構成】多層配線構造の半導体チップの外周に沿って、層間絶縁膜4の一部に薄い層間絶縁膜4aを設けて、対向する下層配線3と上層配線6とをそれぞれ電源配線と接地電位配線として、バイパスキャパシタとする。

【効果】半導体チップの面積を増加することなく、電源ノイズを低減するための大きな容量値をもつバイパスキャパシタを形成することができる。従来半導体チップの外部に実装していたキャパシタを削減して、システムを小型化することができる。半導体チップ内部にバイパスコンデンサを形成することにより、電源ノイズ低減効果が向上するとともに、EMI(電波雑音干渉)発生の低減を図ることができる。

(もっと読む)

半導体装置

【目的】 自動的に電流制限動作を行う過電流制限回路を備えたIGBTなどのスイッチング部を有する半導体装置において、電流制限動作時にスイッチング部を駆動するゲート駆動信号自体を制御することにより、電流制限動作の原因となっている過電流状態を解除すると共に、過電流状態であることを知らせるアラーム信号を発信可能とする。

【構成】 スイッチング部1の入力端子Pgの電圧を、判定回路3のコンパレータ31により判断し、電流制限回路20が稼働したことによるスイッチング部1の入力インピーダンスの変化から過電流が流れる状態にあることを判断する。その結果に基づき、制御部4において入力信号をオンからオフに切り換え、スイッチング部1をオフとすると共に、アラーム信号を発信する。

(もっと読む)

半導体装置の製造方法

半導体装置及びその製造方法

【目的】 容量を構成する穴の表面積を増大せしめ、より容量値の大きい容量を小面積で半導体基体内に得る。

【構成】 半導体基体1の表面の一部に多孔質形状の穴5を設け、該穴5に絶縁層6を介して導電材7を埋め込む。

(もっと読む)

大規模集積回路

【目的】全体に消費電力を低く抑えながらも高速動作を可能とし、且つ、回路の信頼性を下げない。

【構成】第1の供給電圧V1(例えば5[V])と第1の動作クロックCK1により動作する第1の回路部11と、上記第1の供給電圧より低電位の第2の電圧V2(例えば3[V])と第1の動作クロックCK1より周波数の高い第2の動作クロックCK2により動作する第2の回路部12とを1つの集積回路10上に設けるようにしたので、高速動作を要求される回路部(12)を低電圧駆動により実現する一方、それほど高速の動作を必要としない回路(11)に関しては信頼性を向上させるために低周波、高電圧駆動とする。

(もっと読む)

サーマルヘツドの製造方法

【目的】 各ヘッドにおける発熱抵抗体の抵抗値のばらつきと、ドット単位における発熱抵抗体の抵抗値のばらつきとを均一化して、印字品質を向上させるサーマルヘッドの製造方法を提供することである。

【構成】 絶縁性基板1上にグレーズ層2を設け、高融点金属と絶縁材料との混合組成の薄膜抵抗体材料からなる発熱抵抗体3をグレーズ層2に形成し、抵抗体3上に共通電極となるパターン導体4及び個別電極となるパターン導体5を形成し、更にパターン導体を覆う保護膜6を形成した後、印字動作時に必要なドット温度以上の温度になるように抵抗体3を加熱する。また、抵抗体膜を真空中でアニールして発熱抵抗体を作製した後、共通電極となるパターン導体及び個別電極となるパターン導体を形成し、更に、パターン導体4,5及び発熱抵抗体を覆う保護膜を形成することもできる。

(もっと読む)

半導体集積装置

【構成】 水晶発振器用半導体集積装置において発振部と出力バッファ部の電源系をそれぞれ別々の独立した電源パッドで供給する。また発振部と出力バッファ部をデジタル部で分離して配置する。また発振部自体も基板より回り込むノイズを到達しにくい様基盤と反対電位のウェルをデジタル部側及び出力バッファ側になる様レイアウトする。

【効果】 出力バッファからの電源電圧の変動等の悪影響を発振部に与えない。また出力バッファ部のノイズをデジタル部で吸収し発振部に到達しない。これらのレイアウトにより帰還発振及び異常発振を回避した性能の安定した発振器を提供する。

(もっと読む)

半導体集積回路実装基板

【目的】 高速スイッチング動作時の電源ノイズの発生が抑制され、信頼性が高くかつ半導体集積回路や個別部品の高集積化、高密度実装化を実現した半導体集積回路実装基板を提供する。

【構成】 第1の導電体電極層2と第2の導電体電極層4とこれらの 2つの層間に挟持される誘電体層3とにより形成されるコンデンサが、基板1上に配設されており、基板の最上層の表面に実装された半導体集積回路チップ8とは接続ビア(via)9、10によって接続され、チップコンデンサの表面実装およびその配線のための面積が不要でその分集積回路チップをより多く実装でき、またそれらの配置および結線の自由度も高くでき、半導体集積回路や個別部品の高集積化、高密度実装化が実現できる。

(もっと読む)

論理回路パターン形成方法

【目的】 本発明の目的は、プルダウントランジスタの動作に起因するノイズの減少を図った論理回路を容易に形成し得る技術を提供することにある。

【構成】 モディファイパターンセルを基本回路パターンセルに選択的に結合させることによりSPLゲート50Aの形成を可能とし、ワイヤードオアの形成においてNTLゲートとSPLゲートとの選択的な配置配線を可能とすることで、ノイズ低減を図ったワイヤードオアの形成の容易化を図る。

(もっと読む)

半導体定電流源回路

【目的】 外部バイアス用の端子を必要とせずに、製造後検査時に良好な電流値を設定しうる低電流源回路を提供する。

【構成】 FET110と、このFET110のゲート−ソース間にラダー回路120とを備えている。FET110は、デプレーション型であり、そのゲートはVSS即ち電源の負側につながれている。ラダー回路120では、多数の抵抗121と多数の溶断可能配線としてのヒューズ122とがラダー状に接続されている。即ち抵抗121が直列につながれ、その抵抗121の端点を短絡するようにヒューズ122が接続されている。

(もっと読む)

9,671 - 9,680 / 9,686

[ Back to top ]