国際特許分類[H01L27/11]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | 電界効果構成部品を含むもの (11,969) | スタティックランダムアクセスメモリ構造 (855)

国際特許分類[H01L27/11]に分類される特許

121 - 130 / 855

スタティックランダムアクセスメモリ

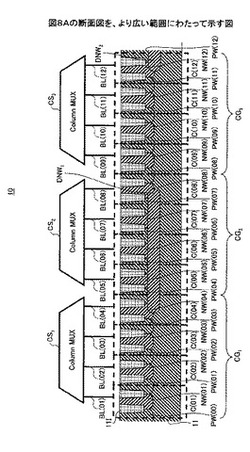

【課題】第1の導電型の共通ウェルが形成された半導体基板と、前記半導体基板上の前記共通ウェルに行列状に配列されたメモリセルよりなり、列方向に整列して共通のビット線に接続される一群のメモリセルがメモリセルカラムを形成するメモリセルアレイからなるスタティックランダムアクセスメモリにおいて、隣接カラム群間のソフトエラーの伝搬を抑制する。

【解決手段】隣接する第1および第2のカラム群において、前記第1のカラム群CG1で選択される一のメモリセルカラムの第1導電型ウェルPW(01)と、第2カラム群CG2で同時に選択されるメモリセルカラムの第1導電型ウェルPW(05)は、いずれか一方が、共通ウェル11から、第2導電型の深いウェルDNW1により遮断されており、前記第2導電型の深いウェルDNW1は、行方向に測った場合の一つのカラム群の寸法を超えない寸法を有する。

(もっと読む)

記憶装置、集積回路装置、及び電子機器

【課題】マルチポートメモリーとして機能する場合に、クロストークノイズを大幅に低減して、誤動作を防止して回路動作の安定化を図る記憶装置等を提供する。

【解決手段】メモリーセルアレイ10を有する半導体記憶装置100は、第1の方向に並ぶメモリーセルを選択するための第1のワードラインと、第2の方向に並ぶメモリーセルを選択するための第2のワードラインと、第1のワードラインによって選択されたメモリーセルに接続される一対の第1のビットライン及び第1の相補ビットラインと、前記第2のワードラインによって選択されたメモリーセルに接続される第2のビットラインとを含み、第2のワードラインは、対応する一対の第1のビットライン及び第1の相補ビットラインに対し、上面から見て第1の方向又は該第1の方向の反対方向に隣接して、第2の方向に延びるように配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の形状を精度良く形成すると共に、隣り合うゲート電極同士がショートすることを防止する。

【解決手段】開口部を有するマスク16Mを用いて、導電膜15にイオンを注入し、ミキシング膜20Xを形成する。次に、マスクを除去した後、導電膜及びミキシング膜の上に、平面形状がライン形状のレジストパターン21を形成する。次に、レジストパターンをマスクとして、導電膜及びミキシング膜をエッチングし、導電膜15aを有するゲート電極を形成すると共に、ゲート電極のゲート幅方向の側面の上に、ミキシング膜20xを残存させる。次に、熱処理により、ミキシング膜に含まれるイオンと、元素(元素は、導電膜に由来する)とを反応させて、絶縁膜24xを形成する。絶縁膜は、ゲート電極と一体に形成されている。絶縁膜により、ゲート電極と、該ゲート電極とゲート幅方向に沿って隣り合う他のゲート電極との間が電気的に分離されている。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタの特性ばらつきを増大させることなく、面積が縮小可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1における第1の素子分離領域2aに囲まれた第1の活性領域1aと、第1の活性領域上に順次形成された第1のゲート絶縁膜6a、第1のゲート電極9aとを有する第1のMISトランジスタと34と、半導体基板1における第2の素子分離領域2bに囲まれた第2の活性領域1bと、第2の活性領域上に順次形成された第2のゲート絶縁膜6b、第2のゲート電極9bとを有する第2のMISトランジスタ32とを備える。第1のゲート電極9aは、第1の活性領域1aの上面上だけでなく側面上に第1のゲート絶縁膜6aを介して形成されており、第2のゲート電極9bは、第2の活性領域1bの上面上に形成されており、側面上には形成されない。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法

【課題】消費電力の少ない新規の半導体メモリ装置を提供する

【解決手段】書き込みトランジスタWTr_n_mのソースと読み出しトランジスタRTr_n_mのゲートとキャパシタCS_n_mの一方の電極を接続し、書き込みトランジスタWTr_n_mのゲートとドレインを、それぞれ書き込みワード線WWL_nと書き込みビット線WBL_mに、キャパシタCS_n_mの他方の電極を読み出しワード線RWL_nに、読み出しトランジスタRTr_n_mのドレインを読み出しビット線RBL_mに接続した構造とする。ここで、読み出しビット線RBL_mの電位はフリップフロップ回路FF_mのような反転増幅回路に入力され、反転増幅回路によって反転された電位が書き込みビット線WBL_mに出力される構造とする。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】SRAMは高速で省電力なメモリであるが、携帯機器等で使用するにはさらなる省電力化が求められる。

【解決手段】オフ抵抗が極めて高いトランジスタを書き込みトランジスタとし、書き込みトランジスタのドレインを書き込みビット線に、ソースをCMOSインバータの入力に接続し、読み出しトランジスタのドレインを読み出しビット線に、ソースをCMOSインバータの出力に接続したメモリセルを用いる。書き込みトランジスタのソースにはキャパシタを意図的に設けてもよいが、CMOSインバータのゲート容量あるいはCMOSインバータの正極や負極との間の寄生容量等を用いることもできる。データの保持はこれらのキャパシタに蓄積された電荷によっておこなえるため、CMOSインバータの電源間の電位差を0とできる。このため、CMOSインバータの正負極間を流れるリーク電流がなくなり、消費電力を低減できる。

(もっと読む)

半導体装置およびその製造方法

【課題】高密度で素子特性に優れた、SRAMを備えた半導体装置を提供する。

【解決手段】一対の駆動トランジスタと一対の負荷トランジスタと一対のアクセストランジスタを備えたSRAMセル単位を有する半導体装置であって、前記トランジスタはそれぞれ、基体平面に対して上方に突起した半導体層と、この半導体層を跨ぐようにその上部から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体層の間に介在するゲート絶縁膜と、前記半導体層に設けられた一対のソース/ドレイン領域を有し、前記駆動トランジスタはそれぞれ、前記負荷トランジスタ及び前記アクセストランジスタの少なくとも一方の各トランジスタのチャネル幅より広いチャネル幅を有する半導体装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極側に位置する側壁部において、面方位が(100)の第1の斜面と、第1の斜面と交差する面方位が(100)の第2の斜面と、を有する。上記構成によれば、基板の表面(110)面と(100)面とのなす角は45°となり、比較的鋭角に第1斜面が形成されるため、効果的にpチャネル型のMISFETのチャネル領域に圧縮歪みを印加することができる。

(もっと読む)

半導体装置

【課題】半導体装置を小型化することを課題の一とする。また、記憶素子を有する半導体装置の駆動回路の面積を縮小することを課題の一とする。

【解決手段】入力端子と出力端子の位置が固定された複数のセルを第1の方向に配置し、各セルの入力端子および出力端子とそれぞれ電気的に接続される配線を複数のセル上に積層させ、且つ、その配線の延在方向をセルが並べられた第1の方向と同方向とすることで、駆動回路の小型化を図った半導体装置を提供する。

(もっと読む)

121 - 130 / 855

[ Back to top ]