国際特許分類[H01L27/11]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | 電界効果構成部品を含むもの (11,969) | スタティックランダムアクセスメモリ構造 (855)

国際特許分類[H01L27/11]に分類される特許

71 - 80 / 855

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2

の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上

に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を

有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第

3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のド

ーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させる。

【解決手段】ゲート電極GE1,GE2、ソース・ドレイン用のn+型半導体領域SD1及びp+型半導体領域SD2を形成してから、半導体基板1上にNi−Pt合金膜を形成し、第1の熱処理を行って合金膜とゲート電極GE1,GE2、n+型半導体領域SD1及びp+型半導体領域SD2とを反応させることで、(Ni1−yPty)2Si相の金属シリサイド層13aを形成する。この際、Niの拡散係数よりもPtの拡散係数の方が大きくなる熱処理温度で、かつ、金属シリサイド層13a上に合金膜の未反応部分が残存するように、第1の熱処理を行う。その後、未反応の合金膜を除去してから、第2の熱処理を行って金属シリサイド層13aを更に反応させることで、Ni1−yPtySi相の金属シリサイド層13bを形成する。第2の熱処理の熱処理温度は580℃以上で、800℃以下とする。

(もっと読む)

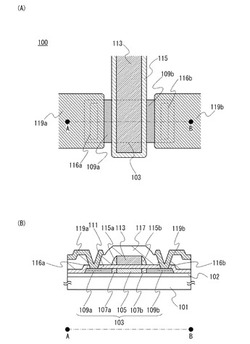

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体集積回路装置

【課題】本発明は、従来のSRAMメモリセルでは、Pウエル領域の基板へのコンタクトをとるために、拡散層の形を鍵状に曲げる必要があった。このため、対称性が悪く微細化が困難であるという問題があった。

【解決手段】SRAMセルを構成するインバータが形成されたPウエル領域PW1、PW2が2つに分割されてNウエル領域NW1の両側に配置され、トランジスタを形成する拡散層に曲がりがなく、配置方向が、ウエル境界線やビット線に平行に走るように形成される。アレイの途中には、基板への電源を供給するための領域が、メモリセル32ローあるいは、64ロー毎に、ワード線と平行に形成される。

(もっと読む)

半導体装置の製造方法

【課題】 CMOS型半導体装置におけるデュアルゲート構造のゲート電極をエッチングにより形成する時に、局所的なゲート絶縁膜の「突き抜け」やゲート電極サイドエッチ等の欠陥が発生することを防止できる製造方法を提供する。

【解決手段】 ゲート絶縁膜5を介して半導体基板1上に形成されたシリコン膜等の、実質的に不純物を含まない半導体膜6を選択的にエッチングしてゲート電極7を形成する。隣接するゲート電極7間の領域をレジスト等の絶縁膜9で埋め込む。さらに例えば所定のゲート電極7が形成された領域を覆うマスク層10を形成し、絶縁膜9とマスク層10とをマスクとして、マスク層10で覆われないゲート電極7にイオン注入等の手段により所定導電型の不純物を導入する。同様の方法を用いてマスク層10で覆われていたゲート電極7に異なる導電型の不純物を導入する。

(もっと読む)

スイッチトランジスタを有しない差動センス増幅器

【課題】半導体メモリのセンス増幅器は、回路全体の面積を増やし、製造コストを押し上げるため、センス増幅器に使用される面積を最小限に抑える必要がある。

【解決方法】本発明の差動センス増幅器は、第1のビットライン(BL)に接続された出力および第1のビットラインに対して相補的な第2のビットライン(/BL)に接続された入力を有する第1のCMOSインバータと、第2のビットライン(/BL)に接続された出力および第1のビットライン(BL)に接続された入力を有する第2のCMOSインバータとを備え、それぞれのCMOSインバータはプルアップトランジスタ(M21、M22)および前記プルダウントランジスタ(M31、M32)を備え、プルアップトランジスタ(M21、M22)またはプルダウントランジスタ(M31、M32)のソースは、トランジスタのソースと電圧源との間に中間トランジスタを置くことなく、プルアップ電圧源またはプルダウン電圧源に電気的に結合され、接続されることを特徴とする。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

半導体装置

【課題】先端プロセスでは、MOSのゲートトンネルリーク電流が増大し、低リーク電流での待機が必要となる半導体装置では問題となる。

【解決手段】電源線とソース線との電位差である複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路を具備する。負荷型P型MOS及び駆動型N型MOSのゲート絶縁膜厚は、4nm以下である。電源電圧制御回路は、動作状態では前記電源電圧を第1電圧とし、待機状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御して、オフ状態での負荷型P型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、駆動型N型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を動作状態に対し待機状態の方を小さくする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接する、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタを有し、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第1の酸化絶縁膜上に位置する。

(もっと読む)

71 - 80 / 855

[ Back to top ]