国際特許分類[H01L27/11]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | 電界効果構成部品を含むもの (11,969) | スタティックランダムアクセスメモリ構造 (855)

国際特許分類[H01L27/11]に分類される特許

801 - 810 / 855

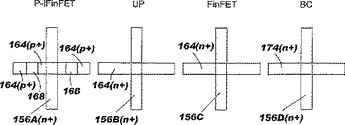

反転型FinFET薄膜トランジスタを用いたFinFETSRAMセル

【課題】反転型FinFETトランジスタ(P2)とFinFETトランジスタ(N3)とを含む、SRAMセル(130)などの集積回路を提供すること。

【解決手段】反転型FinFETトランジスタは、基板上に半導体構造(100)によって形成された第1のゲート領域(108)、ならびに、第1のゲート領域上に配置された第1のチャネル領域(112)と、第1のチャネル領域のいずれか一方の側に形成されたソース(110)およびドレイン(114)とを有する、半導体層(104)からなる第1のボディ領域を含む。FinFETトランジスタ(N3)は、反転型FinFETトランジスタに結合しており、第2のチャネル領域(118)と、第2のチャネル領域のいずれか一方の側に形成されたソース(116)およびドレイン(120)とを有する、半導体構造(102)によって形成された第2のボディ領域、ならびに、第2のチャネル領域上に配置された、半導体層からなる第2のゲート領域(122)を含む。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】 低電源電圧でもSNMと書き込みマージンを両立させることができるスタティック型RAMを備えて半導体集積回路装置を提供する。

【解決手段】 複数のワード線と複数の相補ビット線に対応して設けられた複数のスタティック型メモリセルを備え、上記複数の相補ビット線のそれぞれに接続される複数からなるメモリセル毎に動作電圧を供給する複数のメモリセル電源線を設け、かかるメモリセル電源線に対応してそれぞれ電源電圧を供給する抵抗手段からなる複数の電源供給回路を設け、上記相補ビット線に上記電源電圧に対応したプリチャージ電圧を供給するプリチャージ回路を設け、上記メモリセル電源線は、対応する相補ビット線の書き込み信号が伝えられる結合容量を持つようにする。

(もっと読む)

半導体装置

【課題】 半導体基板の主表面に対して平行な方向における面積を小さくすることができる薄膜トランジスタを有するラッチ回路を備えた半導体装置を提供する。

【解決手段】 1つのメモリセル領域100を横切る同一層に形成されたビット線15および他のビット線とは別の層にグラウンド配線層16が形成されている。このグラウンド配線層16は、メモリセル領域100内のほぼ全ての領域にわたって形成されている。また、メモリセル領域100内においてプラグ18および19がグラウンド配線層16を上下に貫通しているが、絶縁膜18aおよび絶縁膜19aによってグラウンド配線層16とプラグ18および19のそれぞれとが絶縁されている。

(もっと読む)

不揮発性メモリセルおよびその制御方法

第1のノード(6)と第2のノード(7)とを備え、第1のノード(6)と第2のノード(7)とに設定される相補データをラッチするラッチ回路(1)、第1のノード(6)と第1のデータ入出力線(2)とを接続する第1のスイッチング素子(4)、第2のノード(7)と第2のデータ入出力線(3)とを接続する第2のスイッチング素子(5)、第2のデータ入出力線(3)と第1のノード(6)とを接続する第1の強誘電体キャパシタ(8a)、および第1のデータ入出力線(2)と第2のノード(7)とを接続する第2の強誘電体キャパシタ(8b)を備える不揮発性メモリセル。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】 位相比較誤差の低減を図る。

【解決手段】 クロック入力部(190)とデータ入力部(112)とを結ぶ線(201)に直交し、且つ、上記クロック入力部を通る第1ライン(L1)と、上記第1ラインに対して並行され、且つ、上記データ入力部における上記クロック入力部側を通る第2ライン(L2)との間に、位相調整回路(130)を配置する。上記第1ラインと上記第2ラインとの間に上記位相調整回路が配置されることにより、クロック入力部から位相調整回路における正規クロック入力回路までの距離と、データ入出力部から位相調整回路におけるレプリカクロック入力回路までの距離とをほぼ等しくすることができるので、上記クロック入力部から上記正規クロック入力回路に至る配線と、上記データ入出力部から上記レプリカクロック入力回路に至る配線とを等長配線とすることで、上記位相調整回路における位相比較回路での位相比較誤差の低減を達成する。

(もっと読む)

半導体装置

【課題】 4つのトランジスタで構成したメモリセルを用いた半導体装置において、リフレッシュを伴わない情報保持と安定した読出し動作、低待機電力を実現すること。

【解決手段】 メモリセルMCの記憶ノードN1,N2にキャパシタC1,C2を設け、情報読み出し時には、破壊読み出しをした後に再書き込みを行い、情報保持時には、ビット線BL,/BLを一定電位に保ち、トランジスタMP1,MP2を流れるリーク電流により記憶ノードN1,N2の電位を保持する。その際、トランジスタMN1,MN2のオフ状態でのインピーダンスは、トランジスタMP1,MP2のオフ状態でのインピーダンスよりも大きくする。さらに、チャネル部が5nm程度以下のTFTトランジスタを用いて、リーク電流を低減させる。

(もっと読む)

半導体記憶装置

【課題】レプリカビット線の電荷をダミーセルのリーク電流により早く引き抜いてしまい、所望のセンスアンプ起動タイミングを得ることができない。

【解決手段】 メモリアレイと、センスアンプ回路と、メモリセルと同一の素子を有し、段数に応じたレベルの信号を共通のレプリカビット線に出力する複数のレプリカセル105を含むレプリカ回路と、共通のレプリカビット線に負荷として接続されているダミーセル109Bとを備え、ダミーセル109BのドライブトランジスタND1のソースをHighレベルVDDに接続する。これによりレプリカビット線REPBLからダミーセルへのリーク電流を抑え、最適な起動タイミングをセンスアンプ回路に供給できる。

(もっと読む)

スタティック・ランダム・アクセス・メモリ

【課題】スタティックノイズマージンの低下を抑制すること。

【解決手段】ビット線18はロードトランジスタ14のウェルに接続され、反転ビット線18はロードトランジスタ13のウェルに接続されている。ノードN1は“L”レベル、ノードN2は“H”レベルである。リード時にはビット線18,19は“H”レベルにプリチャージされる。ワード線17が“H”レベルに立ち上がるとドライバトランジスタ11にカラム電流が流れる。ビット線18の電位が“L”レベルに変化すると、同時にロードトランジスタ14のウェル電位が“L”レベルに変化するのでロードトランジスタ14の電流駆動能力が向上し、ノードN1の電位がノイズ等によって上昇しドライバトランジスタ12が僅かにオン動作してもノードN2の電位が“H”レベルから低下するのが抑制されビット線18,19の電位差読み取りが可能になりリード時の誤動作が低減される。

(もっと読む)

半導体装置およびその製造方法

【課題】ボディコンタクトを有するSOIデバイスにおいて、ボディコンタクトとボディ領域との間に所望の抵抗値を持たせると共に、当該抵抗値のばらつきを抑制する。

【解決手段】SOI層3におけるコンタクト61との接続部分(即ち、素子分離絶縁膜41の下)に、不純物濃度の高いP+領域を形成せずに、SOI層3とボディコンタクト61とをショットキー接合させる。また、ボディコンタクト61の表面にはバリアメタル61aが形成されており、ボディコンタクト61とSOI層3との間に、バリアメタル61aとSOI層3とが反応したシリサイド70が形成される。

(もっと読む)

半導体装置、及びその製造方法

【課題】 単層ポリシコンゲートから成る不揮発性メモリのセル面積を低減し、かつ超低消費電力で動作させる。

【解決手段】 フローティングゲート6端下部のN型ウエル4の基板表面に、ゲート酸化膜5を介在させて設けられたP型不純物領域8と、前記N型ウエル4が構成する接合に−5Vのような逆バイアス電圧を印加して、バンド間トンネル現象によって発生するホットエレクトロンを前記フローティングゲート6へ注入して書込みを行う。書込み時間はおおよそ10μs、書込み動作時の前記接合の漏洩電流は100nA程度に設計できるため、書込みに要するエネルギーは5pJまで低減され、従来のスタックド・ゲート型メモリセルのチャンネルホットエレクトロン注入を用いた書込みのエネルギーに比較して1/100以下に低減できる。

(もっと読む)

801 - 810 / 855

[ Back to top ]