国際特許分類[H01L27/11]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | 電界効果構成部品を含むもの (11,969) | スタティックランダムアクセスメモリ構造 (855)

国際特許分類[H01L27/11]に分類される特許

831 - 840 / 855

ソフトエラー率計算方法及び計算装置

【課題】

従来の、SRAMやロジック回路等の半導体素子あるいはLSIの、α線、或いは宇宙線によるソフトエラーのエラー率計算方法では、マルチビットエラーが発生した場合、パターンが実際と異なるという問題があった。

【解決手段】

発生したイオンによる電荷が水平にイオンが走った場合、従来は、VH(High電位)側NMOSノード3に対するVL(Low電位)側NMOSノードの領域6、VH側NMOSノード3に対するVH側PMOSノードの領域5、VL側PMOSノード4に対するVH側PMOSノード5の領域、VL側PMOSノード4に対するVL側NMOSノードの領域6はエラーとは関係ないとして計算では考慮しなかった。本発明では、このHigh-Lowが問題となるノードのペアとなる領域に電荷が発生した場合、従来エラーに関係ないと見なしていた電荷によるエラー抑制効果をソフトエラーシミュレーションに組込むようにした。これにより、マルチビットエラーのパターンが実測に合うようになった。

(もっと読む)

半導体記憶装置およびダミーセルの回路のレイアウト

【課題】 メモリアレイと、センスアンプ回路と、レプリカビット線に接続されたレプリカ回路、ダミーセルおよびセンスアンプ制御回路とを有する半導体記憶装置であって、レプリカビット線をダミーセルのリーク電流により速く引き抜いてしまい、所望のセンスアンプ起動タイミングが得られない。

【解決手段】 ダミーセル109Bが2つの直列に接続されたオフ状態のトランジスタ501、502を含み、片方を定電圧源に、もう片方をレプリカビット線REPBLに接続する。これによりレプリカビット線REPBLからダミーセル109Bへのリーク電流を抑え、最適な起動タイミングをセンスアンプ回路に提供できる。

(もっと読む)

半導体装置

【課題】 信頼性の高い半導体装置を実現するために、寄生容量の大きな半導体装置を提供する。

【解決手段】 半導体装置は、第1方向に延在する突出部1bを有する半導体基板1を含む。ゲート絶縁膜11は、突出部の上面上および第1方向に沿う側面上に配設される。ゲート電極12は、第1部分12aと第2部分12bを有する。第1部分は、突出部と交差し、且つ突出部の上面上のゲート絶縁膜上に配設される。第2部分は、突出部の側面上のゲート絶縁膜上に配設され、且つ第1方向における長さが第1部分の第1方向における長さより長い。1対のソース/ドレイン領域13が、ゲート電極の第1部分の下方の領域を挟むように突出部の表面に形成される。

(もっと読む)

半導体記憶装置、半導体記憶装置の製造方法

【課題】完全CMOS型SRAMセルとして、セル面積とコストを大きく増やすことなくソフトエラー耐性を向上すること。

【解決手段】第1(2)の駆動用および負荷用MISFETのゲート電極が、第1(2)の転送用MISFETのゲート電極と別に一体型のN型ポリシリコンで形成され、該N型ポリシリコン中の不純物濃度が制御されて第1(2)の抵抗素子が形成されており、第1および第2の抵抗素子が、それぞれ、第1または第2の負荷用MISFETのゲート電極の先であって、第1または第2の駆動用MISFETとは逆方向側に形成されており、第2(1)のインバータの出力ノードからの配線が、第1(2)の抵抗素子となるN型ポリシリコンの上部に形成されたコンタクト電極に繋がり、第1および第2の負荷用MISFETが、N型ゲート電極をもつ。

(もっと読む)

半導体記憶装置

SRAMメモリセルをFD-SOIトランジスタで構成し、駆動トランジスタを構成するSOIトランジスタの埋め込み酸化膜の下の層の電位を制御して、メモリセルの性能を向上させる。

【課題】

低電源電圧状態でのSRAM回路の性能を向上させる。

【解決手段】

FD-SOIトランジスタを用いて構成されたSRAMメモリセルにおいて、駆動トランジスタのBOX層下のウエル電位を制御することでVthを制御して電流を増加させて、メモリセルの安定動作を可能とする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置、例えばSRAMのメモリセルのα線によるソフトエラーを低減する。

【解決手段】基板1aをエッチングして第1配線溝HM1を形成し、第1配線溝HM1下の素子分離2(または素子分離溝2および絶縁層1c)をエッチングして第2配線溝HM2を形成し、第1配線溝HM1および第2配線溝HM2の内壁に沿って局所配線16a,16bを形成し、一方の局所配線16aを下部電極ELとして、その下部電極EL上に容量絶縁膜となる窒化シリコン膜17、さらに上部電極EUを形成することにより、容量CA1の面積を増加させて、メモリセルの記憶ノードに相対的に大きな静電容量を付加する。

(もっと読む)

リセスデバイス付きメモリ

メモリセル(100,101)は、関連する、規模の異なる分離リセス(908)を有するデバイスを含んでいる。対応するトランジスタの有効チャネル幅は、チャネルの上面幅に、分離リセス(908)によって形成された側壁幅の2倍を加えたものと、実質的に等しい。SRAMセル(100,101)では、ラッチトランジスタ(112)は、より大きなリセス(908)を形成し、従って、ラッチトランジスタ(112)を囲む分離層(906)内に大きな側壁(1306,1310)を形成し、且つその様なリセスをパストランジスタには制限することにより、関連するパストランジスタ(108)よりも大きな有効チャネル幅を有している。メモリセル(100,101)の製造の際は、ラッチトランジスタ(112)の区域を露出させながらパストランジスタ(102)の区域をマスキングするためにマスクが用いられる。従って、ラッチトランジスタ(112)の回りの分離層内のリセスは、パストランジスタ(108)の回りの対応する区域に影響を及ぼすこと無く形成される。  (もっと読む)

(もっと読む)

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

改良されたレイアウトのSRAMメモリセル

本発明は、二つのインバータと複数のスイッチを備えたSRAMメモリセルであって、SRAMセルがN/Pシャント能力を提供する技術において製造され、インバータの入力が少なくとも一対のビットライン(BLa、BLa/;BLb、BLb/)に前記スイッチの二つを介して接続されており、前記スイッチが信号ワードライン(WLa、WLb)によって制御され、各インバータが第1導電性タイプの第1トランジスタ(MN0、MN1)と第2導電性タイプの第2トランジスタ(MP0、MP1)を備え、そして、各スイッチが第1導電性タイプの少なくとも第3トランジスタ(MN2、MN3)を備えるSRAMメモリセルであって、インバータにおける第2導電性タイプの二つのトランジスタ(MP0、MP1)がメモリセルの二つの対向端部領域にそれぞれ配置されていることを特徴とするSRAMメモリセルを提案する。  (もっと読む)

(もっと読む)

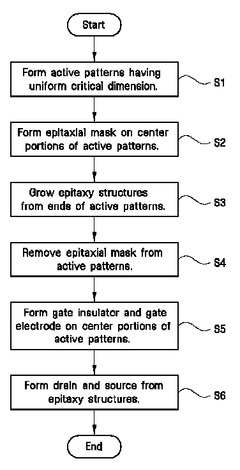

均一な臨界寸法のアクティブパターンで形成されたマルチゲートトランジスタ及びその製造方法

本発明は、均一な臨界寸法のアクティブパターンで構成されたマルチゲートトランジスタの製造方法を提供する。本発明はまた、均一な臨界寸法のアクティブパターンを具備するマルチゲートトランジスタを提供する。マルチゲートトランジスタの製造方法は先に少なくとも一つのアクティブパターンを形成する。以後、前記アクティブパターンの露出した領域から少なくとも一つのエピタキシ構造を成長させる。続いて、前記アクティブパターンの少なくとも2個の面にチャネル領域を形成する。  (もっと読む)

(もっと読む)

831 - 840 / 855

[ Back to top ]