国際特許分類[H01L27/11]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | 電界効果構成部品を含むもの (11,969) | スタティックランダムアクセスメモリ構造 (855)

国際特許分類[H01L27/11]に分類される特許

811 - 820 / 855

メモリセル構造

【課題】 従来技術の問題およびその他の問題を解決するメモリセル構造のシステムを提供する。

【解決手段】 SRAMデバイスは基板中のディープNウェル領域中にあるSRAMセルを含む。SRAMセル中のPウェル領域は、SRAMセルの65%よりも少ないセル領域を占める。SRAMセルは、セル領域の長辺と短辺との比率が1.8よりも大きい。SRAMセル中の複数のNMOSトランジスタ中にある活性領域が占める総面積は、SRAMセル領域の25%よりも少ない。SRAMセル中のプルアップトランジスタのチャネル幅とSRAMセル中のプルダウントランジスタのチャネル幅との比率は0.8よりも大きい。SRAMセルは、ホウ素を含まない層間絶縁膜層と、誘電率が3よりも小さい金属間絶縁膜層と、厚みが20ミクロンよりも小さいポリイミド層とをさらに含む。

(もっと読む)

DRAMセル用の分離領域を有する半導体構造及び製造方法

本発明は、垂直に延びるピラー(80,82)を含む半導体構造、及び、そのような構造を形成する方法を含む。垂直に延びるピラーは、トランジスタデバイス(80,95)内に組み込まれることができ、トランジスタデバイスの垂直に延びるチャネル領域を含むことができる。トランジスタデバイスは、集積回路内に組み込まれることができ、ある態様では、たとえば、ダイナミックランダムアクセスメモリ(DRAM)構造などのメモリ構造に組み込まれる。  (もっと読む)

(もっと読む)

SRAMメモリセルおよび半導体記憶装置

【課題】 面積の増大なしにメモリセルのデータを一括書込みできる。

【解決手段】 第1のN型MOSトランジスタ102と第2のP型MOSトランジスタ103とで構成される第1のインバータと、第3のN型MOSトランジスタ104と第4のP型MOSトランジスタ105とで構成される第2のインバータと、第1のインバータの出力に接続した第5のトランジスタ106と、第2のインバータの出力に接続した第6のトランジスタ107とを有し、第1と第2のインバータとでラッチ回路を構成し、第2のトランジスタ103と第4のトランジスタ105のソースは共通の電源線に接続され、第1のトランジスタ102と第3のトランジスタ104のソースはそれぞれ第1および第2の端子108,109に接続され、第1または第2の端子108,109を制御することによってラッチ回路の保持データを任意の状態に設定できる。

(もっと読む)

セルフバイアストランジスタ構造およびSRAMセル

自己バイアス半導体スイッチを供給することで、個々のアクティブコンポーネント数を減らしたSRAMセル(450)を実現することができる。特定の実施形態では、自己バイアス半導体デバイスを、ダブルチャネル電界効果トランジスタ(400)の形式で与えることができる。このトランジスタは、トランジスタ数が6つ未満の、また、好ましい実施形態では、わずか2つの個々のトランジスタ素子を備えたSRAMセル(450)の形成を可能にする。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 SRAMセルの動作マージンを広く確保することができる半導体装置及びその製造方法を提供し、また、ソフトエラー耐性を向上することができる半導体装置及びその製造方法を提供する。

【解決手段】 p型のSi基板1に素子分離絶縁膜2を形成した後、SRAMセル領域のN−LV領域内にn型の埋め込み層20を形成する。その後、pウェル及びnウェルを形成する。そして、チャネルドープ層の形成の際には、論理回路領域のN−LVへのイオン注入と並行して、SRAMセル領域のN−LV領域内にもイオン注入を行い、更に、I/O領域のN−MVへのイオン注入と並行して、SRAMセル領域のN−LV領域内にもイオン注入を行う。

(もっと読む)

集積メモリデバイスおよびその製造方法

【課題】容易に製造可能であり、セルのサイズの縮小を可能にするメモリデバイスを提供する。

【解決手段】 本発明の、トンネル電界効果トランジスタ(TFET)と埋込みビット線とを用いたメモリデバイスには、記憶セルの行および列を含む行列が含まれる。各記憶セルには、少なくとも1つのセルトランジスタ(T01〜Tmn)が含まれ、そのセルトランジスタは第1のドープされた領域と第2のドープされた領域とを含んでおり、一方がソース領域(98)であり、もう一方がドレイン領域(152)である。そのメモリデバイスにはワード線(T01〜Tmn)が含まれ、各ワード線は1つの行にあるメモリセルとビット線とに接続されており、各ビット線は1つの列における記憶セルに接続されている。第1のドープされた領域と第2のドープされた領域のドーピングタイプは異なる。

(もっと読む)

半導体装置並びにその配置及び製造方法

【課題】半導体装置及びその装置の配置及び製造方法を提供する。

【解決手段】複数のワードライン選択信号と複数のカラム選択信号に応答してアクセスされる複数のメモリセルを備えたメモリセルアレイ、ロウアドレスをデコーディングして複数のワードライン選択信号を発生するロウデコーダ、及びカラムアドレスをデコーディングして複数のカラム選択信号を発生するカラムデコーダを備える。ロウ及びカラムデコーダは、複数のインバータ及び複数のNANDゲートを備える。複数のインバータそれぞれは、少なくとも一つの第1プルアップトランジスタ及び第1プルダウントランジスタを備る。複数のNANDゲートそれぞれは、少なくとも2個の第2プルアップトランジスタ及び少なくとも2個の第2プルダウントランジスタを備える。第1及び第2プルアップトランジスタ及び第1及び第2プルダウントランジスタは、少なくとも2層に積層して配置され。

(もっと読む)

半導体記憶装置

【課題】所望のタイミングで高速な初期値設定を可能にすると共に、セルの形成面積の増大を抑え、また、初期値決定のためのSRAMセルのパターン変更を容易にする。

【解決手段】SRAMセルは、ソースが接地されたNMOSトランジスタQ7を有する。第1記憶ノードN1、第2記憶ノードN2およびNMOSトランジスタQ7のドレインは、同一の配線層に形成された第1,第2及び第3のアルミ配線21,22,23にそれぞれ接続する。第3のアルミ配線23は、第1及び第2のアルミ配線21,22の一方と一体形成され、且つ、他方に近接して配設される。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】SRAMセルの形成面積の増大を抑えつつ、動作の安定化を図る。

【解決手段】SRAMセルのアクセストランジスタQ5のゲート電極33の上には、ワード線に接続するコンタクト45が形成される。コンタクト45は、素子分離絶縁膜14を突き抜けてSOI層13にまで達する。ドライバトランジスタQ1のボディー領域と第1アクセストランジスタQ5のボディー領域とは、素子分離絶縁膜14下方のSOI層13を介して互いに電気的に接続している。よって、アクセストランジスタQ5はそのゲート電極とボディー領域との間がコンタクト45で接続されたDTMOS構造になり、コンタクト45はさらに第1ドライバトランジスタQ1のボディー領域にも電気的に接続する。

(もっと読む)

半導体装置

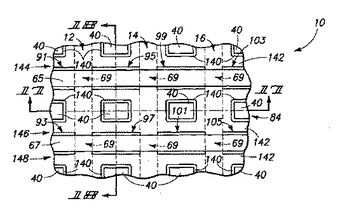

【課題】 ビット線及びワード線に対するクロストークを低減しながら上層の信号配線を配置可能とし、かつブロック配置ローテーションの制約がなくチップ上の信号配線方向に適合したレイアウト構造を有することで、デッドスペースの発生や配線乗り換えによる面積ロスを低減する。

【解決手段】 スタティックRAMのメモリセルアレイ領域10上においてワード線21,22…とビット線31a,31b…との交点を縦横2点ずつ覆うようにダミー配線パターン411,412…,421,422…を形成することで、これらダミー配線パターンの間に横方向に走る配線チャネル5a1,5a2…と、縦方向に走る配線チャネル5i1,5i2…とを格子状に形成する。いずれかの配線チャネル(例えば5a2)を通るように信号配線70を自動配置する。この信号配線70は、ワード線21,22…の上層に位置し、かつダミー配線パターンと同層のメタル配線である。

(もっと読む)

811 - 820 / 855

[ Back to top ]