国際特許分類[H01L27/11]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | 電界効果構成部品を含むもの (11,969) | スタティックランダムアクセスメモリ構造 (855)

国際特許分類[H01L27/11]に分類される特許

841 - 850 / 855

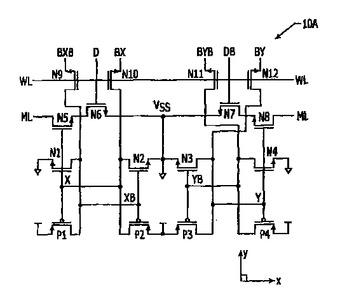

放射線耐性のあるSRAMビット

1つの入力と1つの出力を有する第1インバータと、1つの入力と1つの出力を有する第2インバータとを備える集積回路における放射線耐性のあるSRAM装置。第1抵抗は、第1インバータの出力と第2インバータの入力との間に接続される。第2抵抗は、第2インバータの出力と第1インバータの入力との間に接続される。第1書き込みトランジスタは、第1インバータの出力と接続され、書き込み制御信号の第1セットのソースと接続されるゲートを有する。第2書き込みトランジスタは、第2インバータの出力と接続され、書き込み制御信号の第2セットのソースと接続されるゲートを有する。最後にパストランジスタは第1及び第2インバータのいずれか1つの出力と接続されるゲートを有する。  (もっと読む)

(もっと読む)

ノード・キャパシタンスを増加した半導体メモリ・デバイス

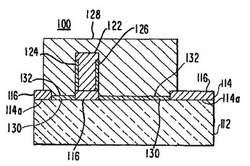

【課題】 ノード・キャパシタンスを増加した半導体メモリ・デバイスを提供することにある。

【解決手段】 集積回路半導体メモリ・デバイス(100)は、ゲートから基板へのキャパシタンスを増加し、それにより、ソフト・エラー率を低減するために、ストレージ・トランジスタのゲートの下に基板(112)の一部分(130)には存在しないBOX層として特徴付けられた第1の誘電体層(116)を有する。第1の誘電体層とは異なる特性を有する第2の誘電体層(132)は、基板のその部分(130)を少なくとも部分的に覆う。このデバイスは、フィン(122)と、ゲートとフィンとの間のゲート誘電体層(124、126)とを含むFinFETデバイスにすることができ、第2の誘電体層はゲート誘電体層より漏れが少ない。

(もっと読む)

セルフタイミング回路を有する半導体メモリ

半導体メモリのセルフタイミング回路(61)において、第1の状態に設定されたセルフタイミング用ダミーメモリセル(SDMC11、12)及び第1の状態と反対の第2の状態に設定された負荷用ダミーメモリセル(LDMC11、12)を有するダミービット線(XDBL1)と、第3の状態に設定されたセルフタイミング用ダミーメモリセル(SDMC21、22)及び前記第3の状態と同一の第4の状態に設定された負荷用ダミーメモリセル(LDMC21、22)を有するダミービット線(XDBL2)と、ダミービット線(XDBL1、XDBL2)の電位の変化速度の差に対応する期間だけ遅延させて、セルフタイミング信号(SLF)を出力するタイミング制御回路(62)とを備える。 (もっと読む)

増大されたセル比を有する6トランジスタFINFET型CMOSスタティックRAMセル

本発明に係るCMOSスタティックRAMセルは、2つのアクセスデバイスであり、各々のアクセスデバイスが単一のフィンを有する3ゲートトランジスタから成るところの2つのアクセスデバイス;2つのプルアップデバイスであり、各々のプルアップデバイスが単一のフィンを有する3ゲートトランジスタから成るところの2つのプルアップデバイス;及び2つのプルダウンデバイスであり、各々のプルダウンデバイスが複数のフィンを有する3ゲートトランジスタから成るところの2つのプルダウンデバイスを有する。さらに、2つのフィンを有する3ゲートトランジスタを備えたCMOSスタティックRAMセルの製造方法が提供される。  (もっと読む)

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

SRAMセル構造及び回路

デバイスの漏れ電流の低減及び/又は速度の増大のためのSRAM回路構造に関する。

様々な形式のSRAMデバイスがシングルポート及びデュアルポートRAMデバイスのような技術を用いて製造されうる。一例として、SRAM構造は、別個の書き込み及び読み込みラインを使用し、回路を異なる閾値レベルを有することで利点を有しうる部分に分け、第一の端子及びソーストランジスタに接続された仮想ノードへの接続のための読み込み経路トランジスタを分けることを実現することができる。構造は、NMOS又はPMOSの組合せ又はNMOSのみでトランジスタを形成するのに特に良く適する。メモリ配列は、本発明により、基準読み込み経路及び検知ブロックが共有又は専用であると共に、多様な分割又は統合を成された配置で編成されても良い。  (もっと読む)

(もっと読む)

小さいフットプリントおよび効率的なレイアウトアスペクト比を有するターナリ検索機能付きメモリ(TCAM)セル

スケーラビリティを高める効率的なレイアウトアスペクト比および極めて小さいレイアウトフットプリントサイズを有するターナリCAMセルが提供される。また、セルは、ビット線、データ線、マッチ線に対する高い歩留りの相互接続を容易にする高度の対称性も有している。16TターナリCAMセルは、セルの第1の側に隣接して延びる第1および第2の対のアクセストランジスタと、セルの第2の側に隣接して延びる第1および第2の対の交差結合インバータとを有している。また、4T比較回路の第1及び第2の半分部位も設けられている。4T比較回路の第1の半分部位は、第1の対のアクセストランジスタと第1の対の交差結合インバータとの間で延びるように位置されている。同様に、4T比較回路の第2の半分部位は、第2の対のアクセストランジスタと第2の対の交差結合インバータとの間で延びるように位置されている。

(もっと読む)

(もっと読む)

並列相補型FinFETの対を有する集積回路構造体及び該形成方法

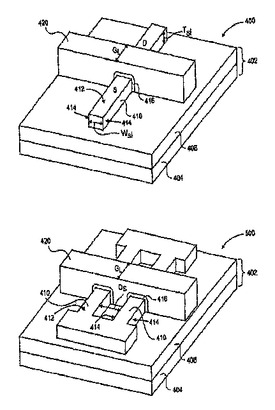

【課題】 従来の単一のFinFETのスペースに2またはそれ以上のFinFETを形成すること。

【解決手段】 相補的フィン型電界効果トランジスタ(FinFET)を用いる集積回路構造体のための方法および構造体を開示する。本発明は、第1フィン(100)を含む第1型FinFETと、第1フィン(100)に並列に延在する第2フィン(102)を含む第2型FinFETを含む。また、本発明は、第1型FinFETおよび第2型FinFETのソース/ドレイン領域(130)の間に配置される絶縁体フィンを含む。第1型FinFETと第2型FinFETとの間隔が1個のフィンの幅とほぼ等しくなるように、絶縁体フィンは、第1フィン(100)および第2フィン(102)とほぼ同じ寸法の幅にされる。また、本発明は、第1型FinFETおよび第2型FinFETのチャネル領域を覆うように形成された共通ゲート(106)を含む。ゲート(106)は、第1型FinFETに隣接する第1不純物ドーピング領域と、第2型FinFETに隣接する第2不純物ドーピング領域とを含む。第1不純物ドーピング領域と第2不純物ドーピング領域の差異が、ゲートに、第1型FinFETと第2型FinFETとの差異に関係した異なる仕事関数を与える。第1フィン(100)および第2フィン(102)はほぼ同じ幅である。

(もっと読む)

半導体装置及びその製造方法

【課題】 より優れたソフトエラー耐性を有するSOI基板を用いた高信頼性のCMOS・SRAMセルを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 SOI基板の表面半導体層上にゲート絶縁膜を介して形成されたゲート電極と、該ゲート電極の両側の表面半導体層に形成された第1導電型ソース/ドレイン領域とから構成される半導体装置であって、前記第1導電型ソース/ドレイン領域の双方又は一方に接して第2導電型引出拡散層が形成され、少なくとも前記第1導電型ソース/ドレイン領域上から第2導電型引出拡散層上にわたってシリサイド層が形成されており、シリサイド層に接地電位が与えられてなる半導体装置。

(もっと読む)

多層配線構造の形成方法

【課題】 第1層の配線上に層間絶縁膜を介して第2層の配線を形成する際、層間絶縁膜に平坦化膜を用いることなく、欠陥のない第2層の配線を形成する、多層配線構造の形成方法を提供する。

【解決手段】 本方法は、半導体基板上に多層配線構造を形成するにあたり、基板面に沿って配線中間に配線を物理的に断絶してなる間隙部60を有する第1層の配線6上に層間絶縁膜を介して第2層の配線層を堆積し、パターニングして第2層の配線を形成する際、層間絶縁膜として、下層が酸化膜とは異なる絶縁膜、例えばSi3 N4 膜8、上層が酸化膜9からなる2層の積層膜を基板上に成膜する工程と、上層の酸化膜にライトエッチングを施して、第1層の配線間の間隙部に形成された層間絶縁膜のスリット状凹部を拡開するライトエッチング工程とを有する。

(もっと読む)

841 - 850 / 855

[ Back to top ]