国際特許分類[H01L27/146]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 赤外線,可視光,短波長の電磁波または粒子線輻射に感応する半導体構成部品で,これらの輻射線エネルギーを電気的エネルギーに変換するかこれらの輻射線によって電気的エネルギーを制御するかのどちらかに特に適用されるもの (11,270) | 輻射線によって制御される装置 (6,258) | 固体撮像装置構造 (6,131)

国際特許分類[H01L27/146]の下位に属する分類

電荷結合型固体撮像装置 (1,522)

国際特許分類[H01L27/146]に分類される特許

31 - 40 / 4,609

撮像装置

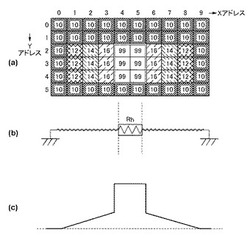

【課題】CMOS型イメージセンサを用いた撮像装置において、高輝度光が入射したときの横筋状又は横帯状のノイズの発生を抑制する。

【解決手段】複数の画素が二次元に配列され、光を受光する開口画素領域と、基準となる遮光されたオプティカルブラック領域とを含むCMOS型の撮像素子と、撮像素子の開口画素領域の特定の領域が高輝度被写体からの光を受光している場合の撮像素子の出力から得られる情報を予め記憶する記憶部と、開口画素領域の特定の領域が高輝度被写体からの光を受光しているか否かを判定する判定部と、判定部により特定の領域が高輝度被写体からの光を受光していると判定された場合に、記憶部に記憶された情報に基づいて、撮像素子からの出力を補正する補正部とを備える。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体膜、ゲート絶縁膜、及び側面に側壁絶縁層が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び側壁絶縁層に接して設けられる。該半導体装置の作製工程において、酸化物半導体膜、側壁絶縁層、及びゲート電極層上を覆うように導電膜及び層間絶縁膜を積層し、化学的機械研磨法によりゲート電極層上の層間絶縁膜及び導電膜を除去してソース電極層及びドレイン電極層を形成する。

(もっと読む)

撮像装置

【課題】 光電変換部の飽和電荷量が増大した場合にも、光電変換部の後段に設けられた読み出し回路のダイナミックレンジに制限を受けることなく信号を読み出すことを目的とする。

【解決手段】 本発明は、光電変換部と、フローティングディフュージョンと、電荷保持部と、前記光電変換部で生じた後、前記電荷保持部で保持された電荷を前記フローティングディフュージョンへ転送する転送トランジスタと、を有する複数の画素と、を有し、前記転送トランジスタには、前記転送トランジスタが導通状態となる導通パルスと、前記転送トランジスタが非導通状態となる非導通パルスと、前記導通パルスと非導通パルスとの間の波高値を有する中間レベルパルスとが、選択的に供給されることを特徴とする。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ別のマスクを用いた別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、ソース電極層またはドレイン電極層は、開口を埋め込むように絶縁層上に導電膜を形成し、絶縁層上の導電膜を化学的機械研磨処理によって除去することで形成される。

(もっと読む)

電磁波検出素子

【課題】センサ部での光の利用効率の低下を防止することができる電磁波検出素子を提供する。

【解決手段】互いに交差して配設された複数の走査配線及び複数の信号配線の各交差部と、2次元状に配列された複数のセンサ部であって、各々が、検出対象とする画像を示す電磁波が照射されることにより電荷が発生する半導体層、半導体層の電磁波が照射される照射面側に電磁波に対して透過性を有する導電性部材により形成され、半導体層に対してバイアス電圧を印加する第1電極、及び半導体層の電磁波に対する非照射面側に形成され、半導体層に発生した電荷を収集する第2電極を備えた複数のセンサ部と、センサ部よりも電磁波の下流側に形成され、各々コンタクトホールを介して第1電極に接続されてバイアス電圧を供給する共通電極配線と、走査配線と、信号配線及び共通電極配線との間に形成されている第1の絶縁膜と、を備え、信号配線及び共通電極配線は同層に形成。

(もっと読む)

走査回路、固体撮像装置およびカメラ

【課題】構成の単純化およびモードの多様化に有利な技術を提供する。

【解決手段】走査回路は複数の単位回路を直列に接続して構成されたシフトレジスタと、シフトレジスタを制御する制御部とを備える。各単位回路はパルス信号入力端子と、パルス信号出力端子と、制御端子とを含む。単位回路は複数にグループ分けされている。制御部は、第1モードでは複数のグループの単位回路の制御端子にクロック信号を供給することによりパルス信号をシフトするように動作させ、第2モードでは少なくとも1つのグループの単位回路の制御端子にはバッファとして動作させる論理レベルを供給し、他のグループの単位回路の制御端子にはクロック信号を供給することにより前段の単位回路から出力されるパルス信号をクロック信号に応じて後段の単位回路に転送するように動作させ、1つの期間内に少なくとも1つのグループの単位回路とその前段の単位回路からパルス信号を出力させる。

(もっと読む)

固体撮像素子、固体撮像素子の製造方法、及び、電子機器

【課題】グローバルシャッタ機能を有し、白点及び暗電流の抑制が可能な固体撮像素子を提供する。

【解決手段】

半導体基体31と、半導体基体31に形成されているフォトダイオード32と、フォトダイオード32に蓄積された信号電荷が転送される浮遊拡散領域35とを備える。さらに、半導体基体31内において浮遊拡散領域35を覆う半導体基体面と平行な水平遮光部32Aと、半導体基体31面と垂直な垂直遮光部32Bとからなる遮光層32とを備える固体撮像素子30を構成する。

(もっと読む)

焦電型光検出器、焦電型光検出装置および電子機器

【課題】焦電型光検出器の検出出力を高めること。

【解決手段】焦電型光検出器は、基板10と、基板上に支持される支持部材215と、支持部材に接して形成されている焦電型光検出素子251と、を有する。焦電型光検出素子251は、支持部材側に設けられる第1電極234と、第1電極と対向して設けられ、平面視における面積が、第1電極より小さい第2電極236と、第1電極234と第2電極236との間に設けられる焦電体232と、を含むキャパシター230を有する。焦電型光検出素子251はさらに、キャパシター上に形成されている光吸収層270を含む。平面視における光吸収層の面積を受光部面積Aaとし、平面視における第2電極の面積をキャパシター面積Acとし、Aa/Acは、2.0<Aa/Ac<49.0を満足する。

(もっと読む)

固体撮像装置、撮像装置、および信号読み出し方法

【課題】複数の基板の面積を有効に活用する。

【解決手段】本発明の一態様に係る固体撮像装置は、第1〜第n(nは2以上の整数)の基板どうしが接続部を介して電気的に接続された固体撮像装置であって、光電変換素子を含む画素が行列状に配置された画素部と、前記画素部内の画素の列に対応して配置され、対応する列の画素に含まれる前記光電変換素子で発生した信号を信号処理する複数の列処理回路を含む列回路部と、前記列処理回路によって信号処理された信号を当該装置の外部に出力する出力部と、を備え、前記第1の基板に前記画素部が配置され、前記第1〜第nの基板のうち少なくとも2以上の異なる基板のそれぞれに前記列回路部が配置され、前記画素部内の各列の画素に対応する信号処理を、前記少なくとも2以上の異なる基板のそれぞれに配置された前記列回路部で分散して行うことを特徴とする。

(もっと読む)

分子検出および識別に応用する多接合フォトダイオード、およびその製造方法

【課題】分子検出および識別に応用する多接合フォトダイオードおよびその製造方法を提供する。

【解決手段】多接合フォトダイオードは、第1導電型ドーパントを有する基板と、第1導電型ドーパントを有するエピタキシー層と、第2導電型ドーパントを有する深ウェル領域と、第1導電型ドーパントを有する第1ウェル領域と、第2導電型ドーパントを有する第2ウェル領域と、第1導電型ドーパントを有する第3ウェル領域と、第2導電型ドーパントを有する第1ドープ領域とを含む半導体装置を提供する。エピタキシー層は、基板の上に配置され、深ウェル領域は、エピタキシー層の中に配置される。第1ウェル領域は、エピタキシー層に接続された3つの側辺を有し、深ウェル領域の中に配置される。第2ウェル領域は、第1ウェル領域の中に配置される。第3ウェル領域は、エピタキシー層に接続された3つの側辺を有し、第2ウェル領域の中に配置される。第1ドープ領域は、第3ウェル領域の中に配置される。

(もっと読む)

31 - 40 / 4,609

[ Back to top ]