国際特許分類[H01L29/74]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | バイポーラ装置 (2,586) | サイリスタ型装置,例.4層再生作用をもつもの (302)

国際特許分類[H01L29/74]の下位に属する分類

ゲートターンオフサイリスタ (51)

双方向サイリスタ,例.トライアック (21)

電界効果によりターンオンするもの (39)

国際特許分類[H01L29/74]に分類される特許

81 - 90 / 191

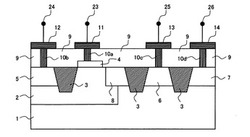

静電気放電保護装置及びこれを備えた半導体集積回路

【課題】 レイアウトサイズを縮小可能で、静電気放電による過電流流入時に半導体集積回路への過電圧印加を低いターンオン電圧で抑制可能なサイリスタ構造の静電気保護装置を提供する。

【解決手段】 第1導電型の半導体基板1と、第2導電型のウェル2と、半導体基板表面に形成される第2導電型でウェルより高不純物濃度のカソード及びアノードの一方となる第1不純物領域6と、半導体基板表面に形成される第1導電型で半導体基板より高不純物濃度の第1コンタクト不純物領域7と、ウェル表面上においてウェル表面に接して形成される第1導電型でカソード及びアノードの他方となる第2不純物領域4と、ウェル表面に形成される第2導電型でウェルより高不純物濃度の第2コンタクト不純物領域5と、半導体基板とウェルの境界領域の半導体基板表面とウェル表面の両方に跨って形成される第2導電型でウェルより高不純物濃度の境界不純物領域8を備える。

(もっと読む)

静電気保護回路及びそれを備えた半導体装置

【課題】新たな素子を追加することなく、基本的な構成のSCR素子のみで、高いSCRトリガー電流をもつSCR素子を備えた静電気保護回路を提供する。

【解決手段】PNPバイポーラトランジスタ7のエミッタとベースがアノード端子5に、コレクタがNPNバイポーラトランジスタ8のベースに接続されている。NPNバイポーラトランジス8タのエミッタがカソード端子6に、ベースが第1抵抗R1を介してカソード端子6に、コレクタが第2抵抗R2を介してPNPバイポーラトランジスタ7のベースに接続されている。

(もっと読む)

半導体を用いた電子デバイス

【課題】高耐圧電子デバイスおよび耐環境電子デバイスを提供する。

【解決手段】本発明においては、ダイオードやトランジスタ等の電子デバイス中で電子が走行する領域に、高純度の酸化モリブデンであって、その禁制帯幅が3.45eV以上であるような酸化モリブデンが用いられる。本発明によれば、高耐圧特性および高耐環境特性を有する電子デバイスが実現できる。

(もっと読む)

高速トリガーESD保護デバイスおよびその設計方法

【課題】ICに現れるオーバーシュートが低減可能なESD保護デバイス、およびその設計方法の提供。

【解決手段】主ESDデバイス10と、低減された電圧で、ESD電流を流すために、主ESDデバイスのトリガーノードに接続されたトリガーデバイス20とを含むESD保護回路の設計方法。このトリガーデバイス20は、ESD電流のための最初の電流経路中に配置される。この最初の電流経路中に、オフ状態からオン状態にトリガーされる少なくとも1つのトリガー要素を有する。この要素のトリガー速度が考慮され、その設計はそのトリガー速度が増加するように最適化される。更に、少なくとも1つのトリガー要素が、速いトリガー速度を得るために、所定のタイプ、好適にはゲート型ダイオードタイプから選択されESD保護回路。

(もっと読む)

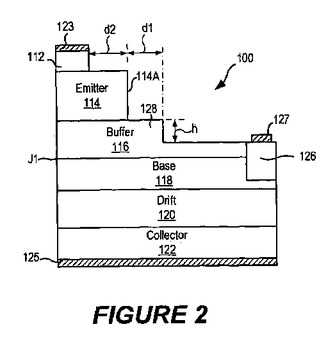

メサ構造とメサ段差を含むバッファ層とを備えた電力半導体デバイス

バイポーラ接合トランジスタが、第1の導電型を有するコレクタと、このコレクタ上の、第1の導電型を有するドリフト層と、このドリフト層上の、第1の導電型と反対の第2の導電型を有するベース層と、このベース層上の、低濃度でドープされ第1の導電型を有しベース層とp−n接合部を形成するバッファ層と、このバッファ層上の第1の導電型を有し側壁を有するエミッタメサとを含む。バッファ層は、エミッタメサの側壁の近傍でそこから横方向に間隔を置いて配置されたメサ段差を含み、エミッタメサの下のバッファ層の第1の厚さは、メサ段差外側のバッファ層の第2の厚さよりも厚い。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】実効的なエピタキシャル成長面積を拡大して、エピタキシャル成長時に発生するファセットの影響を抑えることを可能とする。

【解決手段】第1p型領域p1と、第1n型領域n1と、第2p型領域p2と、第2n型領域n2とが順に接合された第1サイリスタT1と第2サイリスタT2とが素子分離領域14で分離された状態に形成された半導体装置1であって、第1、第2サイリスタT1、T2の第1n型領域n1が素子分離領域14を挟んで設けられ、各第1n型領域n1上に選択エピタキシャル成長により形成される第1、第2サイリスタT1、T2の各第1p型領域p1が、各第1n型領域n1間の素子分離領域14上で連続した状態に形成されていることを特徴とする。

(もっと読む)

逆阻止3端子サイリスタ

【課題】逆阻止3端子サイリスタの誤動作耐量の向上が要求されている。

【解決手段】逆阻止3端子サイリスタを構成するための半導体基体1は第1、第2及び第3のN型半導体領域N1、N2、N3と第1及び第2のP形半導体領域P1、P2とを有する。半導体基体1の一方の主面2側から他方の主面3に向って第1のP型半導体領域P1、第1のN型半導体領域N1、第2のP型半導体領域P2、第2のN型半導体領域N2が順次に配置されている。第3のN型半導体領域N3は半導体基体1の一方の主面2に配置されている。第1の主電極T1は第1のP型半導体領域P1及び第3のN型半導体領域N3に接続され、第2の主電極T2は第2のP型半導体領域P2及び第2のN型半導体領域N2に接続され、ゲ−ト電極Gは第1のP型半導体領域P1に接続されている。

(もっと読む)

バイアス抵抗をコレクタ極とベース極間に、トランジスタ縦続接続UJTを用いたゲート回路をベース極とゲート極間に側路接続したトランジスタ縦続接続サイリスタ高周波半導体素子

【課題】 直流電圧を遮断して突入電流を流し、電流・電圧回路を形成して、高周波接続容量回路を構成し、完全なスイッチ機能を計り電力供給する高周波半導体を提供する。

【解決手段】バイアス抵抗R1,R2を接続しトランジスタ縦続接続UJTゲート回路を側路接続したトランジスタ縦続接続サイリスタ素子の接続容量が直流電圧を遮断し、順方向漏れ電流を流して電界を形成すると、突入電流がゲート電極Gの接合面に電位の溝をつくりゲート漏れ電流を流し、接続容量回路を構成して接続容量に応じて直流電力を供給する高周波半導体素子を得る。

(もっと読む)

サイリスタ

【課題】高いゲート・カソード間耐圧を有するサイリスタを提供する。

【解決手段】第1導電型の半導体基板の第1主面には、第1導電型の不純物領域であるカソード領域と、前記カソード領域を取り囲むような第2導電型の不純物領域であるアノード領域と、前記カソード領域と前記アノード領域との間にはメサ溝部とを有し、前記半導体基板の第2主面には、第2導電型の不純物領域部であるゲート領域と、前記第1主面から前記ゲート領域まで達する深さの前記メサ溝部と、前記第1主面の前記カソード領域にはカソード金属電極、前記アノード領域にはアノード金属電極を有し、前記第2主面の前記ゲート領域上にはゲート金属電極を有することを特徴とするサイリスタであり、ゲート・カソード間距離が充分に確保できる構造であるため、ゲート・カソード間耐圧を高く確保することができる。

(もっと読む)

バイポーラ素子及びその製造方法

【課題】メサ型バイポーラトランジスタあるいはサイリスタでは、エミッタ層あるいはアノード層からベース層あるいはゲート層に注入されたキャリアが横方向に拡散し再結合する結果、小型化やスイッチング周波数の向上が困難であった。

【解決手段】エミッタ層あるいはアノード層を高濃度および低濃度からなる二層で構成し、この低濃度層と同一の不純物密度を有する同一の半導体からなる再結合抑制半導体領域をベース層またはゲート層と表面保護絶縁膜とに接して存在させるとともに、この再結合抑制半導体領域の幅をキャリアの拡散距離以上に設定する。このことにより、バイポーラトランジスタの小型化やサイリスタのスイッチング周波数向上を、性能を損なわず実現できる効果がある。また、上記バイポーラトランジスタの高濃度エミッタ層上に、正孔バリア層、伝導帯不連続緩和層、及びエミッタコンタクト層を順次積層することにより、電流増幅率を大幅に向上できる効果がある。

(もっと読む)

81 - 90 / 191

[ Back to top ]