国際特許分類[H01L29/74]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | バイポーラ装置 (2,586) | サイリスタ型装置,例.4層再生作用をもつもの (302)

国際特許分類[H01L29/74]の下位に属する分類

ゲートターンオフサイリスタ (51)

双方向サイリスタ,例.トライアック (21)

電界効果によりターンオンするもの (39)

国際特許分類[H01L29/74]に分類される特許

61 - 70 / 191

低角度オフカット炭化ケイ素結晶上の安定なパワーデバイス

【課題】炭化ケイ素中の結晶欠陥を低減することができるプロセスならびにその結果得られる構造体およびデバイスを提供すること。

【解決手段】炭化ケイ素ベースのパワーデバイスが、<0001>方向に対して8°よりも小さいオフアクシス角を形成する平坦な表面を有する炭化ケイ素ドリフト層を含む。

(もっと読む)

電流シフト領域を有する半導体デバイスおよび関連方法

半導体デバイスは、第1の伝導形を有する半導体バッファ層と、バッファ層の表面上にあって第1の伝導形を有する半導体メサとを含む。さらに第2の伝導形を有する電流シフト領域が半導体メサと半導体バッファ層との間の隅に隣接して設けられ、第1と第2の伝導形が互いに異なる伝導形である。関連する方法も開示される。  (もっと読む)

(もっと読む)

III族窒化物系化合物半導体素子及びその製造方法

【課題】積層された各層に平面的に電極が形成された、III族窒化物系化合物半導体素子

【解決手段】pnpトランジスタ100は、基板10の上に、図示しないバッファ層を介して、p型GaN層11、n型GaN層12、p型GaN層13を順に形成した後、ケミカルポリシングにより露出部である傾斜面11t、12t及び13tを形成し、そこに各々、コレクタ電極C、ベース電極B、エミッタ電極Eを形成して構成したものである。図1のpnp型トランジスタ100は、水平形状が1辺が500μmの矩形状で、その外周の1辺に水平面と10度の角度を成す傾斜面が形成されている。p型GaN層11、n型GaN層12及びp型GaN層13の膜厚はいずれも1μmであり、p型GaN層11の傾斜面11t、n型GaN層12の傾斜面12t及びp型GaN層13の傾斜面13tの幅はいずれも約5.8μmである。

(もっと読む)

点滅回路

【課題】消費電力を少なくするとともに、部品点数を少なくすることで低コスト化を図った点滅回路を提供することを目的とする。

【解決手段】発光サイリスタ20の第1端子であるアノード端子は、抵抗13を介して電源VDDに接続するとともにコンデンサ15を介してグランドに接続し、第2端子であるカソード端子は抵抗14を介してグランドに接続し、第3端子であるゲート端子は抵抗11と抵抗12の直列回路の接続中心に接続する。

(もっと読む)

静電気保護素子

【課題】表示パネル駆動用の半導体集積装置に適した、保持電圧が高い静電保護素子を提供する。

【解決手段】静電保護素子は、P型半導体基板1の表面側に形成されたNウェル領域2と、Nウェル領域の上に形成された第1のP型高濃度不純物領域8と、P型半導体基板の表面上に形成されたN型高濃度不純物領域5と、Nウェル領域とP型半導体基板1との境界を跨いでNウェル領域と前記P型半導体基板との双方に接触して形成された第2のP型高濃度不純物領域6とを備えている。すなわち、第2のP型高濃度不純物領域6がP型半導体基板1と接触するため、P型半導体基板1におけるP型不純物の濃度が高くなり、従って静電気保護素子の保持電圧が高くなる。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コストを抑えつつ、ガードリングに接するPN接合部の耐圧の向上を図る。

【解決手段】半導体基板10の表面にN−型半導体層11を形成し、その上層にP型半導体層12を形成する。P型半導体層12上には、絶縁膜13を形成する。その後、絶縁膜13からN−型半導体層11の厚さ方向の途中に至る複数の溝、即ち第1の溝17A、第2の溝17B、第3の溝17Cを形成する。これらの複数の溝は、そのうち互いに隣接する2つの溝において、電子デバイスに近い側、即ちアノード電極14に近い側の溝は、該溝よりも外側の他方の溝よりも浅く形成される。その後、第1の溝17A内、第2の溝17B内、第3の溝17C内に、絶縁材料18が充填される。その後、半導体基板10及びその上層に積層された各層からなる積層体をダイシングラインDLに沿ってダイシングする。

(もっと読む)

バイポーラ型半導体装置

【課題】表面欠陥に起因する積層欠陥が生じても、リーク電流を低減でき、最小点弧電流の増大を防止できるバイポーラ型半導体装置を提供する。

【解決手段】n型の半導体基板とその半導体基板上にエピタキシャル成長により順に形成された複数の半導体層とを備えたシリコンカーバイト(SiC)を母材とする主構造体1と、上記主構造体1の半導体層の最上層に形成され、半導体基板のオフ方向に対してストライプ方向(矢印R1)が略直交するメサストライプ部2と、上記メサストライプ部2のメサ2a上に形成されたアノード電極3と、上記半導体基板の裏面に形成されたカソード電極5と、上記メサストライプ部2のメサ2a間に露出する半導体層上に形成されたゲート電極4とを備える。

(もっと読む)

半導体装置

【課題】高耐圧と速い動作とを共に実現することが可能な半導体装置を提供する。

【解決手段】N型基板1上に形成されたN型の半導体層2と、この半導体層2の表面に形成されたP型の第1拡散層4と、半導体層2の表面に、第1拡散層4と互いに離間し、かつ、第1拡散層4を囲むように形成された、P型の第2拡散層4と、第1拡散層4の表面に形成された、P型の第3拡散層5と、第2拡散層4の表面に形成された、P型の第4拡散層7と、第1拡散層4の表面に形成され、第3拡散層5と電気的に接続された、N型の第5拡散層6と、第2拡散層4の表面と半導体層2の表面とをまたぐように形成され、第4拡散層7と電気的に接続された、N型の第6拡散層8とを含む、PN接合型ダイオードを有する半導体装置を構成する。

(もっと読む)

静電気保護素子

【課題】特殊な工程や、保護抵抗の挿入なしに被保護回路を保護できる静電気保護素子を提供する。

【解決手段】P型の半導体基板1と、半導体基板1に形成された、N型の第1不純物層3を備える。第1不純物層3内には、ゲートとして動作するP型の第2不純物層5を備える。第2不純物層5には、カソードとして動作するN型の第3不純物層6を備える。また、第2不純物層5から一定距離離間した第1不純物層3内には、N型の第4不純物層4を備える。第4不純物層4内には、アノードとして動作するP型の第5不純物層8と、N型の第6不純物層9とを備える。そして、本静電気保護素子は、第4不純物層4の不純物濃度が第1不純物層3の不純物濃度よりも高く、かつ第4不純物層4の底部が第2不純物層5の底部より深くなっている。

(もっと読む)

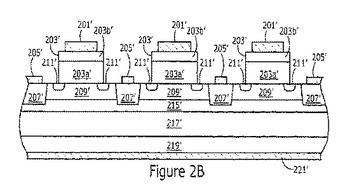

発光素子チップ、露光装置および画像形成装置

【課題】本発明は、発光素子アレイの構造を利用して信号線の引き回しの複雑化を軽減した発光素子チップを提供する。

【解決手段】発光素子チップ51aは、GaAs系の半導体で構成され、基板200上に形成されたpnpn構造からなる、発光部120の発光サイリスタ401と、設定部130の転送サイリスタ402と、制御部140の論理演算素子403とを備え、基板200上にp型の第1半導体層201とn型の第2半導体層202と、p型の第3半導体層203と、n型の第4半導体層204とを積層し、その後、予め定められた箇所をエッチングして形成される。

(もっと読む)

61 - 70 / 191

[ Back to top ]