国際特許分類[H01L45/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 電位障壁または表面障壁をもたず,整流,増幅,発振またはスイッチングに特に適用される固体装置,例.誘電体三極素子;オブシンスキー効果装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,392)

国際特許分類[H01L45/00]の下位に属する分類

固体進行波装置

国際特許分類[H01L45/00]に分類される特許

111 - 120 / 1,392

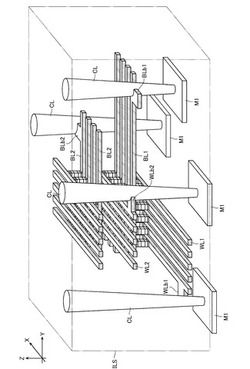

半導体記憶装置の製造方法

【課題】クロスポイント型セル構造の配線構造を正確に形成する。

【解決手段】

第1の配線を形成する第1配線層及びメモリセルを形成するメモリセル層を順次積層してなる第1積層構造を第1方向に延びるストライプ状にエッチングする。このとき、第1ストライプ部の側部から第2方向に突出する第1フック部を形成する。そして、第1積層構造の上層に第2積層構造を形成し、この第2積層構造を2方向に延びるストライプ状にエッチングする。このとき、第2ストライプ部の側部から第1方向に突出する第2フック部を形成する。上記を所定数繰り返す。そして、第1又は第2フックの側面に接するコンタクトプラグを形成する。第2フック部が形成されるべき領域では、第1積層構造を除去し、また、第1フック部が形成されるべき領域では、第2積層構造を除去する。

(もっと読む)

不揮発性抵抗変化素子

【課題】抵抗を可逆的に変化させことを可能としつつ、データ保持特性を向上させる不揮発性抵抗変化素子を提供する。

【解決手段】第1電極1と、第2電極3と、可変抵抗層2とを備え、第2電極3は、Al元素が添加された1B族元素を有し、可変抵抗層2は、第1電極1と第2電極3との間に配置され、シリコン元素を有する。可変抵抗層2は非晶質シリコン層であってもよいし、多結晶シリコン層であってもよいし、単結晶シリコン層であってもよい。第1電極1は不純物ドープシリコンおよびTi、Ni、Co、Fe、Cr、Cu、W、Hf、Ta、Pt、Ru、ZrまたはIrや、その窒化物あるいは炭化物あるいはカルコゲナイド材料などを用いることができる。

(もっと読む)

抵抗変化素子の制御方法、および、半導体装置

【課題】抵抗変化素子の閾値電圧のばらつきを生じさせることなく、閾値電圧を低電圧化すること。

【解決手段】印加されたパルス電圧の極性に応じて抵抗値の異なる第1の状態と第2の状態との間で遷移する抵抗変化層と、抵抗変化層の一端に接続された第1の電極と、他端に接続された第2の電極とを備えた抵抗変化素子の制御方法であって、抵抗変化層を第1の状態から前記第2の状態へ遷移させる第1の極性とは逆の第2の極性を有する第1のパルス電圧を、抵抗変化層を第1の状態に保ちつつ、両電極間に印加した後、第1の極性を有する第2のパルス電圧を両電極間に印加して、抵抗変化層を第1の状態から第2の状態へ遷移させる。

(もっと読む)

不揮発性記憶装置

【課題】高密度・高信頼の不揮発性記憶装置を実現する

【解決手段】基板の主面に沿って延在するワード線2上に交互に積層された層間絶縁膜11〜15およびゲートポリシリコン層21p〜24pを含む積層体と、積層体上に形成され、ワード線2と直交して延在するビット線3と、ワード線2およびビット線3の交点に設けられたポリシリコンダイオードPDとを有する不揮発性半導体装置を形成する。積層体を貫通してポリシリコンダイオードPDの上面を露出する接続孔の内壁には、前記内壁側から順にゲート絶縁膜9、チャネルシリコン膜8a、8bおよび抵抗変化材料層7を設ける。ワード線2とビット線3とはポリシリコンダイオードPD、チャネルシリコン膜8aおよび8bを介して電気的に接続し、前記内壁に垂直な方向におけるチャネルシリコン膜8a、8bの合計の膜厚は、チャネルシリコン膜8a、8bを空乏化することができる膜厚とする。

(もっと読む)

不揮発性記憶装置

【課題】低コストで量産性に優れた不揮発性記憶装置を提供する。

【解決手段】実施形態の不揮発性記憶装置は、下側電極膜と、前記下側電極膜の上に設けられ、第1酸化物を含有する第1記憶素子膜と、前記第1記憶素子膜の上に設けられた上側電極膜と、を有する第1状態と、もしくは、前記下側電極膜と、前記下側電極膜の上に設けられた前記第1記憶素子膜と、前記第1記憶素子膜の上に設けられ、第2酸化物を含有する第2記憶素子膜と、前記第2記憶素子膜の上に設けられた前記上側電極膜と、を有する第2状態と、を維持することが可能である。前記第2記憶素子膜に含まれる酸素濃度は、前記第1記憶素子膜に含まれる酸素濃度よりも高い。前記第2状態における前記下側電極膜と前記上側電極膜との間の抵抗は、前記第1状態における前記下側電極膜と前記上側電極膜との間の抵抗よりも高い。

(もっと読む)

可変抵抗素子のフォーミング処理方法および不揮発性半導体記憶装置

【課題】 パルスフォーミングと同程度の短時間で、スイッチング動作時の書き換え電流がDCフォーミングで達成される書き換え電流程度に抑えることのできる可変抵抗素子のフォーミング処理方法を提供する。

【解決手段】

可変抵抗素子に電圧パルスを印加して、製造直後の初期高抵抗状態にある可変抵抗素子をスイッチング動作が可能な可変抵抗状態に変化させるフォーミング処理が、可変抵抗素子が低抵抗化する閾値電圧より低い電圧振幅の第1パルスを可変抵抗素子の両電極間に印加する第1ステップと、第1ステップの後に、当該第1パルスと同極性であって閾値電圧以上の電圧振幅の第2パルスを可変抵抗素子の両電極間に印加する第2ステップとを含んでなる。

(もっと読む)

不揮発性記憶素子及びその製造方法並びに不揮発性記憶装置

【課題】不揮発性記憶素子の初期化電圧のばらつきの発生を抑えつつ、従来に比べて初期化電圧の低減を図ることができる抵抗変化型の不揮発性記憶素子を提供する。

【解決手段】第1の層間絶縁層102、下部電極105、上部電極107及び抵抗変化領域106を備え、抵抗変化領域106は積層された第1の抵抗変化領域106bと第2の抵抗変化領域106aを有し、第1の抵抗変化領域106bは第1の遷移金属酸化物で構成され、第2の抵抗変化領域106aは第2の遷移金属酸化物で構成され、第2の遷移金属酸化物の酸素不足度は第1の遷移金属酸化物の酸素不足度より小さく、抵抗変化領域106の上面は上部電極107と接し、抵抗変化領域106の底面は下部電極105及び第1の層間絶縁層102と接し、抵抗変化領域106の底面と下部電極105の接する面の面積は抵抗変化領域106の上面と上部電極107の接する面の面積より小さい。

(もっと読む)

半導体記憶装置

【課題】ジュール熱を利用して情報を記憶する相変化メモリを採用した半導体記憶装置において、誤ライト動作を起こす可能性を抑制する。

【解決手段】本発明に係る半導体記憶装置は、積層体内のいずれかの半導体層に第1の電流を印加して積層体内の複数の半導体層の側面に配置されている抵抗変化材料層を一括して結晶化した後、第1の電流を印加した半導体層以外の半導体層に第2の電流を印加する。

(もっと読む)

混合原子価導電性酸化物を用いたメモリ

【課題】混合原子価導電性酸化物を用いたメモリを提供する。

【解決手段】酸化されていない状態で導電性を有し、酸素欠乏状態で導電性が下がる混合原子価導電性酸化物酸素リザーバ635と、酸素に対する電解質であり、酸素イオンの移動を引き起こすのに有効な電場を促進する電解質トンネル障壁505と、を備える。

(もっと読む)

非揮発性メモリ装置及びセンシング方法

【課題】抵抗変化を利用したマルチレベルのデータをセンシングする非揮発性メモリ装置において、読出し動作の回数を減らし、読出し動作の制御に係わる回路の面積を縮小する。

【解決手段】非揮発性メモリ装置は、1つ以上の単位セルを含んでデータの読出し又は書込みが行なわれるセルアレイと、単位セルに格納されたデータに対応するセンシング電圧SAIと基準電圧REFを比較及び増幅して出力し、ビットラインがプリチャージされた以後にセンシングイネーブル信号SENの活性化区間で、単位セルの抵抗値に応じてセンシング電圧がディスチャージされる時間の差を測定し、データをセンシングするセンシング部100とを含む。

(もっと読む)

111 - 120 / 1,392

[ Back to top ]