国際特許分類[H01L45/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 電位障壁または表面障壁をもたず,整流,増幅,発振またはスイッチングに特に適用される固体装置,例.誘電体三極素子;オブシンスキー効果装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,392)

国際特許分類[H01L45/00]の下位に属する分類

固体進行波装置

国際特許分類[H01L45/00]に分類される特許

131 - 140 / 1,392

半導体装置

【課題】製造時以外にデータの追記が可能であり、書き換えによる偽造等を防止可能な不揮発の記憶装置及びそれを有する半導体装置を提供することを課題とする。また、信頼性が高く、安価な不揮発の記憶装置及び半導体装置の提供を課題とする。

【解決手段】絶縁表面上に形成される第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層に挟持される第1の絶縁層と、第1の導電層の一部を覆う第2の絶縁層とを有し、第1の絶縁層は第1の導電層の端部、絶縁表面、及び第2の絶縁層を覆うことを特徴とする記憶装置である。

(もっと読む)

抵抗変化メモリ

【課題】抵抗変化素子の低抵抗状態の抵抗値のばらつきを防止する。

【解決手段】実施形態に係わる抵抗変化メモリのメモリセルは、直列接続される抵抗変化素子RW及び積層構造Cを備える。抵抗変化素子RWを第1の抵抗値からそれよりも低い第2の抵抗値に変化させる第1の動作において、メモリセルMCに第1の電圧パルスを印加する。第1の電圧パルスの振幅は、積層構造Cがキャパシタとして機能する第1の電圧領域内にあり、第1の電圧パルスは、Ron×C < T-lead < Roff×C、 Ron×C < T-trailを満たす。但し、T-leadは、第1の電圧パルスの立ち上がり時間[sec]であり、T-trailは、第1の電圧パルスの立ち下り時間[sec]であり、Roffは、第1の抵抗値[Ω]であり、Ronは、第2の抵抗値[Ω]であり、Cは、キャパシタの容量[F]である。

(もっと読む)

側壁構造化スイッチャブル抵抗器セル

【課題】抵抗を大きくして感知されやすくするとともに、リセット電流を小さくし、製造中の損傷も抑制できる抵抗率スイッチング素子を提供する。

【解決手段】第1の伝導性電極28を形成するステップと、第1の伝導性電極28の上に絶縁構造13を形成するステップと、絶縁構造の側壁上に抵抗率スイッチング素子14を形成するステップと、抵抗率スイッチング素子14の上に第2の伝導性電極26を形成するステップと、第1の伝導性電極28および第2の伝導性電極26の間に抵抗率スイッチング素子14と直列にステアリング素子を形成するステップと、を含み、第1の伝導性電極28から第2の伝導性電極26への第1の方向における抵抗率スイッチング素子14の高さTは第1の方向に垂直な第2の方向における抵抗率スイッチング素子14の厚さIより大きい。

(もっと読む)

相変化メモリ装置

【課題】本発明は、相変化記録層に対する加熱を効率良く行うことができ、書き込み電流の低減を可能とする相変化メモリ装置を提供する。

【解決手段】ヒータプラグと、前記ヒータプラグと接して設けられた相変化記録層とを含んで構成される記憶素子を備え、前記ヒータプラグ及び前記相変化記録層のうち少なくとも一方の内部に空隙が設けられていることを特徴とする。

(もっと読む)

抵抗変化型不揮発性記憶装置

【課題】メモリセルのトランジスタのサイズを最適化可能とした抵抗変化型不揮発性記憶装置を提供する。

【解決手段】下部電極309aと上部電極309cと両電極間に与えられる極性の異なる電気的信号に基づいて高抵抗状態と低抵抗状態とを可逆的に変化する抵抗変化層309bとからなる抵抗変化素子309と、半導体基板301と2つのN型拡散層領域302a、302bとからなるトランジスタ317とを直列に接続してなるメモリセル300を備え、抵抗変化層309bは酸素不足型の遷移金属の酸化物層からなり、下部電極309aと上部電極309cは、異なる元素からなる材料によって構成され、下部電極309aの標準電極電位V1と上部電極309cの標準電極電位V2と前記遷移金属の標準電極電位VtとがVt<V2かつV1<V2なる関係を満足し、下部電極309aとN型拡散層領域302bとが接続されている。

(もっと読む)

有機分子メモリ

【課題】電荷保持特性に優れた有機分子メモリを提供する。

【解決手段】実施の形態の有機分子メモリは第1の導電層と、第2の導電層と、第1の導電層と第2の導電層との間に設けられ、電荷蓄積型分子鎖または抵抗変化型分子鎖を含み、電荷蓄積型分子鎖または前記抵抗変化型分子鎖が縮合多環系の基を備える有機分子層と、を備えている。

(もっと読む)

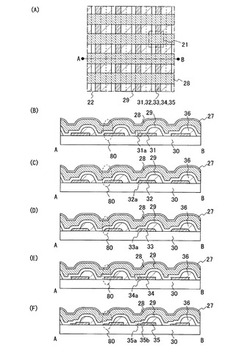

半導体装置の製造方法

【課題】エッチング加工により高アスペクト比の構造体の形成が可能な半導体装置の製造方法を提供すること。

【解決手段】異なる材料からなる複数の膜を積層して少なくとも酸化シリコン膜を含む積層膜を形成する工程と、前記積層膜上にハードマスクパターンを形成する工程と、前記ハードマスクパターンをエッチングマスクに用いて前記積層膜を異方性エッチングして所定の形状の積層膜パターンを形成する工程と、前記ハードマスクパターンを除去する工程と、を含み、前記ハードマスクパターンは、第1ハードマスク層と第2ハードマスク層とが少なくとも1層ずつ以上積層されて構成され、前記第1ハードマスク層は、前記第2ハードマスク層よりもウェットエッチングによる剥離性が良い材料からなり、前記積層膜の直上には前記第1ハードマスク層が配置される。

(もっと読む)

抵抗変化型不揮発性半導体記憶装置

【課題】相変化材料配線、抵抗変化材料配線の書き込み電流(Set、Reset電流)、読み出し電流を大幅に低減し、より微細化を可能にし、メモリセルサイズを縮小することを可能にする抵抗変化型不揮発性半導体記憶装置を提供すること。

【解決手段】カルコゲナイド配線GSTと、両端の各々に接続した抵抗配線と、前記抵抗配線のそれぞれの他端を、ソース、ドレインに接続したセルトランジスタとからメモリセルMCを構成し、前記メモリセルを複数直列接続し、一端を、ソースに接続し、ドレインをビット線に接続した選択トランジスタと、前記複数直列接続の他端をソース線に接続し、前記メモリセルのゲートをワード線に接続し、前記選択トランジスタのゲートとブロック選択線に接続したものからセルストリングを構成し、前記セルストリングを複数配設してメモリセルアレイを構成することを特徴とする相変化メモリ。

(もっと読む)

不揮発性半導体記憶装置

【課題】上側のメモリセルと下側のメモリセルとの間におけるデータリテンションのばらつきを低減できる不揮発性半導体記憶装置を提供する。

【解決手段】第1のメモリセルMC111は、第1のラインWL11の半導体基板SBと反対側に配されている。第2のラインBL11は、第1のメモリセルMC111を介して第1のラインWL11に交差する。第2のメモリセルMC211は、第2のラインBL11の半導体基板SBと反対側に配されている。第3のラインWL21は、第2のメモリセルMC211を介して第2のラインBL11に交差する。第1のメモリセルMC111は、第1の抵抗変化層R111と第1の整流層D111とを有する。第1の抵抗変化層R111は、カーボン系の材料で形成されている。第2のメモリセルMC211は、第2の抵抗変化層R211と第2の整流層D211とを有する。第2の抵抗変化層R211は、金属酸化物で形成されている。

(もっと読む)

半導体記憶装置

【課題】低消費電力且つ省スペースな半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、異なる抵抗状態によってデータを記憶する複数のメモリセルからなるメモリセル層を有するメモリセルアレイと、第1配線及び第2配線を介して前記メモリセルにアクセスするアクセス回路とを備え、メモリセルは、第1極性の所定の電圧が印加されると抵抗状態が第1抵抗状態から第2抵抗状態に遷移し、第2極性の所定の電圧が印加されると抵抗状態が第2抵抗状態から第1抵抗状態に遷移し、アクセス回路は、選択したメモリセルに接続された第1配線及び第2配線に前記メモリセルのアクセスに必要な電圧を印加する共に、非選択の前記メモリセルに接続された第1配線及び第2配線の少なくとも一方をフローティング状態にして、選択したメモリセルにアクセスすることを特徴とする。

(もっと読む)

131 - 140 / 1,392

[ Back to top ]