国際特許分類[H01L45/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 電位障壁または表面障壁をもたず,整流,増幅,発振またはスイッチングに特に適用される固体装置,例.誘電体三極素子;オブシンスキー効果装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,392)

国際特許分類[H01L45/00]の下位に属する分類

固体進行波装置

国際特許分類[H01L45/00]に分類される特許

121 - 130 / 1,392

半導体記憶装置

【課題】ジュール熱を利用して情報を記憶する相変化メモリを採用した半導体記憶装置において、誤ライト動作を起こす可能性を抑制する。

【解決手段】本発明に係る半導体記憶装置は、積層体内のいずれかの半導体層に第1の電流を印加して積層体内の複数の半導体層の側面に配置されている抵抗変化材料層を一括して結晶化した後、第1の電流を印加した半導体層以外の半導体層に第2の電流を印加する。

(もっと読む)

半導体記憶装置

【課題】相変化メモリの構造の簡素化と低コスト化を実現する。

【解決手段】相変化材料からなる記録層18とn+型ポリシリコン膜15との間に、相変化材料を構成する元素の少なくとも一種とシリコンとを含有する中間層20を配置し、記録層18とn+型ポリシリコン膜15との接触抵抗を低減することにより、相変化メモリの構造の簡素化と低コスト化を実現する。例えば相変化材料がGe、SbおよびTeを含む場合、中間層20は、Si−Sb、Si−Te、Si−Geの少なくとも一種を含む。

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

メモリ素子スイッチング層形成用組成物、メモリ素子及びメモリ素子スイッチング層形成用重合体

【課題】良好なスイッチング特性を発現するとともに、塗布性に優れたメモリ素子スイッチング層形成用組成物を提供する。

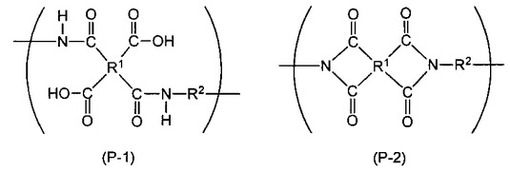

【解決手段】メモリ素子の陽極層と陰極層との間に配置されたスイッチング層を形成するのに用いるメモリ素子スイッチング層形成用組成物において、下記式(P−1)で表される繰り返し単位及び下記式(P−2)で表される繰り返し単位の少なくともいずれかの繰り返し単位(p1)を有する重合体を含むものとする。

(式(P−1)及び式(P−2)中、R1は脂環式構造を有する4価の基であり、R2はトリフェニルアミン構造を有する2価の基である。)

(もっと読む)

抵抗変化型不揮発性メモリセルおよび抵抗変化型不揮発性記憶装置

【課題】電流制御素子が破壊されにくい、抵抗変化型不揮発性メモリセルおよび抵抗変化型不揮発性記憶装置を提供する。

【解決手段】極性の異なる電気的信号を印加することにより抵抗値の異なる複数の抵抗状態の間を可逆的に遷移する抵抗変化素子103と、抵抗変化素子103に直列に接続し、所定の印加電圧の範囲において印加電圧の絶対値が大きくなるにしたがい電圧電流曲線の傾きが大きくなる非線形の電圧電流特性を有する電流制御素子104と、層間絶縁層108、109、110を貫通するホールの内部に形成され、抵抗変化素子103もしくは電流制御素子104の少なくとも一方に接触し、かつ、負荷抵抗部131A、131B、131Cを有する、プラグ105,106,107と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】従来のReRAMを有する半導体装置では、メモリ素子特性にばらつきが生ずるおそれがあった。

【解決手段】基板11を覆う第1の絶縁膜23を形成する工程と、第1の絶縁膜23を貫通する導電プラグ24を形成する工程と、導電プラグ24の上部を一部除去して、導電プラグ24の上面を底面として有し、かつ、一部除去した導電プラグ24に覆われていた部分の第1の絶縁膜23を側壁として有する孔部を形成する工程と、孔部の側壁を覆い、孔部の底面の一部を露出させる側壁絶縁膜25を形成する工程と、孔部の側壁絶縁膜25および底面を覆う可変抵抗膜26を形成する工程と、可変抵抗膜26を覆う導電膜27を形成する工程と、を有する。

(もっと読む)

相変化メモリの形成装置、及び相変化メモリの形成方法

【課題】金属カルコゲナイド膜の積層体を有する相変化メモリにおいて、読み書き動作の速度を高めることのできる相変化メモリの形成装置、及び相変化メモリの形成方法を提供する。

【解決手段】スパッタ装置10は、互いに異なる組成を有したGeTeターゲット22a及びSb2Te3ターゲット22bを有する。また、スパッタ装置10は、基板Sを加熱する加熱面を有して、基板Sを該加熱面に吸着しながら加熱する基板ステージ13と、基板ステージ13を基板Sの周方向に回転させる回転部18とを備えている。こうしたスパッタ装置10は、基板ステージ13が基板Sを吸着且つ加熱した状態で、回転部18が基板ステージ13を回転させつつ、GeTeターゲット22a及びSb2Te3ターゲット22bの各々を互いに異なるタイミングでスパッタすることにより、互いに異なる組成を有した二つの金属カルコゲナイド膜を基板S上に積層する。

(もっと読む)

不揮発性半導体記憶装置および同装置の製造方法

【課題】高抵抗状態と低抵抗状態の抵抗値の比を大きくする素子の構成及び方法並びに素子間ばらつきの低減方法を提供する。

【解決手段】ペロブスカイト酸化物の一面に特定金属が設けられるとともに、前記ペロブスカイト酸化物から前記金属へ当該ペロブスカイト酸化物の酸素が移動することで当該金属の酸化と当該ペロブスカイト酸化物の還元が進行するために必要な活性化エネルギー以上のエネルギーが与えられるように加熱することによって得られる酸素欠乏層領域が前記ペロブスカイト酸化物の前記金属と接触した近傍の領域に存在するようになし、前記金属よりなる一方の電極と前記酸素欠乏層を介して対となる他方の電極間の電圧−電流特性のヒステリシス特性を利用することを特徴とする不揮発性半導体記憶装置である。

(もっと読む)

抵抗記憶装置およびその書き込み方法

【課題】 イオン伝導領域を備えた抵抗記憶装置において、誤書き込みが発生しやすくなるという課題を解決する抵抗記憶装置およびその書き込み方法を提供する。

【解決手段】 抵抗記憶装置およびその書き込み方法であって、第1の絶縁体と、第1の絶縁体を挟んで対向して形成された第1の端子と第2の端子と、第1の絶縁体内に存在し第1の絶縁体が第1の端子と向かい合う面、もしくは第1の絶縁体が第2の端子と向かい合う面とほぼ平行な方向に延在する線状もしくは面状で第1の絶縁体に比べイオンが移動しやすいイオン伝導容易領域と、第1の端子と第2の端子の対向部を挟んで配置された第3の端子とイオン源とを有することを特徴としている。また、その書き込み方法は、書き込み処理を、読み出し端子をフローティング状態にして行うことを特徴としている。

(もっと読む)

抵抗記憶装置およびその製造方法

【課題】 電圧印加によりイオンを移動させることで伝導領域を形成・消滅させ、読み出し端子間の抵抗を変化させる抵抗記憶装置において、特性ばらつきが改善された抵抗記憶装置およびその製造方法を提供する。

【解決手段】 本発明の抵抗記憶装置は、イオン源部材と、イオン源部材上に形成された粒状または島状の絶縁体部材と、絶縁体部材上に形成されたイオン伝導体部材と、イオン伝導体部材上に形成された電極部材とを有することを特徴とする。また、本発明の抵抗記憶装置の製造方法は、イオン源部材上に粒状または島状に絶縁部材を形成する工程と、この絶縁部材上にイオン伝導体部材を形成する工程と、イオン伝導体部材上に電極部材を形成する工程とを有することを特徴とする。

(もっと読む)

121 - 130 / 1,392

[ Back to top ]