国際特許分類[H01L45/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 電位障壁または表面障壁をもたず,整流,増幅,発振またはスイッチングに特に適用される固体装置,例.誘電体三極素子;オブシンスキー効果装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,392)

国際特許分類[H01L45/00]の下位に属する分類

固体進行波装置

国際特許分類[H01L45/00]に分類される特許

11 - 20 / 1,392

分子メモリ装置の製造方法

【課題】メモリ素子の状態が良好なクロスポイント構造の分子メモリ装置の製造方法を提供する。

【解決手段】実施形態に係る分子メモリ装置の製造方法は、第1方向に延びる複数本の第1配線を含む配線層を形成する工程と、前記配線層上に犠牲膜を形成する工程と、前記犠牲膜上に第2方向に延びる複数本の第1絶縁部材を形成する工程と、前記第1絶縁部材の側面上に前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、隣り合う前記第1絶縁部材間であって前記第2配線間に複数本の第2絶縁部材を前記配線層に接するように形成する工程と、前記犠牲膜を除去することによりギャップを形成する工程と、前記ギャップ内に、前記第1配線及び前記第2配線のうちの一方に結合し他方には結合しない分子材料を形成する工程と、を備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

不揮発性記憶装置

【課題】プロセス耐性が高く、高い性能を維持する不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、第1導電部と、第2導電部と、記憶層と、を含む不揮発性記憶装置が提供される。前記記憶層は、前記第1導電部と前記第2導電部との間に設けられる。前記記憶層は、前記第1導電部と前記第2導電部とを介して供給される電流により、抵抗が低い第1状態と前記第1状態よりも抵抗が高い第2状態との間を可逆的に遷移可能である。前記記憶層は、カルコパイライト構造を有する。

(もっと読む)

半導体記憶装置

【課題】データ書き込みエラー発生と消費電力を低減させた半導体記憶装置を提供することを目的とする。

【解決手段】実施形態に係る半導体記憶装置は、第1極性の電圧パルス印加によってメモリセルに第1動作及び第2動作をさせるユニポーラ方式、並びに、第1極性とは異なる第2極性の電圧パルス印加によってメモリセルに第1動作をさせ且つ第1極性の電圧パルス印加によってメモリセルに第2動作をさせるバイポーラ方式の動作モードを有するデータ書き込み部と、メモリセルの第1動作の回数をカウントする第1動作回数カウント回路と、第1動作回数カウント回路を参照し、ユニポーラ方式による第1動作回数が第1規定回数に達した場合にデータ書き込み部の動作モードをバイポーラ方式に切り替える動作モード切り替え部とを備える。

(もっと読む)

半導体記憶装置の製造方法及び半導体記憶装置

【課題】抵抗変化膜の抵抗変化を容易にする半導体記憶装置の製造方法及び半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置の製造方法は、金属酸化物を含む抵抗変化膜との接触対象層にハロゲンを導入する工程と、前記ハロゲンを熱処理により前記接触対象層から前記抵抗変化膜に拡散させる工程とを備えている。

(もっと読む)

半導体装置

【課題】有機化合物を含む層を有する素子が設けられたフレキシブルな記憶装置及び半導

体装置を歩留まり高く作製する。また、信頼性の高いフレキシブルな記憶装置及び半導体

装置を歩留まり高く作製する。

【解決手段】剥離層を有する基板上に素子層及び素子層を封止する絶縁層を有する積層体

を形成し、剥離層から積層体を剥離してフレキシブルな記憶装置及び半導体装置を作製す

る方法であって、素子層において第1の電極層及び第2の電極層からなる一対の電極間に

有機化合物を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金

層で形成する。また、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物

を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金層で形成さ

れるフレキシブルな記憶装置及び半導体装置である。

(もっと読む)

不揮発性メモリ

【課題】メモリセルへのデータの書き込みと読出しの信頼性を高くした不揮発性メモリを提供する。

【解決手段】2つのメモリセルを隣接させた基本ユニットを単位にするメモリセルアレイを有し、前記基本ユニットの2つのメモリセルのメモリセル選択用トランジスタのソース端子を共通のソース線に接続し、前記2つのメモリセルを2つのビット線に接続した抵抗変化型メモリであって、前記ソース線の配線パターンと前記ビット線の配線パターンを平行に走行させ、前記ソース線の配線パターンと前記ビット線の配線パターンの一部の領域を上下で重ねあわせて対向させる。

(もっと読む)

不揮発性記憶素子、不揮発性記憶装置、不揮発性半導体装置、および不揮発性記憶素子の製造方法

【課題】 動作の高速化を図ることができ、可逆的に安定した書き換え特性と、良好な抵抗値のリテンション特性を有し、半導体製造プロセスと親和性の高い不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を備える不揮発性記憶装置および不揮発性半導体装置を提供する。

【解決手段】 本発明の不揮発性記憶素子は、第1電極103と、第2電極105と、第1電極103と第2電極104との間に介在させ、両電極103,105間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層104とを備え、この抵抗変化層104は少なくともタンタル酸化物を含み、当該タンタル酸化物をTaOxと表した場合に、0<x<2.5を満足するように抵抗変化層104が構成されている。

(もっと読む)

メモリ装置

【課題】増加されたメモリ容量を具現できるメモリ装置を提供する。

【解決手段】メモリ装置は、水平な共通導電領域の上に配置され、前記共通導電領域に一端が電気的に連結され、互いに離隔水平な第1選択ラインの上で互いに平行に延長され前記水平な第1選択ラインと交差し前記垂直な半導体柱の側面に対向する側面を包含する水平な第1選択ラインと、前記水平な第1選択ラインと前記垂直な半導体柱との間に、そして前記水平な第2選択ラインと前記垂直な半導体柱との間に介在される少なくとも1つの誘電パターンを包含する選択構造体を含む。前記メモリ装置は、前記選択構造体の上に配置され前記垂直な半導体柱に電気的に連結されたメモリセルを含むメモリセルアレイをさらに含む。

(もっと読む)

半導体素子及びその形成方法

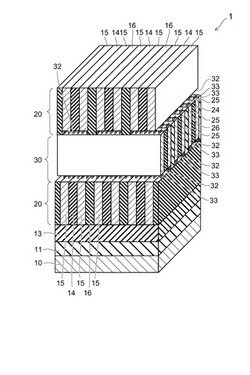

【課題】ビットラインを容易に形成することができ、ビットライン工程マージンを増加させ、さらに隣接したビットライン間のキャパシタンスを減少させる半導体素子及びその形成方法を提供する。

【解決手段】本発明に係る半導体素子は、半導体基板10で一方向に延長され、垂直チャンネル領域12b,14bを含む第1及び第2ピラー12,14と、第1及び第2ピラー12,14の内部で垂直チャンネル領域12b,14bの下部に位置する第1ビットライン22と、第1ビットライン22を含む第1ピラー12及び第2ピラー14の間に位置する絶縁膜32とを含む。

(もっと読む)

11 - 20 / 1,392

[ Back to top ]