国際特許分類[H03H17/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | インビーダンス回路網,例.共振回路;共振器 (15,336) | ディジタル技術を用いる回路網 (734)

国際特許分類[H03H17/00]の下位に属する分類

周波数選択回路網 (514)

位相推移を与える回路網 (21)

国際特許分類[H03H17/00]に分類される特許

171 - 180 / 199

デジタル信号処理装置

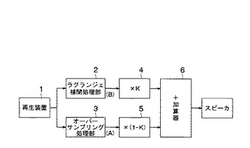

【課題】

もとのオーディオデータに対して、高域成分をその劣化を伴うことなく付加することにより、作成された高域成分に忠実な音質調整を行う。

【解決手段】

周波数帯域が制限されたデジタルオーディオデータに対して、高域データを付加して高域補償を行うデジタル信号処理装置であって、サンプル信号間に、多項式による演算をもとに複数のサンプルを用いて生成した補完データを挿入する補完処理部2と、サンプル信号の中央に零次補完を行い、さらに高調波除去を行うオーバサンプリング処理部3と、補完処理部出力のK倍とオーバサンプリング処理部出力の(1−K)倍(但し、0<K<1)を加算する加算器6を備え、加算器出力側から高域補償されたオーディオ信号を得る。

(もっと読む)

デジタルサンプリング周波数変換器

本発明は、入力デジタル信号を出力デジタル信号に変換するための変換器に関する。前記変換器は、特に、入力デジタル信号または出力デジタル信号のサンプルを含むことができるシフトレジスタの組を備えている。また、変換器は、前記シフトレジスタの組に対してシフト信号(4)を供給することができる演算ユニットを備えている。前記演算ユニットは、変換率の値またはその逆数の値を含むことができる第1の記憶装置(51)であって、記憶された値が0〜1となるようにする第1の記憶装置(51)を備えている。また、演算ユニットは、サイクル時間i+1(iは整数)において未来の信号(8)を含むことができる第2の記憶装置(52)であって、前記未来の信号(8)が、サイクル時間iにおいて第2の記憶装置内に含まれる現在の信号(7)と第1の記憶装置の内容との合計に等しい、第2の記憶装置(52)を備えている。この場合、シフト信号は、現在の信号の最上位ビット(71)と未来の信号の最上位ビット(81)との間での排他的OR機能(54)によって生じる。  (もっと読む)

(もっと読む)

空間スケーラビリティを備えているディジタル・フィルタ

信号をフィルタリングする方法、フィルタ及びビデオ符号器を記載する。フィルタ(92)は、第1フィルタ係数段(C2、C4、C6)によって信号のサンプルをフィルタリングする第1乗算装置群(102、104、106)、第1フィルタリング・サンプルを加算して第1加算信号を形成する第1加算装置(108、110)、第2フィルタ係数群(C1、C3、C5、C7)によってサンプルをフィルタリングする第2乗算装置群(114、116、118、120)、第2フィルタリング・サンプルを加算して第2和信号を形成する第2加算装置(122、124、126)及び第1和信号を第1係数段の和によって除算し、第2和信号を第2係数段の和によって除算して、第1出力信号及び第2出力信号を備える正規化装置(112、128)を備える。これによって、係数の和を等しくすることなく、係数の最適化を可能にする。  (もっと読む)

(もっと読む)

オーディオ信号処理装置

【課題】 入力されるオーディオ信号の成分に適したフィルタを選択し、出力する。

【解決手段】 オーディオ信号処理装置に入力されるオーディオ信号は、シャープロールオフ特性フィルタとスローロールオフ特性フィルタとに平行して入力され、フィルタリングされる。大振幅成分検出部は、オーディオ信号の出力値の変化量が所定の基準値より大きいか否かにより、オーディオ信号の振幅の大きな成分が検出する。高域成分検出部は、オーディオ信号の出力値の変化パターンが所定のパターンと一致するか否かによりオーディオ信号の高域成分が検出する。大振幅成分又は高域成分が検出された場合、切り換え部は、シャープロールオフ特性フィルタの出力に切り換えて出力部に出力し、それ以外は、スローロールオフ特性フィルタの出力を出力部に出力する。

(もっと読む)

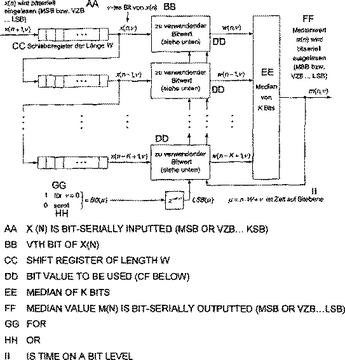

ディジタル濾波方法

非線形フィルタによりK個の入力値をディジタル濾波する方法が紹介され、フィルタが、K個の入力値からR最大値を発生する(K≧R≧1)。特にこの方法は。奇数K個の入力値から、出力値として中央値を発生するために使用することができ、従ってR=(K+1)/2である。基本思想は、一方では固定小数点形式で入力値の2進表示の使用であり、他方ではビットで逐次の処理であり、すべての普通の2進数表示が固定小数点形式で使用され、使用すべき数表示のそれぞれの性質を考慮して僅かな整合しか必要とされない。

この方法は、ディジタルフィルタの実現のため、特に物体識別システムにおける信号処理のために使用することができる。  (もっと読む)

(もっと読む)

マルチレートフィルタならびにマルチレートフィルタを備える表示システムおよび移動電話

本発明によるマルチレートフィルタは、a)入力信号(Sin)を受け取り、前記入力信号に応じて複数の中間信号(IS1、IS2)を供給する入力ユニット(10)と、b)入力ユニット(10)に結合されたフィルタ・ユニット(20)と、c)フィルタ・ユニット(20)に結合され出力信号(Sout)を生成する出力ユニット(30)とを備える。フィルタ・ユニット(20)は、伝達関数H0(z)および伝達関数H1(z)をそれぞれ有する少なくとも第1および第2のフィルタ・モジュール(21、22)を備え、これらの伝達関数は、H0(z)=c0(HB(z)+Mα,ψHB(z))およびH1(z)=c1(HB(z)+Mα,ψHB(z))の関係に従って互いに関連付けられ、ここで、Mα,ψ(HB(z))=αz−2ψHB*(z−1)であり、さらに式(1)はhb[m]のz変換である。マルチレートフィルタは、前記フィルタ・モジュール(21、22)に結合され第1の結合信号(Ssum)および第2の結合信号(Sdiff)を生成する結合ユニットを備える。  (もっと読む)

(もっと読む)

後処理を有する信号処理装置

【課題】中間メモリを迂回してアナログ/デジタル変換器に接続させるという切替を可能にする切替装置が設けられ、リアルタイムでの処理が可能にし、中間メモリに不必要な中間保存がされることを回避できる。

【解決手段】本信号処理装置1は、アナログ入力信号からデジタル入力信号の生成のためのアナログ/デジタル変換器3、前記デジタル入力信号の中間保存のための中間メモリ11およびデジタル処理のためのデジタル信号処理ユニット10を有している。前記信号処理ユニット10の入力は、切換装置5、9、12、13により、前記中間メモリの後か、または中間メモリ11を迂回するかのいずれかを選択して接続される。

(もっと読む)

サンプルレート変換装置

【課題】 簡単な回路構成で実現できるサンプルレート変換装置を提供する。

【解決手段】 位相差検出部4は、出力ワードクロックLRCKoと入力ワードクロックLRCKiの周期の差をLRCK周期カウンタ41と256減算器42により求めて累積加算部43で累積加算し、その累積加算値がLRCKoの1周期分を超えたかどうかを比較部414で比較し、1周期分を超えると位相遅れ/進み信号を出力する。補正調整部5は、位相遅れ/進み検出信号とリングバッファ1の残存データ量の情報に基づいて調整信号を読み出し制御部3へ出力する。読み出し制御部3は、調整信号に基づいてリングバッファ1のリードポインタRPの位置を調整してリングバッファ1から読み出すデータ量を制御する。

(もっと読む)

ディジタル適応ヒステリシス・システム

【課題】従来の単一の端数処理手法ではない、量子化エラーを削減するよう、2つのモードが用いられて主力値を生成する適応ディジタル・ヒステリシス手法。

【解決手段】床と天井との、2つの別々の手法のうちの何れを用いるかを判定するよう、モードを選択するトリップ点が存在する。床トリップ点及び天井トリップ点が入力信号値に基づいて生成される。他方のモードのトリップ点を超え、現行モードの次のトリップ点を超えない場合、モードが変更される。本願の手法の出力値は、ヒステリシス手法による従来の端数処理よりもエラーが低い。

(もっと読む)

信号処理装置、方法およびプログラム

【課題】 周波数特性を調整することができる信号処理装置、方法およびプログラムを提供すること。

【解決手段】 着目点を挟んで存在する前後2個の離散データを抽出する離散データ抽出部10と、4個の離散データのそれぞれについて着目点と各離散データまでの距離をtとして標本化関数の値を計算する標本化関数処理部20と、計算されたそれぞれの標本化関数の値を加算して畳み込み演算を行う畳み込み演算部30と、標本化関数の形状を決定するために必要なシフト量を可変設定するシフト量設定部50とが備わっている。標本化関数処理部20は、少なくとも1回以上微分可能な有限台の基本波形に対して、この基本波形に対して極性反転と利得調整を行った補助波形を前後に可変のシフト量だけシフトして加算することにより決定される標本化関数を用いて計算を行う。

(もっと読む)

171 - 180 / 199

[ Back to top ]