国際特許分類[H03K17/56]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 特定の構成要素の使用によって特徴づけられたもの (2,578) | 能動素子として半導体装置を用いるもの (2,114)

国際特許分類[H03K17/56]の下位に属する分類

二以上の形式の半導体装置の使用に特徴づけられた回路,例.BIMOS,IGBTのような複合装置 (31)

装置がトンネルダイオードであるもの

装置がバイポーラトランジスタであるもの (134)

装置が電界効果トランジスタであるもの (1,712)

装置が電極を2個だけもち,かつ負性抵抗を示すもの

バイポーラ半導体装置で3以上のPN接合を持つもの,例.サイリスタ,プログラムできるユニジャンクショントランジスタ,または4以上の電極をもつもの,例.シリコン制御スイッチ,または同一伝導領域に接続された2以上の電極をもつもの,例.ユニジャンクショントランジスタ (38)

国際特許分類[H03K17/56]に分類される特許

11 - 20 / 199

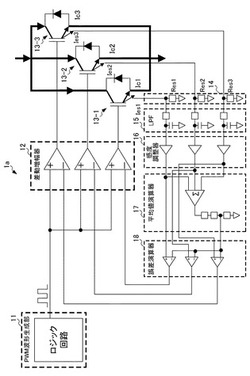

半導体素子駆動装置及び方法

【課題】並列に駆動される複数の半導体素子の特性差によって生じる、ターンオンやターンオフ時のスイッチングにおける電流の偏りを緩和すること。

【解決手段】電圧変換器14は、IGBT13−1乃至13−3の各々のエミッタセンス電流を電圧信号に変換する。平均値演算器17や誤差演算器18等の演算器は、LPF15から出力される、IGBT13−1乃至13−3の各々に対応する電圧信号の平均値を求め、それぞれの電圧信号についての平均値に対する誤差を演算する。PWM波形生成部11は、IGBT13−1乃至13−3の各々を駆動するための駆動信号(パルス信号)を出力する。差動増幅器12の各々の駆動信号を、当該IGBT13−1乃至13−3の各々に対応する誤差に基づいて調整して、当該IGBT13−1乃至13−3の各々に供給する。

(もっと読む)

半導体スイッチ及びスイッチ装置

【課題】電流変動が大きな箇所の半導体スイッチにおいて耐電流と損失を最適化する。

【解決手段】電気的特性及び種類が互いに異なるFET11とIGBT12を並列接続することで半導体スイッチ1aを形成する。端子5及び6間を接続するとき、FET11及びIGBT12は同時にオンされる。端子5及び6間の電流が小電流であるときには、FET11の内部抵抗がIGBT12よりも小さいため、FET11側に優先的に電流が流れて低損失が実現される。端子5及び6間の電流が増大するにつれて、FET11では発熱が内部抵抗増大を招くがIGBT12では内部抵抗が殆ど変化しないため、或る電流値以上では、IGBT12側に優先的に電流が流れる。結果、大電流がFET11側に流れることによるFET11の劣化又は破損が回避される。

(もっと読む)

スイッチング回路

【課題】半導体スイッチの寄生容量の充放電時間を短縮する回路を提供する。

【解決手段】スイッチング回路10の入力端子21と出力端子22との間、入力端子21と共通端子23との間及び出力端子22と共通端子23との間の少なくとも一つに接続される容量抑制素子部50を備え、容量抑制素子部50は、容量抑制素子部が接続される半導体スイッチ素子20の端子間の寄生容量を、パルス状信号のクロック周波数のN倍(Nは1以上の整数)の周波数において、容量抑制素子部が接続されていない場合より低減する。

(もっと読む)

スイッチング回路

【課題】半導体スイッチの寄生容量の充放電時間を短縮し、オーバドライブによらず速度の向上と電力効率の向上を図り得るスイッチング回路を提供する。

【解決手段】半導体スイッチ素子20a、20dがON(OFF)のとき残りの半導体スイッチ素子がOFF(ON)となるように、各半導体スイッチ素子の入力端子にパルス状信号が印加される。スイッチング回路は、半導体スイッチ素子20bの出力端子と半導体スイッチ素子20dの入力端子の間に接続されるキャパシタンス素子60と、半導体スイッチ素子20bの入力端子と半導体スイッチ素子の出力端子20dの間に接続されるキャパシタンス素子61とを備える。キャパシタンス素子60,61は、半導体スイッチ素子20b、20dの各々の入力端子と出力端子間の寄生容量を、半導体スイッチ素子20b、20dに供給されるパルス状信号のクロック周波数のN倍の周波数において低減する容量を有する。

(もっと読む)

ゲート駆動回路

【課題】 簡便な回路構成で、高速に動作するゲート駆動回路を提供することである。

【解決手段】 パワー半導体素子のゲート端子に正電圧を印加するためのNPNトランジスタと、パワー半導体素子のゲート端子に負電圧を印加するためのPNPトランジスタと、NPNトランジスタと、PNPトランジスタとに直列に接続された遮断用抵抗器と、遮断用抵抗器に、正極がパワー半導体素子のゲート端子側となるように並列に接続された遮断用抵抗器切換え半導体スイッチとを備えたゲート駆動回路である。

(もっと読む)

スイッチング素子の駆動回路

【課題】オフ保持用スイッチング素子46をオフ状態とすべき期間において、この素子が誤ってオフ状態とされることに起因するスイッチング素子S*#の信頼性の低下を抑制することのできるスイッチング素子の駆動回路を提供する。

【解決手段】オフ保持回路48は、信号生成部26の操作信号INを入力としてゲートの充電処理の実行中であると判断された場合、オフ保持用スイッチング素子46をオフし、操作信号INを入力としてゲートの放電処理の実行中であると判断されて且つゲート電圧検出部50の出力信号GPRを入力としてゲート電圧Vgeが低いと判断された場合、オフ保持用スイッチング素子46をオンする。ここで、上記駆動回路は、ゲート電圧Vgeが閾値電圧を跨いでから出力信号GPRの論理が反転するまでの時間を、操作信号INを入力としてオフ保持回路48によって把握される充電処理指示時間の最小値以下とするように構成される。

(もっと読む)

スイッチング装置、スイッチングモジュール

【課題】本発明は、サージ電圧の低減及び発生ノイズの低減を可能とするスイッチング装置、スイッチングモジュールを提供することを目的とする。

【解決手段】本発明にかかるスイッチング装置は、スイッチング素子1と、エミッタ電極100と、エミッタ電極100を外部の主配線に接続するための主配線用エミッタ端子4と、エミッタ電極100と主配線用エミッタ端子4との間の主電流経路に介在する、複数の制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7と、隣接する制御用エミッタ端子間の主電流経路に介挿されたインダクタンス8、インダクタンス9とを備えることを特徴とする。

(もっと読む)

負荷駆動装置

【課題】クランプ回路が未使用状態なのか断線状態なのかを判別する。

【解決手段】温度センサ1hの出力が入力される温度検出端子14a〜14cを利用し、クランプ回路5a〜5cや温度検出回路7a〜7cの一部がパワーモジュール1に接続されないときには温度検出端子14a〜14cの電位に基づいて温度センサ1hが接続されていない断線無効状態を検出する。例えば、温度検出端子14a〜14cのうち温度センサ1hに接続されない端子に断線検出無効化閾値Vth3以上の電圧を印加することで、温度検出端子14a〜14cが温度センサ1hに接続されていないことを検出する。これにより、クランプ回路5a〜5cに接続されるクランプ端子11a〜11cの電位に基づいて断線検出を行う際に、断線状態なのか断線無効状態なのかを温度検出端子14a〜14cの電位に応じて判定できる。

(もっと読む)

パワー半導体スイッチの制御回路及びその制御方法

【課題】寄生容量の影響を最少化させることのできる、パワー半導体スイッチの改良された制御方法及び制御装置を提供する。

【解決手段】パワー半導体スイッチの制御接続端信号を生成するための信号処理ユニットを備えた、パワー半導体スイッチを制御する制御回路において、少なくとも一つの半導体素子が、定められたパワー半導体スイッチのコレクタ・エミッタ電圧を越えた時に、導通作動され、半導体素子の出力端が導電性の接続線を通じて抵抗直列回路の抵抗の間の接続点と、或いは信号処理ユニットと接続されている抵抗直列回路の出力端と接続されており、半導体素子のブレークダウン電圧が、半導体素子の出力端の電位が、パワー半導体スイッチがスイッチオン状態にある時のパワー半導体スイッチの制御接続端の電位よりも高くなるように選ばれている。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】 スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路構成で実現する。

【解決手段】 トランス15の1次側をローサイドゲート駆動回路2の出力端子に接続し、トランス15の2次側をハイサイドスイッチング素子5のゲート入力側に接続する。ローサイド駆動回路2から正極性のゲート駆動電圧が出力されるとハイサイドスイッチング素子5のゲート‐ソース間には負極性の電圧が印加されてゲート電圧は閾値以下に抑えられるため、ローサイドスイッチング素子がターンオンする際にハイサイドスイッチング素子はオフ状態を維持する。

(もっと読む)

11 - 20 / 199

[ Back to top ]