国際特許分類[H03K17/56]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 特定の構成要素の使用によって特徴づけられたもの (2,578) | 能動素子として半導体装置を用いるもの (2,114)

国際特許分類[H03K17/56]の下位に属する分類

二以上の形式の半導体装置の使用に特徴づけられた回路,例.BIMOS,IGBTのような複合装置 (31)

装置がトンネルダイオードであるもの

装置がバイポーラトランジスタであるもの (134)

装置が電界効果トランジスタであるもの (1,712)

装置が電極を2個だけもち,かつ負性抵抗を示すもの

バイポーラ半導体装置で3以上のPN接合を持つもの,例.サイリスタ,プログラムできるユニジャンクショントランジスタ,または4以上の電極をもつもの,例.シリコン制御スイッチ,または同一伝導領域に接続された2以上の電極をもつもの,例.ユニジャンクショントランジスタ (38)

国際特許分類[H03K17/56]に分類される特許

81 - 90 / 199

電力変換装置

【課題】 電力変換用スイッチング素子を異常電流から保護する際、当該スイッチング素子の制御端子に印加する電圧制御信号のレベルを下げることなく、またバラつきも少ないスイッチング素子を保護する機能を有する電力変換装置を提供する。

【解決手段】 本発明の電力変換装置1は、一対の主端子と主端子対に流れる電流を制御する制御端子とをもち、主端子の低電位側端子が低電位側に接続される電力変換用スイッチング素子134〜139と、主端子対に流れる主電流を検出する電流検出回路4と、制御端子と低電位側との間に位置する主コンデンサ5と、電流検出回路4によって検出された主電流がスイッチング素子134〜139の所定値を超えた場合に、制御端子と低電位側との間に主コンデンサ5が電気的に接続されるようにスイッチング動作する保護用スイッチング素子6と、を有することを特徴とする。

(もっと読む)

パワー半導体スイッチのドライバ回路内部で信号電圧伝送するための回路と方法

【課題】パワー半導体スイッチのドライバ回路内部で、信号電圧を伝送するための回路と方法を提供する。

【解決手段】ドライバ回路6の1次側8aに、第1信号電圧US1のための信号入力14aと、第1信号電圧US1と相関関係のある電流I、I’のための電流源16、16’と、電流I、I’のための接続ライン20、20’とを含み、この接続ラインは、電流源16、16’からドライバ回路6の2次側8bへ連結している。さらに、2次側8bには、電流I、I’を、この電流と相関関係のある第2信号電圧US2に変換するための電流・電圧変換器24、24’と、第2信号電圧US2のための信号出力14bとを含んで出力される。

(もっと読む)

パワーエレクトロニクスコンポーネントを制御するためのデバイス及び回路、関連する駆動方法、並びに関連する点弧子

【課題】RC回路のコンポーネントを交換することなく、新しい印加のたびに調整が行われるよう、制御の対象となる少なくとも1つのパワーエレクトロニクスコンポーネントを制御するための回路を提案する。

【解決手段】本発明は、パワーエレクトロニクスコンポーネント12の開閉を制御するための回路26に関する。上記回路は、第1垂直枝路33Aと第2垂直枝路33Bとから成るHブリッジを具備する。第1垂直枝路33Aは、デジタル制御された第1電流生成部40と第1スイッチ34とから成る。第1生成部40は、一方向に向けられた供給電流を供給するために適する。第2垂直枝路33Bは、デジタル制御された第2電流生成部44と該第2電流生成部44に直列に接続された第2スイッチ36とから成る。第2生成部44は、逆方向に向けられた供給電流を供給するために適する。また、本発明は、制御デバイス、駆動方法、及び点弧子に関する。

(もっと読む)

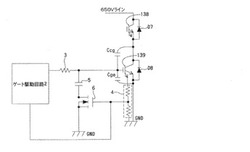

ゲート駆動回路

【課題】主スイッチング素子のターンオフ,ターンオン動作を、コンデンサを用いることで高速化しスイッチング損失を低減させる。

【解決手段】主スイッチング素子1の例えばオン期間中に、電源電圧11によりコンデンサ15を充電し、このコンデンサ15に蓄積された電圧を、主スイッチング素子1がオフする際の逆バイアス電源として用いることより、特に負電圧用の電源を用いることなく高速なターンオフ動作を可能にし、スイッチング損失の低減化を図る。

(もっと読む)

電圧駆動型半導体素子のゲート駆動装置

【課題】FWDが小電流で逆回復する時のサージ電圧や電圧振動を抑制するために、対向アームのオンゲート抵抗値を大きくする方式では、通常電流時の損失が大きくなり、装置の損失が大きく、装置が大型となる。

【解決手段】ターンオフ時にIGBT3に接続されている内部インダクタンス5に発生する電圧を検出する電圧検出回路12と、オフゲート信号が入力されてから電圧検出回路12が電圧検出するまでの検出時間と予め定められた設定時間とを比較する比較回路13と、を備え、比較結果に応じてターンオン用のゲート駆動抵抗8又は11をスイッチ素子6、10で切替える。

(もっと読む)

パワー半導体のゲート駆動回路

【課題】パワー半導体におけるサージ電圧の上昇を抑制しつつパワー半導体のスイッチングロスを低減することが可能であり、かつパワー半導体装置を小型化することが可能なパワー半導体の駆動回路を提供する。

【解決手段】ゲート駆動回路100に、PチャネルMOSFET11のスイッチング動作によりIGBT200をターンオンするオン側駆動回路2と、NチャネルMOSFET12のスイッチング動作によりIGBT200をターンオフするオフ側駆動回路3と、NチャネルMOSFET13のスイッチング動作によりIGBT200のターンオフ状態を保持するオフ保持回路5と、を具備し、オフ保持回路5に、NチャネルMOSFET13のスイッチング動作によりターンオフ動作を開始し、PチャネルMOSFET11およびNチャネルMOSFET13よりもターンオフ動作に要する時間が長いPNP型バイポーラトランジスタ14を設けた。

(もっと読む)

パワーデバイスドライブ装置

【課題】ソフトシャットダウン機能を有するパワーデバイスドライブ装置の出力端子とパワーデバイスを接続する信号線を短縮化する。

【解決手段】パワーデバイスドライブ装置50には、光結合部1とパワーデバイスドライブ回路部2が設けられる。パワーデバイスドライブ回路部2には、ドライバ部21、ディセイブル回路22、I/V変換回路23、サンプルホールド回路24、ソフトシャットダウン回路25、制御端子PDisb、Vcc端子PVcc、Vo端子PVo、及びVss端子PVssが設けられる。IGBT4の短絡等の異常事態が発生したとき、制御信号Ssetがディセイブル状態となる。ディセイブル状態の制御信号Ssetがディセイブル回路22に入力され、出力部から出力される信号がHz状態となり、ソフトシャットダウン回路25のNch MOSトランジスタNMT3が“ON”しIGBT4をソフトシャットダウン状態にする。

(もっと読む)

アクティブゲート回路

【課題】自己のアームの半導体スイッチング素子のターンオン時のコレクタ・エミッタ過電圧の抑制のみならず、他方のアームの半導体スイッチング素子の還流ダイオードのリカバリ電圧の過電圧の抑制も可能とすることである。

【解決手段】アクティブゲート回路12aのリカバリ過電圧抑制手段16aは、電力変換器のレグを形成する一対のアームのうちの一方のアームの半導体スイッチング素子S1のターンオン時に他方のアームの還流ダイオードD2のリカバリ電圧の過電圧を抑制するように一方のアームの半導体スイッチング素子S1のゲート電流を調整する。

(もっと読む)

アナログ/ディジタル変換装置

【課題】低オフセットで高価な電圧源を不要にし、低コスト化を可能にした高精度のアナログ/ディジタル変換装置を提供する。

【解決手段】3相交流電圧または交流電流の第1〜第3のアナログ検出値にそれぞれ同一の直流量を加算する手段と、前記直流量加算後の第1〜第3のアナログ検出値を第1〜第3のディジタル検出値に変換する片極性のA/D変換器33と、第1のA/D変換値を(2×第1のディジタル検出値−第2のディジタル検出値−第3のディジタル検出値)/3により演算し、第3のA/D変換値を(2×第3のディジタル検出値−第1のディジタル検出値−第2のディジタル検出値)/3により演算し、第2のA/D変換値を(−第1のアナログ/ディジタル変換値−第3のアナログ/ディジタル変換値)により演算する手段(ソフトウェア)と、を備える。

(もっと読む)

車載情報伝達装置

【課題】インバータの温度を感知する感温ダイオードSDの温度に関する情報をマイコン20に伝達する際に、マイコン20のタイマ機能やA/D変換機能を備えたポートを使用すると、そのリソースが低減すること。

【解決手段】感温ダイオードSDの出力電圧に基づき周波数変調回路34にて周波数変調された信号は、フォトカプラ36に取り込まれる。フォトカプラ36の出力は、マイコン20に取り込まれる。マイコン20においては、フォトカプラ36の出力電圧が閾値電圧以上であるなら論理「H」と認識し、閾値電圧未満であるなら論理「L」と認識する処理を、ハードウェアにて行う。一方、論理「H」である期間や論理「L」である期間に基づく温度情報の復調処理を、ソフトウェア処理とする。

(もっと読む)

81 - 90 / 199

[ Back to top ]