国際特許分類[H03K17/56]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 特定の構成要素の使用によって特徴づけられたもの (2,578) | 能動素子として半導体装置を用いるもの (2,114)

国際特許分類[H03K17/56]の下位に属する分類

二以上の形式の半導体装置の使用に特徴づけられた回路,例.BIMOS,IGBTのような複合装置 (31)

装置がトンネルダイオードであるもの

装置がバイポーラトランジスタであるもの (134)

装置が電界効果トランジスタであるもの (1,712)

装置が電極を2個だけもち,かつ負性抵抗を示すもの

バイポーラ半導体装置で3以上のPN接合を持つもの,例.サイリスタ,プログラムできるユニジャンクショントランジスタ,または4以上の電極をもつもの,例.シリコン制御スイッチ,または同一伝導領域に接続された2以上の電極をもつもの,例.ユニジャンクショントランジスタ (38)

国際特許分類[H03K17/56]に分類される特許

61 - 70 / 199

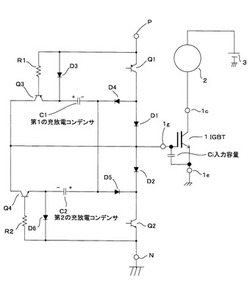

ゲート駆動回路

【課題】ゲート端子の入力容量の充放電に伴うスイッチングの遅れを防止して電力用半導体スイッチング素子を高速にスイッチングする。

【解決手段】IGBT1がオフしているときに第1の充放電コンデンサC1を充電し、IGBT1がオフからオンにスイッチングするときに、正端子Pを介した電源電圧と第1の充放電コンデンサC1の充電電圧とを直列に合成した順方向の高電圧によりIGBT1のゲート端子1gの入力容量Ciを瞬時に初期充電して迅速にオンする。また、IGBT1がオフしているときに第2の充放電コンデンサC2を充電し、IGBT1がオンからオフにスイッチングするときに、負端子Nを介した電源電圧と第2の充放電コンデンサC2の充電電圧とを直列に合成した逆方向の高電圧により入力容量Ciを瞬時に初期放電して迅速にオフする。

(もっと読む)

半導体スイッチ回路

【課題】電圧駆動型半導体素子の特性のばらつきによりターンオフ時にコレクタ電圧差が生じる場合であっても、電圧分担をほぼ均一にすることである。

【解決手段】直列接続された3個以上の電圧駆動型半導体素子のコレクタとゲート駆動回路との接続線を互いにコモンモードリアクトルで磁気結合させ、リアクトルの磁気結合巻線にコンデンサ及び抵抗を直列接続して一方が各々の電圧駆動型半導体素子のコレクタに接続され他方が各々のゲート抵抗に接続される電圧均一化回路22を設け、少なくともいずれか一つの電圧均一化回路22のリアクトルを自己以外の二つ以上の他の電圧均一化回路22のリアクトル16と磁気結合させたときは、自己の電圧均一化回路22は、磁気結合した各々のリアクトル16の磁気結合巻線にコンデンサ17をそれぞれ直列接続して並列接続し、その並列接続された磁気結合巻線に一つにまとめた抵抗18を直列接続する。

(もっと読む)

半導体装置

【課題】要求仕様に応じて電気的特性を適切に切り替えることが可能な半導体装置を提供する。

【解決手段】半導体装置101は、スイッチング損失および飽和電圧損失が互いに異なる複数の半導体スイッチ素子11,12と、複数の半導体スイッチ素子11,12のいずれかを選択し、選択した半導体スイッチ素子を駆動する選択駆動部51と、複数の半導体スイッチ素子11,12および選択駆動部51を収容するケースKとを備える。

(もっと読む)

ラッチ回路を有する信号処理装置

【課題】 ラッチ回路がノイズによって誤動作することがある。

【解決手段】

信号処理装置は、セットパルス発生回路3と、リセットパルス発生回路5と、ラッチ回路4との他に補正セットパルス形成回路30を有する。補正セット信号形成回路30は、セットパルスからリセットパルスまでの時間幅にほぼ対応する補正セット信号を形成してラッチ回路4に送る。ラッチ回路4はノイズによってリセットされても補正セット信号によって再びセットされる。

(もっと読む)

電気回路のスイッチング装置

【課題】逆方向電流を阻止する機能を有するIGFETの逆方向耐圧の向上が要求されている。

【解決手段】スイッチング装置(10)は、逆方向電流を阻止するショットキダイオードD3を内蔵する主IGFET(11)と、保護スイッチ手段(12)と、保護スイッチ制御手段(13)とを有する。保護スイッチ手段(12)は主IGFET(11)のドレイン電極Dとゲート電極Gとの間に接続されている。保護スイッチ制御手段(13)は、主IGFET(11)に逆方向電圧が印加された時に保護スイッチ手段(12)をオンにする。これにより、主IGFET(11)が逆方向電圧から保護される。

(もっと読む)

電力変換回路の駆動回路

【課題】電力変換回路の備えるパワースイッチング素子Sのゲート及びエミッタ間を短絡させる機能を搭載する場合、ドライブIC20が大型化するおそれがあること。

【解決手段】パワースイッチング素子Sのゲート及びエミッタ間は、オフ保持用スイッチング素子62によって短絡される。オフ保持用スイッチング素子62は、ドライブIC20内のオフ保持回路60によってオン操作される。オフ保持回路60は、パワースイッチング素子Sを充電するための充電用スイッチング素子24に接続される端子T1の印加電圧を利用してパワースイッチング素子Sのゲート電圧を把握することで、オフ保持用スイッチング素子62のオン操作を行う。

(もっと読む)

レベルシフト回路、スイッチング素子駆動回路及びインバータ装置

【課題】レベルシフト回路のdv/dt等に起因するコモンモードノイズによる誤判定を抑制し、ロバスト性の高いスイッチング素子駆動回路及びインバータ装置を提供する。

【解決手段】レベルシフト回路のオフセットが設けられたセット用負荷の信号レベルとリセット用負荷との信号レベルとを比較し、セット用負荷のレベルがリセット用負荷のレベルに比べ前記オフセットより低くなったことを判定して前記セットパルスを検出する

(もっと読む)

電力変換回路の駆動回路

【課題】パワースイッチング素子Sを流れる電流が規定値以上となることで、この電流を制限すべくパワースイッチング素子Sのゲートに印加される電圧をツェナーダイオード58のブレークダウン電圧程度に規制するに際し、ツェナーダイオード58に過度の電流が流れるおそれがあること。

【解決手段】パワースイッチング素子Sを流れる電流が規定値以上となることで、コンパレータ54からフェール信号FLが出力される。パワースイッチング素子Sをオンすべくそのゲートに正の電荷を供給するための電源26とゲートとの間のスイッチング素子24a,24bのうち、スイッチング素子24bは、フェール信号FLの出力時には、強制的にオフされる。

(もっと読む)

パルストランスを用いた信号伝達回路

【課題】パルストランスを用いた信号伝達回路に接続される回路要素の誤動作を回避する。

【解決手段】パルストランスTの2次側において、スイッチ素子Q2は、IGBTのゲート・エミッタ間に設けられる。コンデンサCは、スイッチ素子Q2の制御端子に接続される。スイッチ素子Q3は、コンデンサCに接続される。パルストランスTの1次側に設けられているスイッチ素子Q1をターンオフすると、2次側において負電圧が発生し、コンデンサCがチャージされる。スイッチ素子Q1がオフ状態である期間は、パルストランスTの励磁エネルギーが放出された後であっても、コンデンサCの負電圧は保持され、スイッチ素子Q2はオン状態に保持されるので、IGBTのゲート・エミッタ間のインピーダンスは低い状態に維持される。

(もっと読む)

電圧駆動型半導体素子のゲート駆動装置

【課題】 電力変換装置の各アームを構成する半導体素子に対して設けられるフリーホイーリングダイオードのサージ電圧を抑制し、半導体素子のターンオン損失を低減する。

【解決手段】従来のゲート駆動装置に対し、抵抗R,コンデンサCからなる遅延回路、抵抗Rg(on)1およびトランジスタTR10を接続することにより、フリーホイーリングダイオード逆回復時の低電流域では、半導体素子IGBTを抵抗Rg(on)により、また高電流域では抵抗Rg(on)と抵抗Rg(on)1との並列抵抗により、それぞれターンオンさせることで掲記課題の解決を図る。

(もっと読む)

61 - 70 / 199

[ Back to top ]