国際特許分類[H03K17/56]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 特定の構成要素の使用によって特徴づけられたもの (2,578) | 能動素子として半導体装置を用いるもの (2,114)

国際特許分類[H03K17/56]の下位に属する分類

二以上の形式の半導体装置の使用に特徴づけられた回路,例.BIMOS,IGBTのような複合装置 (31)

装置がトンネルダイオードであるもの

装置がバイポーラトランジスタであるもの (134)

装置が電界効果トランジスタであるもの (1,712)

装置が電極を2個だけもち,かつ負性抵抗を示すもの

バイポーラ半導体装置で3以上のPN接合を持つもの,例.サイリスタ,プログラムできるユニジャンクショントランジスタ,または4以上の電極をもつもの,例.シリコン制御スイッチ,または同一伝導領域に接続された2以上の電極をもつもの,例.ユニジャンクショントランジスタ (38)

国際特許分類[H03K17/56]に分類される特許

21 - 30 / 199

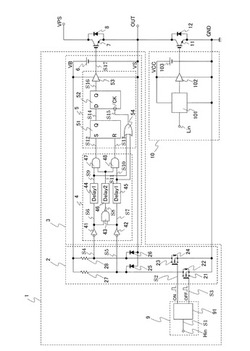

半導体回路

【課題】 高電位側スイッチング素子の導通を示す第1状態から前記高電位側スイッチングデバイスの非導通を示す第2状態への遷移、または前記第2状態から前記第1状態への遷移に伴い発生する過渡的な電圧ノイズに曝された場合に発生する誤信号を確実に除去する半導体回路を提供する。

【解決手段】 高電位側スイッチング素子駆動回路1は、スイッチング素子7の導通状態を変化させる場合に第1、第2のレベルシフト素子21、24のオン/オフ状態を必ず同一状態にするためのフリップフロップ52と、マスク信号S11が確実にセット信号S9、リセット信号S10を覆うようにするための第1、2、3の遅延回路44、45、46を有する。

(もっと読む)

スイッチング回路

【課題】電力効率を低下させずに高速動作可能なスイッチング回路を提供する。

【解決手段】スイッチング回路は、入力電圧を第1の電圧に変換する第1のDC/DCコンバータB1と、制御信号に応じて第1の電圧を出力するか否か切り替える第1のスイッチ回路C1と、第1のスイッチ回路からの電圧の過渡特性を制御する第1の制御回路D1と、高圧側電源に一端が、出力端子に他端が接続され、第1の制御回路からの電圧に応じてオンオフされる第1の能動素子A1と、入力電圧を第2の電圧に変換する第2のDC/DCコンバータB2と、制御信号に応じて第1のスイッチ回路とは相補的に第2の電圧を出力するか否か切り替える第3のスイッチ回路C3と、第3のスイッチ回路からの電圧の過渡特性を制御する第2の制御回路D2と、出力端子に一端が、低圧側電源に他端が接続され、第2の制御回路からの電圧に応じてオンオフされる第2の能動素子A2とを備える。

(もっと読む)

電子装置

【課題】スイッチング素子をオンするために、スイッチング素子の制御端子に定電流を供給して電荷を充電するオン駆動用定電流回路の異常を検出できる電子装置を提供する。

【解決手段】制御装置12は、オン駆動用定電流回路121と、オフ駆動用回路122と、制御回路128とを備えている。オン駆動用定電流回路121は、電流制御用FET121aと、電流検出用抵抗121bとを有している。制御回路128は、電流検出用抵抗121bの電圧に基づいて電流制御用FET121aを制御し、IGBT110dのゲートに定電流を流し込み、IGBT110dをオンする。オン駆動用定電流回路121の電流制御用FET121aや電流検出用抵抗121bが故障すると、それらに流れる電流や、それらに印加される電圧が変化する。そのため、電流検出用抵抗121bの電圧に基づいてオン駆動用定電流回路121の異常を検出することができる。

(もっと読む)

電圧駆動型スイッチングデバイスの駆動回路

【課題】ターンオン時のゲート電流を所望の電流値に高精度に設定でき、スイッチング損失の低減が可能な電圧駆動型スイッチングデバイスの駆動回路を得る。

【解決手段】IGBT1のゲート端子に接続され、駆動用パルス信号2のオン/オフゲート制御信号に基づき、IGBT1をターンオン/ターンオフさせるゲート信号を前記ゲート端子に出力するゲート駆動定電流回路が示されている。このゲート駆動定電流回路は、正電源3とGND電位4間に直列に接続された第1の抵抗5と第1のトランジスタ15と第2の抵抗6と制御信号伝達トランジスタ7、および正電源3とIGBT1のゲート端子間に直列に接続されたゲートオン抵抗8と定電流出力トランジスタ9を備え、第1のトランジスタ15のベース端子は第1のトランジスタ15のコレクタ端子と短絡接続されている。

(もっと読む)

電子装置

【課題】オン駆動用定電流回路が故障しても、スイッチング素子の破損を抑えて駆動することができる電子装置を提供することを目的とする。

【解決手段】制御回路128は、オン駆動用定電流回路121が故障して、IGBT110dのゲートに正常時に流れ込む電流より大きい電流が流れ込むようになったとき、オフ駆動用定電流回路122の電流を調整する。これにより、IGBT110dのゲートに流れ込む電流、及び、ゲートから引き抜く電流を調整することができる。そのため、オン駆動用定電流回路121が故障しても、IGBT110dの破損を抑えて駆動することができる。

(もっと読む)

スイッチング素子駆動回路

【課題】スイッチング素子駆動回路において、スイッチング素子のスイッチング損失を抑制する。

【解決手段】 ゲート電圧検出回路201は、スイッチング素子11のゲート電圧Vgsを検出し、このゲート電圧がスイッチング素子11の閾値電圧未満に設定された所定電圧未満のとき、Hレベルの昇圧指示信号を出力する。電圧制御回路103は、前記昇圧指示信号がLレベルの間は、制御電源102の所定電圧V1をそのまま出力し、前記昇圧指示信号がHレベルの間は、前記所定電圧V1を昇圧した電圧V2を出力する。駆動信号出力回路104は、PWMパルス出力回路111から出力されるPWMパルスの電圧を電圧制御回路103から出力される電圧に増幅する。従って、駆動信号出力回路104からスイッチング素子11への駆動信号は、前記PWMパルスがHレベルになった時に、先ず昇圧された電圧V2となり、スイッチング素子11のゲート電圧Vgsが所定電圧にまで上昇すると、所定電圧V1となる。

(もっと読む)

スイッチング素子の駆動回路

【課題】スイッチング素子S*#のオン状態への切り替えによってこれを流れる電流が急激に大きくなると、ツェナーダイオード40およびクランプ用スイッチング素子42を備えて構成されるクランプ回路による対処が間に合わなくなるおそれがあること。

【解決手段】スイッチング素子S*#のオン操作指令に伴い、まず制限用電圧VLを端子電圧とする直流電圧源25を電源とし、定電流用スイッチング素子27を用いてスイッチング素子S*#のゲート充電処理を行う。そして、所定時間が経過することで、定常用電圧VH(>VL)を端子電圧とする直流電圧源22を電源とし、定電圧用スイッチング素子23を用いてスイッチング素子S*#のゲート充電処理を行う。

(もっと読む)

レベルシフト回路並びにレベルシフト回路を備えたインバータ装置

【課題】VM電位のdv/dtに起因する上アーム電力用スイッチング素子の誤動作を抑制できるレベルシフト回路並びにこれを備えたインバータ装置を提供する。

【解決手段】支持体Si基板上にBOX酸化膜を介しN型Si活性層を形成したSOI基板により構成し、分離酸化膜により分離されN型MOSFETを形成する第1のN型Si活性層、分離酸化膜により分離されP型拡散層による拡散抵抗を形成する第2のN型Si活性層、分離酸化膜により分離され上アーム制御電源の一端側に接続する第4のN型Si活性層から構成され、第1のN型Si活性層を形成する分離酸化膜と第4のN型Si活性層を形成する分離酸化膜は、隣接配置されるとともに、N型MOSFETのドレイン電極と拡散抵抗の第一の電極を接続し、拡散抵抗の第2の電極を上アーム制御電源の他端側に接続した。

(もっと読む)

スイッチング素子の駆動回路

【課題】定電流制御に異常が生じる場合、スイッチング素子S*#が熱破損するおそれが生じたり、スイッチング状態の切替に伴うサージが過度に大きくなったりするおそれがあること。

【解決手段】電源20から出力される正の電荷は、異常検出用抵抗体22、定電流用抵抗体24および充電用スイッチング素子32を介してスイッチング素子S*#のゲートに充電される。この際、定電流用抵抗体24の電圧降下量が規定値となるように、オペアンプ36によって充電用スイッチング素子32のゲート電圧が操作される。異常検出用抵抗体22の電圧降下量は、充電側異常判断部62に取り込まれ、これに基づき定電流制御の異常の有無が判断される。

(もっと読む)

負荷駆動装置

【課題】スイッチング素子の立ち上がりの速度を高速に維持しつつ、スイッチング素子を駆動するドライバ回路の消費電流を削減することができる負荷駆動装置を提供する。

【解決手段】負荷10に接続されるスイッチング素子50と、定電流を生成する定電流生成部30と、定電流生成部30から流れ込む定電流の大きさに応じたオン時間でスイッチング素子50をオンするドライバ回路40と、を備えた構成とする。そして、定電流生成部30は、スイッチング素子50がオンするオン時間に達するまではドライバ回路40に第1電流量の大きさの定電流を流すことでスイッチング素子50の立ち上がりの速度を高速に維持する。また、定電流生成部30は、スイッチング素子50がオンするオン時間が経過した後はドライバ回路40に第1電流量よりも小さい第2電流量の定電流を流すことでドライバ回路40の消費電流を削減する。

(もっと読む)

21 - 30 / 199

[ Back to top ]