国際特許分類[H03K17/56]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 特定の構成要素の使用によって特徴づけられたもの (2,578) | 能動素子として半導体装置を用いるもの (2,114)

国際特許分類[H03K17/56]の下位に属する分類

二以上の形式の半導体装置の使用に特徴づけられた回路,例.BIMOS,IGBTのような複合装置 (31)

装置がトンネルダイオードであるもの

装置がバイポーラトランジスタであるもの (134)

装置が電界効果トランジスタであるもの (1,712)

装置が電極を2個だけもち,かつ負性抵抗を示すもの

バイポーラ半導体装置で3以上のPN接合を持つもの,例.サイリスタ,プログラムできるユニジャンクショントランジスタ,または4以上の電極をもつもの,例.シリコン制御スイッチ,または同一伝導領域に接続された2以上の電極をもつもの,例.ユニジャンクショントランジスタ (38)

国際特許分類[H03K17/56]に分類される特許

71 - 80 / 199

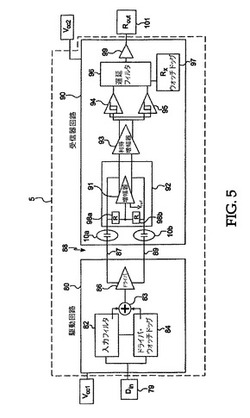

容量性信号結合を用いた高電圧駆動回路及び関連する装置及び方法

【課題】ほぼ1つの面内に形成された駆動電極と感知電極とを備えた高電圧駆動回路を提供する。

【解決手段】装置は、駆動回路と感知回路との間の信号の転送を、駆動電極および感知電極を介して容量性手段によって行い、かつIGBTなどの高電圧装置を高電圧トランジスタを使用せずに駆動することが可能にされ、これにより高電圧ゲート駆動回路及びICを製造する場合、SOIなどの高価な製造工程を使用する必要がなくなる。

(もっと読む)

電力スイッチグループ化

電力モジュレータは複数の切換パルスジェネレータ部(22)と、電源装置(10)と、変圧器装置(30)を含む。スイッチ制御部(24)が上記複数の切換パルスジェネレータ部(22)に接続され、それ等をターンオン及び/又はターンオフするための制御信号を供給する。スイッチ制御部(24)は第1のサブセットの切換パルスジェネレータ部を第1の瞬時にターンオン及び/又はターンオフするための制御信号を供給し、第2のサブセットの切換パルスジェネレータ部を、第1の瞬時とは異なる第2の瞬時にターンオン及び/又はターンオフするための制御信号を供給するようになっている。第2のサブセットは第1のサブセットとは異なるものとする。  (もっと読む)

(もっと読む)

半導体スイッチモジュール

【課題】当該半導体スイッチモジュールが適用された機器の誤動作や自己の故障を防止できる半導体スイッチモジュールを提供する。

【解決手段】外部からの駆動信号に含まれる所定幅以下のパルスを除去するフィルタ回路12〜16、と、フィルタ回路で所定幅以下のパルスが除去された駆動信号をゲート信号としてオン/オフする半導体スイッチ19とを備える。

(もっと読む)

半導体集積回路装置

【課題】パワー半導体素子を有する半導体集積回路装置において、プルダウン用半導体素子を確実に動作させてパワー半導体素子をオフ状態にすること。

【解決手段】プルダウン用トランジスタ26のゲート端子と、ゲート信号を入力とするしきい値回路25の間に、バッファ回路29が設けられる。バッファ回路29には、外部のバッテリー電源23からパワー半導体素子24の出力端子に印加される電圧が抵抗型素子28を介して供給される。しきい値回路25から出力されるオン信号のレベルがバッファ回路29でプルダウン用トランジスタ26のしきい値よりも高い電圧に変換されることによって、ゲート信号のレベルが低くても、プルダウン用トランジスタ26が確実に動作し、パワー半導体素子24がオフ状態となる。

(もっと読む)

ゲート駆動装置

【課題】本発明は、外付け部品を要することなく、出力トランジスタのゲート電圧を適切にクランプすることが可能なゲート駆動装置を提供することを目的とする。

【解決手段】本発明に係るゲート駆動装置は、出力トランジスタTrのゲート電圧VGを駆動するものであって、ゲート電圧VG(図1ではゲート電圧VGの分圧電圧Va)と所定の閾値電圧Vbとの高低関係を検出する電圧検出回路41と、電圧検出回路41の検出結果に基づいて出力トランジスタTrのゲートと電源電圧VCCの印加端との間を導通/遮断するスイッチ51と、を有して成る構成とされている。

(もっと読む)

半導体装置の駆動装置及びその駆動方法

【課題】

本発明の課題は、スイッチング素子の駆動回路及び電力変換装置の発熱抑制及びスイッチング時の信頼性の両立を実現することである。

【解決手段】

電圧駆動型のスイッチング素子用駆動装置であって、前記スイッチング素子のゲート電極に電気的に接続され、かつ該ゲート電極にゲート電圧を印加するための駆動回路部と、前記ゲート電極に印加されたゲート電圧を検出する電圧検出部と、前記ゲート電極に印加されたゲート電圧の変化率を検出する電圧変化率検出部と、前記電圧検出部の検出結果及び前記電圧変化率検出部による検出結果に基づいて、前記駆動回路部を制御し、前記ゲート電極に印加されるゲート電圧を変化させるように前記駆動回路部を制御する制御回路部と、を備えるスイッチング素子用駆動装置を提供する。

(もっと読む)

半導体装置

【課題】ダイオード内蔵IGBTを備えた半導体装置において、ダイオード素子とIGBT素子のゲート信号との干渉を回避してダイオードの順方向損失増加を防止する。

【解決手段】メイン用のダイオード素子22aに流れる電流を電流検出用のダイオードセンス素子22bおよびセンス抵抗30にて検出する。他方、フィードバック回路部40にてセンス抵抗30の両端の電位差Vsがモニタされると共に、当該電位差Vsに基づいてダイオード素子22aに電流が流れているか否かが判定される。そして、ダイオード素子22aに電流が流れていると判定された場合、フィードバック回路部40からIGBT素子21aの駆動を停止させる停止信号がAND回路10に入力され、AND回路10にてIGBT素子21aの駆動が停止される。

(もっと読む)

半導体集積回路装置

【課題】 レベルシフト回路のオン耐圧について配慮し、オン耐圧を高めて破壊を防止する回路を提供することにある。

【解決手段】 高圧出力DOUTがHiの状態では、N型トランジスタHVN1、P型トランジスタHVP2はOFF状態、N型トランジスタHVN2、P型トランジスタHVP1はON状態であり、HVN1のドレイン−ソース間には高電圧VHが印加されている。高圧出力DOUTをLoに遷移させる過程において、N型トランジスタHVN1のゲート電位を一旦、VDDとGNDの中間状態に置き、N型トランジスタHVN1のドレイン−ソース電圧を下げた後、ゲート電圧をVDDに上昇させる。これにより、N型トランジスタHVN1のドレイン−ソース間電圧が高く、且つ、ドレイン電流が大きい状態を回避し、レベルシフト回路のオン耐圧を高めて破壊を防止する。

(もっと読む)

半導体装置

【課題】スイッチング素子を強制的に遮断する際、誘導負荷の大きさによらず所望のクランプ電圧で、精度よく誘導起電力の大きさを抑制する技術を提供する。

【解決手段】IGBT1(スイッチング素子)のゲート−コレクタ間に第1クランプ素子3が、ゲートに放電抵抗部16が接続される。タイマー回路7は、IGBT1をオン状態に駆動するオン信号の入力が所定時間以上継続すると、Hレベルの信号をNMOSトランジスタ26及びゲート駆動回路9に出力する。ゲート駆動回路9は、タイマー回路7からの信号に基づいてIGBT1をオフ状態に駆動する。NMOSトランジスタ26は、タイマー回路7からの信号に応答して、選択的に第2クランプ素子28をIGBT1のゲート−コレクタ間に接続する。

(もっと読む)

インバータ装置

【課題】

パワーモジュールに大きな電流を流すインバータ装置であっても、高電位側IGBTを駆動する信号の基準電位端子とゲート駆動ICの基準電位端子間の逆サージを効果的に回避する。

【解決手段】

高電位側のIGBT121及び低電位側のIGBT123を有するIGBTモジュール113と、高電位側IGBT121及びIGBT123を駆動する信号を出力するゲート駆動IC101と、ゲート駆動IC101の高電位側IGBT駆動信号用基準電位端子106と低電位側のIGBT123のコレクタ端子117との間に設けられた容量128と、ゲート駆動IC101の高電位側IGBT駆動信号用基準電位端子106と高電位側IGBT121のエミッタ端子116との間に設けられた抵抗127と、を有するインバータ装置。

(もっと読む)

71 - 80 / 199

[ Back to top ]