国際特許分類[H03K5/26]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 入力信号特性,例.傾斜,積分,にもとづいてパルスまたはパルス列をお互いに比較するための2つ以上の入力と1つの出力をもつ回路 (310) | 入力信号特性が持続時間,間隔,位置,周波数または順序であるもの (305)

国際特許分類[H03K5/26]に分類される特許

21 - 30 / 305

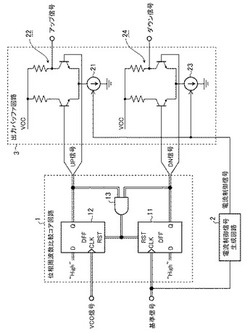

位相周波数比較回路

【課題】雑音特性及び高速動作を維持しながら、消費電力を削減することができる位相周波数比較回路を得ることを目的とする。

【解決手段】出力バッファ回路3が、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力する。

(もっと読む)

位相調整回路及び位相調整方法

【課題】LSIチップ面積の増大を抑制しつつ、製造ばらつきや使用条件の影響を受けない安定的な位相調整を実現する

【解決手段】入力クロックと出力クロックの位相差を調整する位相調整回路を以下のように構成する。その位相調整回路は、出力クロックに遅延を付加するクロック遅延回路と、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスを入力として受け、パルス除去幅設定値によって遅延素子の段数を変化させて、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスの幅を検出する位相差検出回路とを有することが好ましい。そして、位相差検出回路で検出した入力クロックと出力クロックの位相差が入力クロックに対して目標の位相差になるようにクロック遅延回路にて出力クロックに遅延を付加する。

(もっと読む)

遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法

【課題】簡易な処理によって遅延素子の遅延情報を出力する遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法を提供すること。

【解決手段】本発明にかかる遅延検出回路10は、基準信号生成部11と、遅延チェーン12と、保持部13と、を備える。基準信号生成部11は、クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくともクロック信号の一周期の間は第2のレベルが維持される基準信号を生成する。遅延チェーン12は、多段接続された複数の遅延ゲート12−1〜12−nを有し、基準信号が入力される。保持部13は、クロック信号に同期して複数の遅延ゲート12−1〜12−nの出力信号を保持し、前記遅延手段の遅延情報を出力する。

(もっと読む)

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

遷移検出回路

【課題】

簡潔な構成でコード信号の遷移を検出する遷移検出回路を提供する。

【解決手段】

1ビットずつ遷移するグレイコードの遷移を検出する検出回路において、グレイコードのビットに含まれる1の個数が偶数であるか奇数であるかによって変化する信号を出力する組み合わせ論理回路と、組み合わせ論理回路の出力が変化したときに有効となる遷移検出信号を生成する比較回路とを備える。

(もっと読む)

差動入力インターフェース回路、表示ドライバIC、表示パネルモジュールおよび画像表示装置

【課題】高速に伝送されてくるデータを安定して受信する差動入力インターフェース回路を提供する。

【解決手段】一対の差動信号を受信して正相データ信号PA11を出力する第1の差動アンプ103と、一対の差動信号を受信して負相データ信号NA11を出力する第2の差動アンプ104と、一対の差動クロック信号を受信して正相クロック信号FX11を出力する第3の差動アンプ105と、正相データ信号PA11と負相データ信号NA11とを正相クロック信号FX11に同期してラッチすることにより、ラッチ出力信号PDを出力するデータラッチ回路303と、ラッチ出力信号PDよりシングルエンドのデータ信号L13を生成するデータ生成回路302とを備える。

(もっと読む)

同期信号処理装置

【課題】回路の小面積化、低消費電力化を図ることが可能であり、しかも温度依存性の影響を受けない安定した位相比較が可能な同期信号処理装置を提供する。

【解決手段】水平同期信号を同期クロックで同期させ、当該同期クロックのタイミングでデジタルデータとして出力する時間デジタル変換器(TDC)と、同期クロックをカウントして参照クロックを生成する参照クロック生成部と、TDCによるデジタルデータと参照クロックの位相比較を行うことにより位相差情報を得るデジタル位相比較器と、デジタル位相比較器の位相差情報に応じて上記参照クロックとTDCによる水平同期信号のデジタルデータの位相が一致するように周波数が制御される同期クロックを生成する同期クロック生成装置と、を有する。

(もっと読む)

クロック生成装置および電子機器

【課題】レプリカ回路が不要で、小面積化を図ることが可能であり、しかもジッタの増加を防止でき、低ジッタ出力クロックを生成することが可能なクロック生成装置および電子機器を提供する。

【解決手段】アキュムレータの値に応じて目標とするNCOクロックと実際のNCOクロックとの位相差を取得する位相差取得部と、入力クロックに位相同期した信号に応じて入力クロックに複数の遅延を与えた複数の遅延クロックを生成する遅延同期回路と、位相差取得部の位相差情報を受けて複数の遅延クロックから目標とする上記NCOクロックの位相に近づくような遅延が与えられた遅延クロックを選択し、選択クロックとして出力する選択部と、選択部で選択された上記選択クロックに上記NCOクロックを同期させて出力クロックを得る第2の同期回路とを有する。

(もっと読む)

CDR回路

【課題】線形位相比較器を用いながら、チャージポンプやVCO等のアナログ回路を不要とすることができ、回路面積を抑えたCDR回路を提供する。

【解決手段】位相比較器902は、データエッジ検出回路111〜114により伝送データのエッジを検出し、データエッジマスク回路115〜118、サンプリング回路119〜122、低域通過型フィルタ123〜126、及びアナログ・デジタル変換回路127〜130により、伝送データのエッジを検出したときの再生クロックの電圧を検出し、検出した電圧に基づいて再生クロックの位相調整を行う。

(もっと読む)

時間差加算器を含むシステムオンチップ、時間差累算器を含むシステムオンチップ、シグマ−デルタタイムデジタル変換器、デジタル位相ロックループ、温度センサ、及びシステムオンチップ

【課題】 入力信号間の時間差を加算する時間差加算器を含むシステムオンチップを提供する。

【解決手段】 時間差加算器100は、第1入力信号SIN1、第2入力信号SIN2、第3入力信号SIN3、及び第4入力信号SIN4に応答して第1出力信号SOUT1及び第2出力信号SOUT2を生成する。時間差加算器100は、第1入力信号SIN1と第2入力信号SIN2との間の第1時間差TD1、及び、第3入力信号SIN3と第4入力信号SIN4との間の第2時間差TD2を加算することによって、第1時間差TD1と第2時間差TD2との和に相応する時間差(TD1+TD2)を有する第1出力信号SOUT1及び第2出力信号SOUT2を出力する。これにより、低い電源電圧環境において、時間ドメインで信号処理を遂行することができ、性能を向上させることができる。

(もっと読む)

21 - 30 / 305

[ Back to top ]