国際特許分類[H03K5/26]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 入力信号特性,例.傾斜,積分,にもとづいてパルスまたはパルス列をお互いに比較するための2つ以上の入力と1つの出力をもつ回路 (310) | 入力信号特性が持続時間,間隔,位置,周波数または順序であるもの (305)

国際特許分類[H03K5/26]に分類される特許

11 - 20 / 305

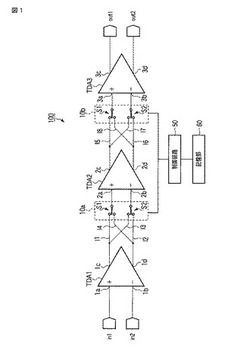

時間差増幅回路

【課題】時間差増幅回路の時間差オフセットを低減する。

【解決手段】複数の時間差増幅器が多段接続された時間差増幅回路100であって、複数の時間差増幅器は、第1の正入力端子1a、第1の負入力端子1b、第1の正出力端子1c及び第1の負出力端子1dを有する第1の時間差増幅器TDA1と、第2の正入力端子2a、第2の負入力端子2b、第2の正出力端子2c及び第2の負出力端子2dを有し、第1の時間差増幅器の出力信号が入力される第2の時間差増幅器TDA2と、第2の正入力端子2aに第1又は第4の配線I1,I2を接続させる第1の選択素子S1と、第2の負入力端子2bに第2又は第3の配線I2、I3を接続させる第2の選択素子S2を有する選択回路10aと、選択回路10aを制御する制御回路50を具備する。

(もっと読む)

位相同期ループのための線形位相周波数検出器およびチャージポンプ

【課題】位相同期ループ(PLL)における位相周波数検出器およびチャージポンプの線形動作を達成する。

【解決手段】位相周波数検出器は、基準信号とクロック信号とを受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、upおよびdownの信号であってもよいし、それぞれ、downおよびupの信号であってもよい。位相周波数検出器は、予め定められた量の分、第1の信号を遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、リセット信号を用いて第1および第2の信号をリセットすることができる。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。

(もっと読む)

PLL回路

【課題】低消費電力のPLL回路を提供する。

【解決手段】位相比較回路11は、基準信号と、フィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号(UP信号とDN信号)をチャージポンプ12に供給し、バイアス回路16は、チャージポンプ12にバイアス電流を供給し、制御回路17は、2種の位相差信号のうち一方または両方が活性化状態のときにバイアス回路16の動作を行わせ、2種の位相差信号の両方が非活性化状態のときに、バイアス回路16を停止させる。

(もっと読む)

位相検出回路及び検査方法

【課題】入力信号の位相の同相/反転関係を検出する位相検出回路であって、検出可能な信号速度が制限されることを回避することが可能な位相検出回路を提供する。

【解決手段】ギルバートセルと、このギルバートセル内の下段側に位置する第1の差動対(101、102)に対して並列関係に設けられた第2の差動対(120、121)と、第1の差動対に電流を供給する第1の電流源(100)とは別に設けられ、第2の差動対に電流を供給する第2の電流源(130)と、第1の電流源と第2の電流源とのいずれかのみが動作するように制御する制御回路(140)とを備え、第1の電圧信号は第1の差動対の正側電圧入力端子と第2の差動対の負側電圧入力端子に入力され、第1の電圧信号と相補の関係にある第2の電圧信号は第1の差動対の負側電圧入力端子と第2の差動対の正側電圧入力端子に入力されている位相検出回路。

(もっと読む)

集積回路

【課題】電源ノイズが存在する環境下において、位相同期回路の出力信号の特性劣化を軽減する。

【解決手段】基準信号源は、基本周波数を有する基準信号を生成する。位相同期回路102は、制御電圧に応じた周波数の信号を生成する電圧制御発振器106と、前記周波数の信号をN分周して第1分周信号を生成する第1分周器107と、第1分周信号と基準信号との位相差を検出する位相検出器103と、チャージポンプ104と、ループフィルタ105と、を含む。第2分周器は、電圧制御発振器により生成された信号をM分周して第2分周信号を生成する。信号処理回路は、第2分周信号に同期して動作する。基本周波数のK倍と、第2分周信号の周波数との差分の絶対値が、電圧制御発振器の入力から位相同期回路の出力までの伝達関数によって表される帯域通過フィルタの低域遮断周波数以下または高域遮断周波数以上となるように、NおよびMの値が決定されている。

(もっと読む)

基準信号生成装置

【課題】 回路規模を増大させずに複数の外部基準信号を用いて所望の基準信号を生成でき、アンロック時にも安定した基準信号を出力する基準信号生成装置を提供する。

【解決手段】 分周された外部基準信号と分周された電圧制御発振器5の出力との位相を比較する位相比較器32を備え、複数の異なる周波数の外部基準信号を入力可能とし、可変フィルタ10が入力信号を帯域制限し、検波回路11が可変フィルタ出力の信号レベルを検出し、レベル判定回路12が、可変フィルタ10にいずれかの外部基準信号の周波数を通過させる帯域を設定し、信号レベルが適正範囲であれば、入力された外部基準信号の周波数を当該通過帯域の周波数として特定し、第1の分周器31に当該周波数に応じた分周値を設定すると共に、切替器6を位相比較器31側に切り替え、適正範囲外であれば、切替器6を固定電圧生成装置7側に切り替える基準信号生成装置としている。

(もっと読む)

半導体装置

【課題】サンプル間、温度等の変位に伴い発生するロック位相の変動を補正し、ロック位相を一定とすることができるDLLを備えた半導体装置を提供する。

【解決手段】位相検出回路(PD)105を構成する複数のMOSFETのうち所定のMOSFETのバックゲート電位を変更するPDバックゲート電位変更回路106と、温度センサ107と、サンプル別閾値電圧(Vt)情報を記憶したFuse(ヒューズ)108を備える。温度センサ107の温度情報、Fuse(ヒューズ)108に記憶されたサンプル別閾値電圧(Vt)情報は、PDバックゲート電位変更回路106に読み出され、閾値電圧を制御し、ロック位相の変動を補正する。

(もっと読む)

位相比較装置

【課題】ステップ応答収束時間だけ待つ必要なく積分値を抽出し、また、入力信号の周波数が既知でなくても抽出した積分値に応じて位相差を演算する位相比較装置を得る。

【解決手段】分周器4が入力信号の周波数を2分周し、積分器5が排他的論理和回路3により生成されたパルスを分周器4により設定された周期分積分し、基準積分器7が既知の一定レベルの基準信号を分周器4により設定された周期分積分し、信号処理部10が積分器5および基準積分器7による積分値に応じて位相差を演算するように構成したので、入力信号の周波数の1/2倍の周波数の整数倍の周波数にヌル点のできるsyncフィルタ特性が形成されることを利用し、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。また、2つの入力信号の周波数が既知でなくても、2つの入力信号の位相差を演算することができる。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

遅延ロックループ/フェーズロックループにおける移相処理

【課題】

本開示は遅延ロックループ(DLL)及びフェーズロックループ(PLL)における移相処理に関する。

【解決手段】

DLLまたはPLLにおけるチャージポンプは、出力ノードに並列に接続されたキャパシタを備える。一次電流スイッチング回路は、ソース電流でキャパシタを充電し、シンク電流でキャパシタを放電する。補助ソース回路は、大きさの範囲を有する正の位相生成電流をソースする。正の移相生成電流の大きさは、少なくとも1つのソース選択信号により決定される。補助シンク回路は、大きさの範囲を有する負の移相生成電流をソースする。前記負の移相生成電流の大きさは、少なくとも1つのシンク選択信号により決定される。

(もっと読む)

11 - 20 / 305

[ Back to top ]