国際特許分類[H03L7/197]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 間接的な周波数の合成,すなわち周波数または位相ロックループを用いる予じめ決められた多数の周波数の内の所望の一つを発生するもの (528) | ループの中に分周器または計数器を用いるもの (427) | ループをロックするために時間差を用いるもの,適時変化可能な数値間を計数する計数器,または適時変化可能な係数によって分周する分周器,例.非整数の周波数分周を得るもの (112)

国際特許分類[H03L7/197]の下位に属する分類

国際特許分類[H03L7/197]に分類される特許

1 - 10 / 94

ディジタル制御発振装置および高周波信号処理装置

【課題】発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供する。

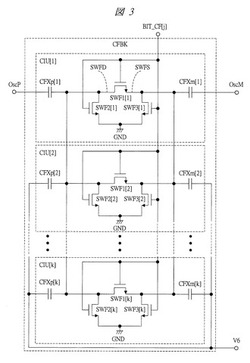

【解決手段】例えば、複数の単位容量ユニットCIU[1]〜CIU[k]を用いて分数容量を実現する。CIU[1]では、容量素子CFXp[1],CFXm[1]の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、CIU[2]〜CIU[k]では、容量素子CFXp([2]〜[k]),CFXm([2]〜[k])の一端が固定電圧V6に接続される。CIU[1]〜CIU[k]の一方の容量素子の他端は共通接続され(SWFD)、他方の容量素子の他端も共通接続される(SWFS)。そして、CIU[1]〜CIU[k]内の各スイッチ(SWF1〜SWF3)のオン・オフは共通に制御される。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】DNLの低減を実現可能なディジタル制御発振装置を提供する。

【解決手段】例えば、発振出力ノードOscP,OscM間に並列に結合されるアンプ回路ブロックAMPBK、コイル素子LP,LM、複数の単位容量ユニットCIU等を備え、各CIUは、容量素子CIp,CImと、当該CIp,CImを発振周波数の設定パラメータとして寄与させるか否かを選択するスイッチSWIを備える。ここで、SWIは、デコーダ回路DECからのオン・オフ制御線BIT_CIによって駆動され、当該BIT_CIは、シールド部GSによってOscP,OscMとの間でシールドされる。

(もっと読む)

位相同期ループのための線形位相周波数検出器およびチャージポンプ

【課題】位相同期ループ(PLL)における位相周波数検出器およびチャージポンプの線形動作を達成する。

【解決手段】位相周波数検出器は、基準信号とクロック信号とを受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、upおよびdownの信号であってもよいし、それぞれ、downおよびupの信号であってもよい。位相周波数検出器は、予め定められた量の分、第1の信号を遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、リセット信号を用いて第1および第2の信号をリセットすることができる。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。

(もっと読む)

無線送信機

【課題】局部発振器の位相雑音性能の改善により、送信信号に含まれる隣接チャネル漏洩信号を大幅に低減することができる無線送信機を提供する。

【解決手段】ディジタルデータ信号を出力するデータ信号生成回路と、ディジタルデータ信号をディジタル/アナログ変換し、中間周波数のIF信号を出力するディジタル/アナログ変換回路と、IF信号と局部発振器から出力されるローカル信号とをミキシングし、無線周波数のRF送信信号を出力する直交ミキサ回路とを備えた無線送信機において、データ信号生成回路は、ディジタル/アナログ変換回路から出力されるIF信号の周波数が送信チャネルに応じて切り替わるディジタルデータ信号を出力する構成であり、局部発振器は、RF送信信号のチャネル周波数間隔のn倍(nは3以上の整数)の周波数間隔のローカル信号を切り替えて出力する構成である。

(もっと読む)

高周波信号処理装置および無線通信システム

【課題】ディジタル型PLL回路を備えた高周波信号処理装置および無線通信システムにおいて、スプリアスの影響を低減する。

【解決手段】例えば、ディジタル位相比較部DPFD、ディジタルロウパスフィルタDLPF、ディジタル制御発振部DCO、マルチモジュールドライバ部(分周部)MMDを備えたディジタル型PLL回路において、DLPFのクロック信号CKDLPFのクロック周波数が複数の選択肢の中から選択可能に構成される。当該クロック周波数は、基準発振信号Frefの整数倍の周波数の中から、DCOの発振出力信号RFdcoに対して規格上のどの周波数帯を設定するかに応じて選択される。

(もっと読む)

発振回路およびそれを用いた電子機器

【課題】スペクトルのピークを抑制する。

【解決手段】発振回路2は、基準クロック信号CKREFを受け、出力クロック信号CKOUTを生成する。プログラマブル分周器18は、その分周比が少なくとも2値で切りかえ可能に構成され、出力クロック信号CKOUTを設定された分周比で分周し、分周クロック信号CKDIVを生成する。位相比較器10は、基準クロック信号CKREFと分周クロック信号CKDIVの位相差に応じた位相差信号S1を生成する。ループフィルタ12は、位相差信号S1を平滑化する。VCO(電圧制御発振器)14は、ループフィルタ12から出力される位相差信号S2に応じた周波数で発振し、出力クロック信号CKOUTを生成する。制御部20は、プログラマブル分周器18の分周比を、時分割的に切りかえることにより出力クロック信号CKOUTのスペクトルを拡散させる。

(もっと読む)

周波数シンセサイザ

【課題】少数点逓倍の精度を向上させ、累積ジッタを低減した周波数シンセサイザを提供する。

【解決手段】位相比較器1と、チャージポンプ2と、ローパスフィルタ3と、電圧制御発振器4と、該電圧制御発振器の出力クロック信号を小数点分周して前記帰還クロック信号を生成する帰還回路とを備える。帰還回路は、電圧制御発振器4の出力クロック信号を分周する可変分周器5と、電圧制御発振器4の8相のクロック信号から1つの位相のクロック信号を選択するマルチプレクサ7と、マルチプレクサ7で選択した特定の位相のクロック信号により可変分周器5のクロック信号をリタイミングするリタイミング回路(DFF回路8,9とアンド回路10)とを備える。

(もっと読む)

可変分周装置

【課題】クロック信号が高速化した場合でも対応することのできる可変分周装置を得る。

【解決手段】可変分周回路101は、クロック信号Clk_aを入力し、クロック信号Clk_aに対するP(Pは2以上の整数)またはP+1の分周した信号Do1を出力する。可変分周回路102は、クロック信号Clk_aと逆相になるクロック信号Clk_bを入力し、クロック信号Clk_bに対するPまたはP+1の分周した信号Do2を出力する。経路切り替え回路103は、信号Do1,Do2を入力し、経路選択信号MuxContにより信号Do1,Do2のうちいずれか一方を選択し出力する。

(もっと読む)

アキュムレータ型フラクショナルN−PLLシンセサイザおよびその制御方法

【課題】フラクショナル分周器の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制したアキュムレータ型フラクショナルN−PLLおよびその制御方法を実現する。

【解決手段】アキュムレータ型フラクショナルN−PLLシンセサイザ100を、その参照信号入力側の位相検出器の前段にアキュムレータ120からの誤差信号によって上記参照信号に対し位相調整を行う位相調整回路130を介挿して構成し、出力段のVCO114の出力を前段側にフィードバックするフラクショナル分周器115の出力である帰還信号と、上記位相調整された参照信号との両信号の位相差が生じないようにして、該両信号の位相差に応じた出力を得る位相検出器111の出力によってチャージポンプ112が駆動されないようにすることによって、フラクショナル分周器115の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制するように構成する。

(もっと読む)

PLL周波数シンセサイザ

【課題】 フラクショナルN方式のPLL(Phase-locked loop;位相同期回路)周波数シンセサイザにおいて生じる、フラクショナルスプリアスを抑圧する。

【解決手段】 可変分周器の分周数を2つ以上の整数値で時間的に切り替えるフラクショナルN方式のPLL周波数シンセサイザにおいて、電圧制御発振器2とループフィルタ7の間に、抑圧周波数および減衰量の制御を可能とする可変ノッチフィルタ8を設けることで、フラクショナルスプリアスを抑圧することができる。

(もっと読む)

1 - 10 / 94

[ Back to top ]