富士通セミコンダクター株式会社により出願された特許

91 - 100 / 2,507

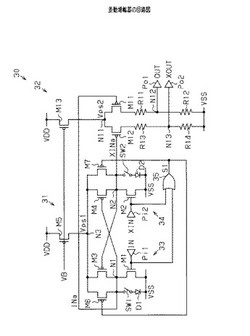

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

半導体装置

【課題】出力信号を高速に変化させかつオーバーシュートやアンダーシュートを抑制できるようにする。

【解決手段】入力信号を反転して出力する主ドライバ11に加えて、補助ドライバ12を設け、入力信号の電圧変化に応じて出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、変化開始から主ドライバの出力信号がある電圧レベルを超えるまでの期間では信号変化を補助するように制御部15により補助ドライバの動作を制御し、主ドライバの出力信号がある電圧レベルを超えてから第2の電圧レベルになるまでの期間に信号変化を抑制するように制御部により補助ドライバの動作を制御するようにして、出力信号における信号変化の高速性を向上させ、かつオーバーシュートやアンダーシュートを抑制できるようにする。

(もっと読む)

極紫外露光マスク用防塵装置及び露光方法

【課題】EUVリソグラフィ時のEUV露光マスクの表面での炭素系薄膜及び酸化物の生成を抑制することができる極紫外露光マスク用防塵装置及び露光方法を提供する。

【解決手段】防塵装置51には、極紫外露光マスク61に対する防塵部材52と、極紫外露光マスク61と防塵部材52との間の空間に、防塵部材52側が極紫外露光マスク61側よりも高電位となる電場を生じさせる電場生成手段58と、が設けられている。

(もっと読む)

電流モード回路の入力インピーダンスを維持するシステム及び方法

【課題】 電流モード回路の入力インピーダンスを維持するシステム及び方法が提供される。

【解決手段】 本開示の幾つかの実施形態によると、回路は、電流モード入力信号を受信する入力ノード、及び前記入力ノードに通信可能に結合された入力装置を含む入力段、を有する。入力装置は、入力ノードにおいて入力信号を受信する。さらに、回路は、入力段に通信可能に結合され、入力装置にバイアス電流を供給するよう構成されたバイアス回路を有する。バイアス回路は、入力ノードと関連するフィードバックループを通じてバイアス電流の少なくとも一部を入力信号から除去して、入力信号がバイアス電流の少なくとも一部を除去されて入力装置に受信されるように構成される。回路は、入力段に通信可能に結合され、入力信号に基づき電流モード出力信号を出力するよう構成された出力段を更に有する。

(もっと読む)

半導体集積回路及び回路状態監視回路

【課題】プロセッサ部の負荷を低減する。

【解決手段】半導体集積回路10は、プロセッサ部11と回路部12と回路状態監視回路13を有する。回路部12は、自身の回路状態を示す状態情報を記憶する記憶部12aを有しており、回路状態監視回路13は、その状態情報を監視し、状態情報の所定の変化を検出すると、プロセッサ部11に対する割り込みを発生することで、プロセッサ部11が回路部12に対するポーリングを行わなくて済むようになる。これによって、プロセッサ部11の負荷を低減できる。

(もっと読む)

再送制御方法、通信装置および無線通信システム

【課題】必要なメモリサイズを低減すると共に、帯域使用効率を上げてスループットの向上を図る。

【解決手段】第1データ単位Sub-burst#で再送を行う第1データ再送機能HARQと、前記第1データ単位の一部の第2データ単位SDU#で再送を行う第2データ再送機能ARQを併用してデータ再送を制御する再送制御方法であって、前記第2データ単位のブロックの欠落を検出(ST502)し、前記欠落ブロックの直後のブロックの受信フレーム番号と、前記第1データの再送完了に要するフレーム数から、前記欠落ブロックに対応する第1データ単位の再送状況を推定(ST504)し、前記欠落ブロックの前記第1データ単位の再送状況に応じて、前記第2データの受信結果の応答メッセージを送信(ST505,ST506)する。

(もっと読む)

半導体集積回路検査装置,および,半導体集積回路の検査方法

【課題】テスト時間をより短縮するテストパターンを作成する半導体集積回路検査装置,および,半導体集積回路の検査方法を提供する。

【解決手段】半導体集積回路検査装置20は,テストパターンを複数の区間に分割した分割テストパターン毎に,分割テストパターンに対する論理演算を異なる周期のクロック信号に基づき半導体集積回路に実行させることにより得られた半導体集積回路31の故障判定結果に基づき,分割テストパターン毎の最適クロック周期を算出する最適周期算出部213と,テストパターンと,テストパターンに係る分割テストパターン毎の最適クロック周期を有するテストパターンファイルを生成する新テストパターンファイル生成部214を有する。

(もっと読む)

電子回路、および実装基板

【課題】出力信号の電圧レベルの遷移の方向に応じて、電源線や接地線を通らず寄生インダクタンス成分の影響を受けない電流を加算して信号の電圧レベルの遷移をアシストすることにより、SSOノイズを抑制することが可能な電子回路および実装基板の制御方法を提供すること。

【解決手段】出力回路1は、出力バッファ4と、出力バッファ4から出力される出力信号が伝搬する出力線と、出力バッファ4に電源を供給する電源線VdeLあるいは接地線VgLの少なくとも何れか一方と、出力線と電源線VdeLあるいは接地線VgLとにより囲まれる磁心50と、磁心50に巻回される制御コイル51と、出力信号の遷移を前もって検出し検出結果に応じて制御コイル51への電流供給を制御するコイル電流制御回路3とを備え、出力信号の遷移方向に応じて、制御コイル51からの電磁誘導により出力線の信号遷移をアシストするアシスト電流を流す。

(もっと読む)

半導体装置

【課題】半導体装置の効率的な放熱を行う。

【解決手段】第一の半導体チップ及び第二の半導体チップを備える半導体装置であって、前記第一の半導体チップは、回路が形成された第一の半導体基板と、前記第一の半導体基板の回路形成面から前記第一の半導体基板の回路形成面の反対面である裏面を貫通する貫通電極と、を有し、前記第二の半導体チップは、回路が形成された第二の半導体基板と、前記第二の半導体基板の回路形成面に形成された層間絶縁膜と、前記層間絶縁膜上に形成された金属柱と、前記金属柱上に形成されたバンプと、を有し、前記バンプは、前記第一の半導体基板の裏面であって前記貫通電極が形成されていない領域に接触し、前記第一の半導体基板とは電気的に接続していない。

(もっと読む)

送信装置、通信システム、及びデータ送信方法

【課題】ゼロウインドウ状態でゼロウインドウプローブの送信を繰り返すことによるスループット低下を回避する。

【解決手段】送信装置は、受信装置からウインドウサイズの当該単位容量を示すデータを受信し、データパケットを送信するごとに、当該データパケットに応答して前記受信装置から送信される、前記ウインドウサイズを含む確認応答を受信し、前記ウインドウサイズがゼロのとき、前記単位容量未満のデータサイズの検査用データパケットを送信し、当該検査用データパケットに応答して前記受信装置が送信する前記ウインドウサイズがゼロであっても、当該ウインドウサイズを含む前記確認応答が前記検査用データパケットが前記メモリに格納されたことを示すときには、前記検査用データパケットのデータサイズ以上であって前記単位容量未満の第1のデータサイズの前記データパケットを送信する。

(もっと読む)

91 - 100 / 2,507

[ Back to top ]