富士通セミコンダクター株式会社により出願された特許

101 - 110 / 2,507

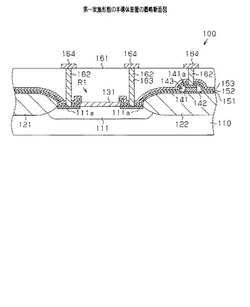

半導体装置の製造方法

【課題】回路素子の素子特性の変動を抑制すること。

【解決手段】半導体基板110には、拡散領域111を有する抵抗素子(回路素子)R1が形成されている。拡散領域111を含む半導体基板110の上には、層間絶縁膜161が形成される。拡散領域111のシリサイド層(コンタクト部)111aは、コンタクトプラグ162を介して層間絶縁膜161上の配線と接続される。拡散領域111の上には、コンタクトホール163を形成するためのエッチングストッパ膜152が形成されている。このエッチングストッパ膜152は、拡散領域111上の保護絶縁膜131に対応する部分が除去され、開口が形成されている。

(もっと読む)

オーディオ信号符号化方法および装置

【課題】チャネル間の音質のバランスを維持しながら音質が向上したオーディオ信号符号化方法および装置の実現。

【解決手段】オーディオ信号符号化装置であって、知覚エントロピー算出部21と、知覚エントロピーに応じて、各チャネルの使用可能ビット数を決定するビット配分部22と、窓判定部23と、使用可能ビット数を補正する補正部24と、各チャネルのオーディオ信号を、補正された使用可能ビット数以下となるように順次量子化し、その際にフレーム内で既に量子化されたチャネルの余りビット数を順次後のチャネルに加えながら量子化する量子化部25と、を有し、補正部24は、以前のフレームの窓のタイプごとの量子化ビット使用率を算出する使用率履歴算出部31と、量子化ビット使用率で量子化が行われた場合の各チャネルの使用可能ビット数に対する使用率が等しくなるように補正する補正ビット数算出部32と、を有する。

(もっと読む)

電源装置の駆動回路及び電源装置

【課題】遷移期間においてハイサイドトランジスタQ1がオンしないようにする。

【解決手段】高電位電源ラインと低電位電源ラインとの間に直列に接続されたハイサイドトランジスタとロウサイドトランジスタと,両トランジスタの接続ノードと出力端子との間に設けられたインダクタとを有する電源装置の前記両トランジスタを駆動する駆動回路であって,前記ハイサイドトランジスタのゲートを駆動する第1のゲートドライバと,前記ロウサイドトランジスタのゲートを駆動する第2のゲートドライバとを有し,前記ハイサイドトランジスタがオンでロウサイドトランジスタがオフの第1の状態から,前記ハイサイドトランジスタがオフでロウサイドトランジスタがオンの第2の状態に遷移する遷移期間で,前記第1のゲートドライバは前記ハイサイドトランジスタのゲートを前記低電位電源ラインの電位より低い第1の電圧に駆動する電源装置の駆動回路。

(もっと読む)

半導体装置及びその製造方法

【課題】電子部品を封止する樹脂層の表面にシールド層が設けられる半導体装置の、当該樹脂層からの脱湿性を高める。

【解決手段】半導体装置100cは、基板110と、その基板110上に実装された電子部品120を含む。基板110上の電子部品120は、樹脂層130によって封止され、その樹脂層130の上面及び側面に、電磁波をシールドするシールド層140が設けられる。樹脂層130及びシールド層140には、連通する穴131,141が設けられ、そこにピン180が挿入される。加熱によりピン180が熱膨張すると隙間200ができ、樹脂層130に含まれる水分は、穴131,141及び隙間200を通って外部へと除去される。

(もっと読む)

画像処理装置、撮像装置、撮像システム、及びデータ処理方法

【課題】点滅駆動される被写体を好適に撮影すること。

【解決手段】撮像部22は、1映像記録周期に複数(例えば3つ)のフレームFa,Fb,Fcを出力する。抽出部25は、デモザイク部24から連続的に出力されるフレームのうち、[3n−2]番目(n=1,2,・・・)のフレームFaと、[3n−1]番目のフレームFbとを処理する。合成部27は、デモザイク部24から連続的に出力されるフレームのうち、[3n]番目のフレームFcを処理する。抽出部25は、フレームFa,Fbの画像データから設定色に対応する領域を推定し、その領域に含まれる画素の情報と、領域の情報をメモリ26に格納する。合成部27は、抽出部25がメモリ26に格納した発光部領域のデータを、メモリ26から読み出す。そして、合成部27は、デモザイク部24から出力される合成フレームFcと、発光部領域とを合成して出力フレームFdを生成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】素子面積の増加を抑制しつつ、動作速度が向上する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置は、ボディ領域11a、11bと、ボディ領域11a、11b上にゲート絶縁層12a、12bを介して配置されるゲート電極13a、13bと、ボディ領域11a、11bを挟んで配置される一対のソース/ドレイン領域14a、14b、14cと、を有する電界効果型トランジスタ10a、10bを複数備え、複数のトランジスタ10a、10bは、ボディ領域11a、11b同士が電気的に接続されており、複数のトランジスタ10a、10bの内の一のトランジスタ10aのゲート電極13aのみが、複数のトランジスタ10a、10bの内の何れかのトランジスタのボディ領域と電気的に接続される。

(もっと読む)

シンボルタイミングリカバリ回路

【課題】干渉波による精度の悪化を防止することができるシンボルタイミングリカバリ回路を提供することを課題とする。

【解決手段】第1のフィルタを用いて入力デジタル信号のゼロクロス点及び/又はデータ識別点の補間データを生成する補間器(14)と、第2のフィルタを用いて補間器により生成された補間データを基に入力デジタル信号から前方干渉波を除去し、その除去した信号、第1の識別信号及び第1の誤差信号を出力する前方等化器(21)と、第3のフィルタを用いて補間器により生成された補間データを基に入力デジタル信号から後方干渉波を除去し、その除去した信号、第2の識別信号及び第2の誤差信号を出力する後方等化器(23)と、第2のフィルタのタップ係数、第3のフィルタのタップ係数、第1の識別信号、第1の誤差信号、第2の識別信号及び第2の誤差信号を基に第1のフィルタのタップ係数を生成するタイミング再生部(20)とを有する。

(もっと読む)

スタティックRAM

【課題】動作速度および信頼性を維持しながら、消費電力を低減したSRAMの実現。

【解決手段】複数のワード線WLと、複数のローカルビット線対LBL,LBLXと、複数のローカルビット線対の複数のワード線との交差部に設けられた複数のメモリセルC0-Cmと、複数のローカルビット線対毎に設けられた容量共通化回路BCと、複数の容量共通化回路を接続する共通接続ラインCLNと、複数のローカルビット線対に接続されるグローバルビット線対GBL,GBLXと、を有し、容量共通化回路は、対応するローカルビット線対と共通接続ラインの間に接続された2個のNチャネルトランジスタを有するスタティックRAM。

(もっと読む)

基板搬送装置、半導体製造装置、及び基板搬送方法

【課題】 反りと反発力の大きいウェハであっても、確実に吸着して保持しながら搬送することができる搬送技術を提供することを課題とする。

【解決手段】 基板搬送装置は、基板を吸着保持しながら搬送する搬送ピック40を有する。搬送ピック40の吸着面40aは複数の領域46a,46bに分割され、複数の領域の各々に対して吸着経路が設けられる。制御部60は、吸着経路への負圧の導入を制御して、搬送ピック40による基板の吸着保持動作を制御する。

(もっと読む)

電源電圧設定方法及び電源電圧設定プログラム

【課題】チップごとに適正な電源電圧を設定する。

【解決手段】チップのレイアウトデータ20からクリティカルパスのゲート遅延と配線遅延の遅延比を抽出する(ステップS1,S2)。チップのモニタ回路で実測されたゲート遅延及び配線遅延を、その遅延比に基づき合成して第1遅延値を生成し(ステップS3)、モニタ回路のシミュレーションで得られるゲート遅延及び配線遅延を、その遅延比に基づき合成して第2遅延値を生成する(ステップS4,S5)。このようにゲート遅延、配線遅延、クリティカルパスでの遅延比が考慮された第1遅延値及び第2遅延値に基づいて、チップに適用するチップ電源電圧を設定する(ステップS7)。

(もっと読む)

101 - 110 / 2,507

[ Back to top ]