富士通セミコンダクター株式会社により出願された特許

151 - 160 / 2,507

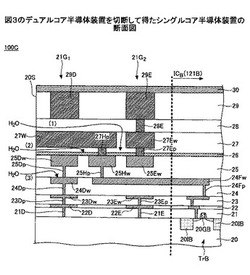

半導体装置および試験方法

【課題】より小さな単位に切り離しも可能なマルチコア半導装置において、前記より小さな単位に切り離した場合に相互接続配線を伝って生じる可能性のある水の侵入を阻止する。

【解決手段】半導体装置は、素子領域を有する半導体基板と、前記素子領域に形成され、第1の開口部を有する内側シールリングと、前記素子領域に形成され、第2の開口部を有する外側シールリングと、前記半導体基板上に形成された、各々配線層を含む複数の層間絶縁膜を積層した積層体よりなる多層配線構造と、前記多層配線構造に含まれる第1の層間絶縁膜とその上の第2の層間絶縁膜の間に形成された耐湿膜と、前記耐湿膜の下側および上側のいずれか一方である第1の側を延在し、前記第1の開口部を通過する第1の部分と、前記耐湿膜の下側および上側の他方である第2の側を延在し、前記第2の開口部を通過する第2の部分と、前記第1の部分と前記第2の部分とを、前記耐湿膜を貫通して接続するビアプラグとを含む配線パターンと、を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体ウェハのダイシングを効率良く、確実にする。

【解決手段】半導体ウェハ2は、裏面にダイアタッチ材25が貼り付けられた状態でダイシングシート27に取り付けられる。ダイシングブレード4は、第1の砥粒31を有し、半導体ウェハ2をダイアタッチ材25と共に切削する。切削時には、冷却水と共に第2の砥粒32が半導体ウェハ2及びダイシングブレード4に供給される。第2の砥粒32は、第1の砥粒31より粒径が大きく、ダイシングブレード4に張り付いたダイアタッチ材25Aを取り除く。

(もっと読む)

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

水晶発振器回路の温度依存性及び処理依存性周波数変動を低減させるシステム及び方法

【課題】無線通信エレメントの発振器に於いて、共振器の温度依存性に対する処理の変動を補償する発振器の提供。

【解決手段】発振器210は、アクティブ・エレメント312と並列に共振器310を含み、共振器は、可変静電容量を有する可変コンデンサ314に結合し、発振器の出力周波数同調を可能にする。所定の温度補償算出器324は温度センサ322からの温度信号に基づき、共振器のロットに対して行われる特徴付けデータを参照して、温度ベースの周波数補償信号を出力する。又、周波数推定器326からの周波数推定信号に基づき、処理補償算出器328は共振器の処理依存性補償を算出して処理ベースの補償信号を出力し、乗算器330は前記周波数補償信号及び前記補償信号に基づき乗算器出力信号を出力し、制御モジュール332は、乗算器出力信号に基づき、制御信号を可変コンデンサに供給し、共振器における温度、処理ベースの変動を補償する。

(もっと読む)

マイクロコンピュータ

【課題】リソースでの無駄な消費電力を削減することができるマイクロコンピュータを提供することを目的とする。

【解決手段】外部から電源を供給されるマイクロコンピュータにおいて,それぞれの所定の機能を有し,外部から供給される前記電源の起動時に電源が供給されない複数のリソースと,前記複数のリソースにバスを介して接続され,前記リソースに前記バスを介してアクセス信号を供給する制御ユニットと,前記複数のリソースにそれぞれ設けられ,電源起動信号に応答して外部から供給される前記電源から対応するリソースにリソース内電源を供給する複数のリソース内電源供給部と,前記複数のリソースにそれぞれ設けられ,前記バスを介して供給されるアクセス信号が対応するリソース宛か否かを検知し,前記アクセス信号が対応するリソース宛の場合に前記電源起動信号を対応するリソース内電源供給部に出力できる電源制御部とを有する。

(もっと読む)

可変利得増幅回路,および可変利得増幅回路を用いた通信装置

【課題】利得ズレを抑制する可変利得増幅回路を提供する。

【解決手段】可変利得増幅回路は,一端が第1の可変利得増幅器11の入力抵抗Ri10 と入力スイッチSWi10との第1の接続ノードN1に接続され,他端が第1の可変利得増幅器の後段側の第2の可変利得増幅器13の演算増幅器OP3の入力端に接続されたバイパススイッチSWb13を有する。

(もっと読む)

量子化装置

【課題】 回路規模の増加を抑制しつつ、複数ビットの量子化信号を生成する。

【解決手段】 量子化装置は、第1クロックの1周期前の量子化信号に基づく量子化誤差と第1信号とに基づいて、第2信号を生成する信号処理部と、第1クロックより高速の第2クロックに同期して動作し、第2信号を第1クロックの1周期以内に量子化し、量子化信号を生成する量子化部とを有している。

(もっと読む)

半導体装置とその製造方法

【課題】クラック伝播を抑制できる新規な構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板に形成された半導体素子と、半導体素子を囲む第1金属リングと、半導体素子を覆って形成され、内部に前記第1金属リングが配置された絶縁膜と、絶縁膜に形成された溝とを有し、第1金属リングは、複数の金属層が積層されて形成され、各々の金属層の外側の側面が一致しているか、または、下側に位置する金属層の外側の側面よりも上側に位置する金属層の外側の側面が内側に位置しており、溝の底面は、第1金属リングより内側に配置された第1部分で、第1金属リングの最上層に位置する金属層の上面以下である。

(もっと読む)

メモリアクセス制御装置、及びメモリアクセス制御方法

【課題】データメモリへのリクエストを優先順位に応じて調停する。

【解決手段】メモリアクセス制御装置に、メモリに対する複数の、それぞれ優先順位を有するリクエストを受け付ける受付部と、前記優先順位を有する複数のキャッシュと、第1の優先順位を有する第1のリクエストが受け付けられると、前記第1の優先順位を有する空き状態の第1のキャッシュに当該第1のリクエストを登録し、前記第1のキャッシュが検出されないときには、前記第1の優先順位より低い第2の優先順位を有する空き状態の第2キャッシュに前記第1のリクエストを登録し、当該第2のキャッシュの前記第2の優先順位を前記第1の優先順位に変更する管理部と、前記第1、または第2のキャッシュに登録された前記リクエストを実行する実行部とを設け、データメモリへのリクエストを優先順位に応じて調停する。

(もっと読む)

無線通信装置における位相シフトを推定及び補正するシステム及び方法

【課題】無線通信装置における位相シフトを推定及び補正する方法を提供する。

【解決手段】本発明の幾つかの実施の形態によれば、本方法は、無線通信装置のデジタル回路により出力されたデジタル信号を、計算された位相誤差に基づいて、補償されたデジタル信号に変換するステップを含む。また、本方法は、補償されたデジタル信号を無線通信信号に変換するステップを含む。また、本方法は、デジタル回路により出力されたデジタル信号の推定される瞬間的な基準となる位相を更に計算するステップを含む。さらに、本方法は、無線通信信号の推定される送信位相を計算するステップを更に含む。さらに、本方法は、推定される瞬間的な基準となる位相と、無線通信信号の推定される送信位相との間の差に基づいて位相誤差を計算するステップを含む。

(もっと読む)

151 - 160 / 2,507

[ Back to top ]