台湾積體電路製造股▲ふん▼有限公司により出願された特許

31 - 40 / 198

光デバイス及びその製造方法

【課題】 光デバイスとその製造方法を提供する。

【解決手段】 基板と、前記基板の一部を露出する、少なくとも1のアスペクト比をそれぞれ有する2つ以上の開口を含む誘電材料と、前記基板と格子不整合の化合物半導体材料を含み、前記化合物半導体材料が2つ以上の開口を占有し、前記2つ以上の開口の上に接合され、下ダイオード領域を形成する下ダイオード材料と、上ダイオード材料と、前記上及び下ダイオード材料の間に設けられた活性ダイオード領域を有する光デバイス。

(もっと読む)

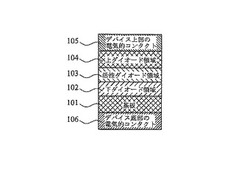

ダイオードベースのデバイスとその製造方法

【課題】 ダイオードベースのデバイスとその製造方法を提供する。

【解決手段】 基板、前記基板の一部を露出する、少なくとも1のアスペクト比を有する開口を含む誘電材料、前記開口内の少なくとも一部に設置された下領域と前記開口上に延伸した上領域を含み、前記基板と格子不整合の半導体材料を含む下ダイオード材料、前記下ダイオード材料の前記上領域に隣接した上ダイオード材料、及び前記上ダイオード材料と下ダイオード材料の間にあり、前記基板の上表面から離れて延伸した表面を含む活性ダイオード領域を含むダイオード。

(もっと読む)

SRAMワードラインカップリングノイズ制限

【課題】 マルチプルポートのランダムアクセスメモリセル用の直流モードワードラインカップリングノイズ制限回路を提供する。

【解決手段】 この回路は、スタティックランダムアクセスメモリセル(SRAM)アレイからなる。SRAMアレイは、複数のカラムと複数のロウからなり、SRAMセルは、カラムとロウの交点で形成される。各SRAMセルは、第一ワードライン導体と第二ワードライン導体を含む。第一ワードライン導体は、第一カップリングノイズ制限回路に接続される。第一カップリングノイズ制限回路は、インバータとNMOS電界効果トランジスタを含み、インバータは、別のNMOS電界効果トランジスタとPMOS電界効果トランジスタを含む。

(もっと読む)

電界効果トランジスタの金属ゲート構造

【課題】電界効果トランジスタの電気抵抗の小さい金属ゲート構造を提供する。

【解決手段】本発明は、集積回路製造に関するものであって、特に、低抵抗の金属ゲート電極を有する電界効果トランジスタに関するものである。電界効果トランジスタのゲート電極の例は、凹部326aを有し、かつ、第一抵抗を有する第一金属材料からなる下側部分326と、突起328aを有し、かつ、第二抵抗を有する第二金属材料からなる上側部分328とからなり、突起が凹部に延伸し、第二抵抗は第一抵抗より小さい材料で形成される。

(もっと読む)

マルチフィン高さを有するFinFET

【課題】マルチフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、半導体基板と、半導体基板上のFinFETと、を含む。FinFETは、半導体フィンと、半導体フィンの頂面および側壁上のゲート誘電体と、ゲート誘電体上のゲート電極と、半導体フィン一端に位置するソース/ドレイン領域と、を備える。一対の第一STI領域は、ソース/ドレイン領域の一部分の真下に位置する部分を含み、一対の第一STI領域は、半導体ストリップにより分離され、且つ、半導体ストリップに隣接する。一対の第一STI領域は、更に、第一頂面を有する。一対の第二STI領域は、ゲート電極の真下に位置する部分を含み、一対の第二STI領域は、半導体ストリップにより互いに分離され、且つ、半導体ストリップに隣接する。第二STI領域は、第一頂面より高い第二頂面を有する。

(もっと読む)

集積回路

【課題】マルチフィンを有するFinFETを利用したSRAM構造を提供する。

【解決手段】SRAMセルは、ストレートフィンと、ストレートフィンから物理的に切り離された屈曲フィンからなる。屈曲フィンは、ストレートフィンに平行な第一部分と第二部分を有する。屈曲フィンの第一部分とストレートフィンの間の距離は、屈曲フィンの第二部分とストレートフィンの間の距離より小さい。SRAMセルは、第一ゲートストリップの一部分を含むプルダウントランジスタからなり、それぞれ、ストレートフィンと屈曲フィンの第一部分を有する第一と第二サブプルダウントランジスタを形成する。SRAMセルは、更に、第二ゲートストリップの一部分を含むパスゲートトランジスタからなり、ストレートフィンを有する第一サブパスゲートトランジスタを形成する。プルダウントランジスタは、パスゲートトランジスタより多いフィンを有する。

(もっと読む)

オーバーレイの方法及びその装置

【課題】フォトリソグラフィ工程で使用するオーバーレイマークを提供する。

【解決手段】半導体デバイスの製造方法は、基板を準備する工程13と、基板の中にオーバーレイマークの第1の部分を形成し、第1の部分は、第1の方向で測定される第1の寸法と、第1の方向に対して略垂直な第2の方向で測定され、第1の寸法より大きな第2の寸法と、をそれぞれ有する複数の第1のフィーチャを有する工程15と、基板の中にオーバーレイマークの第2の部分を形成し、第2の部分は、第1の方向で測定される第3の寸法と、第2の方向で測定され、第3の寸法より小さい第4の寸法と、をそれぞれ有する複数の第2のフィーチャを有する工程17と、を含む。

(もっと読む)

集積回路構造、及び集積回路の製造方法

【課題】異なるフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、第1装置領域の第1部分と、第2装置領域の第2部分と、を有する半導体基板からなる。第1半導体フィンは半導体基板上にあり、第1フィン高さを有する。第2半導体フィンは半導体基板上にあり、第2フィン高さを有する。第1フィン高さは第2フィン高さより高い。

(もっと読む)

半導体装置のパッド構造

【課題】半導体装置のパッド構造を提供する。

【解決手段】半導体装置200は、半導体基板202、相互接続構造、複数のダミーメタルビア235及びパッド構造を備える。半導体基板202は、内部に複数の微小電子素子が設けられている。相互接続構造は、半導体基板202上に設けられ、複数の金属層210a〜210iと、金属層を隔離する複数のIMD層220とを有する。金属層210a〜210iは、最上金属層210iと、最下金属層210aと、最上金属層210iと最下金属層210aとの間に設けられた少なくとも2層の金属層とを含む。複数のダミーメタルビア235は、少なくとも2層の金属層間に設けられた1層又は2層以上のIMD層220内に形成される。パッド構造は、ダミーメタルビア235の上に直接設けられている。

(もっと読む)

不均一な半導体装置のアクティブ領域パターン形成方法

【課題】不均一な半導体装置のアクティブ領域パターン形成方法を提供する。

【解決手段】具体例によると、少なくとも3つのアクティブ領域を含む半導体装置が提供される。少なくとも3つのアクティブ領域は隣接する。少なくとも3つのアクティブ領域の縦軸は平行で、少なくとも3つのアクティブ領域は、それぞれ、対応するアクティブ領域の縦軸と交差する辺縁を有する。少なくとも3つのアクティブ領域の辺縁は弧形を形成する。

(もっと読む)

31 - 40 / 198

[ Back to top ]