Fターム[2F085GG27]の内容

未知の時間間隔を測定するもの (1,604) | 計時手段 (305) | パルス発生手段 (26)

Fターム[2F085GG27]の下位に属するFターム

回転体の発生パルス

異周期パルスの利用(バーニア法) (2)

Fターム[2F085GG27]に分類される特許

1 - 20 / 24

時間測定方法及びそのシステム

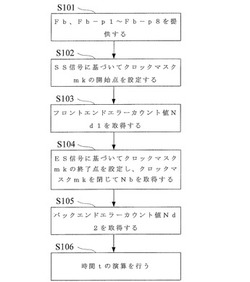

【課題】時間測定過程の演算速度と測定の正確性を高め、回路占用面積を減少し、かつ消費電力を減少した時間測定方法及びそのシステムの提供。

【解決手段】本発明の時間測定方法及びそのシステムは、測定開始と測定終了時に生成される開始信号と終了信号を利用してクロックマスクを設定し、且つこのクロックマスク下の基準信号のサイクル数を取得して初期時間値を換算して得ると同時に、前記基準信号に基づいて生成された複数の位相シフト信号を利用して前述の初期時間値を修正し、かつ位相シフト信号数の増加に伴いエラーをさらに縮小して、正確な時間測定値を取得することができ、且つ測定速度が速く、測定システムが占用する回路面積が小さいという利点がある。

(もっと読む)

時間間隔計測装置及び時間間隔計測方法

【課題】時間間隔の計測精度を向上させる。

【解決手段】開始時点から各クロック信号の直近の立ち上がり時点までの時間間隔及び各クロック信号の直近の立ち上がり時点から終了時点までの時間間隔を計測する細時間測定手段(20)と、第1クロック信号を利用して開始時点から終了時点までの周期をカウントする第1カウンタ(12a)と、第2クロック信号を利用して開始時点から終了時点までの周期をカウントする第2カウンタ(12b)と、第3クロック信号を利用して開始時点から終了時点までの周期をカウントする第3カウンタ(12c)と、細時間および粗時間を選択する選択手段(31)と、選択手段で選択された粗時間と細時間とから開始時点から終了時点までの時間間隔を演算する演算手段(32)とを備える。

(もっと読む)

計時装置及びこれを用いた電子時計

【課題】 環境の変化に強く外部からのメンテナンスも必要としない、長期間動作可能な計時装置を提供すること。

【解決手段】 固定部と自由端部とを有する弾性体のレバー101に電荷を蓄積可能な電荷蓄積部材103と出力端子を有する圧電部材104とが設けられ、電荷蓄積部材103に放射線を放射する放射性物質102を配置して、電荷蓄積部材103に蓄積される電荷で電荷蓄積部材103に発生する静電力で生じる前記レバー101の撓みと、レバー101が撓んだ状態で蓄積電荷の放電で生じるレバー101の撓みの開放とが繰り返されることにより、出力端子から交流電流を出力可能な原子力電池1を用い、出力される交流電流を波形整形して計時パルスを出力する波形整形回路5と、計時パルスから計時動作を行う計時カウンタ7と、交流電流により蓄電されるとともに、波形整形回路5と計時カウンタ7とに電力を供給する蓄電手段3とを設けて計時装置を構成した。

(もっと読む)

時間計測装置およびセンサ装置

【課題】計測時間の計測精度の低下を抑制し得る時間計測装置およびセンサ装置を提供する。

【解決手段】レーザレーダ装置1に採用される制御回路70の時間計測回路71では、計測時間Tが、デジタル値D1およびデジタル値D2の比率と基準時間Toとに基づいて求められる。さらに、比率演算時の時間分解能Tr1が、比率演算時の演算誤差e1に等しくなるように設定されて、リング遅延パルス発生回路81の遅延素子(ゲートディレイ)の時間分解能よりも細かく設定される。

(もっと読む)

計時装置

【課題】複数の時間を測定することが可能な計時装置を提供する。

【解決手段】この時間デジタル変換装置は、スタート信号STAを出力するクロック発生回路3と、スタート信号STAが出力されてからストップ信号ST1〜ST4が入力されるまでそれぞれ時間信号TM1〜TM4を「H」レベルにする時間信号発生回路4と、それぞれ時間信号TM1〜TM4が「H」レベルにされた時間を測定する計時回路5〜8とを備える。したがって、スタート信号STAを出力してからストップ信号ST1〜ST4が入力されるまでの4個の時間を測定できる。

(もっと読む)

時間計測回路

【課題】TAC方式とクロックカウント方式を併用する際に、クロック発生部を別途設ける必要のない時間計測回路を得る。

【解決手段】入力信号の振幅の最大値を検出し、ピーク検出トリガを出力するピーク検出回路(30)と、外部からの測定開始信号を起点として、時間経過に伴って電圧値が所定のパターンで上昇するアナログ信号を生成し出力するアナログ信号発生部(10)と、アナログ信号の電圧値をモニタし、所定電圧値を超えるごとにアナログ信号の電圧値をゼロリセットする動作を繰り返すことで、一定間隔のパルス信号を発生させるパルス発生部(60)と、ピーク検出トリガが出力されたタイミングにおけるアナログ信号の電圧値と、パルス信号の計数結果とに基づいて、測定開始信号を起点としてピーク検出トリガが出力されるまでの時間を算出する時間算出処理部(20、40、50)とを備える。

(もっと読む)

クロノグラフ時計

【課題】クロノ駆動タイミングと磁界検出タイミングが重なって不必要に補正駆動パルスによって駆動されるのを防止すること。

【解決手段】処理部108は、計時した計時情報、計測したクロノ計測情報に各々基づいて所定タイミングで時刻表示モータ110、クロノ表示モータ114を駆動するように駆動回路109、113を制御すると共に所定タイミングで磁界検出手段112が磁界を検出するように制御し、クロノ表示モータ114の駆動タイミングと磁界検出手段112の磁界検出タイミングが重なった場合、クロノ表示モータ114の駆動タイミングと磁界検出手段112の磁界検出タイミングが重ならないように磁界検出手段112の磁界検出タイミングを変更する。

(もっと読む)

クロノグラフ時計

【課題】クロノグラフ機能の使用時間が少ない場合でも、電池信頼性寿命時間の超過を防止して、漏液によるクロノグラフ時計の故障発生を防ぐこと。

【解決手段】24時間カウンタ111は経過した時間を24時間からダウンカウントし、クロノカウンタ112は所定時間からクロノ計測動作を行った時間をダウンカウントし、処理部106は、24時間カウンタ111とクロノカウンタ112のカウント値が等しくなったとき、カウンタ111、112の残り時間の間、電池電力消耗手段103によって電池113を消耗させる。

(もっと読む)

時間計測回路

【課題】TAC方式を使用する時間計測回路、またはTAC方式とパルスカウント方式を組み合わせた時間計測回路において、測定精度を向上させるとともに、デッドタイムのない回路構成を提供する。

【解決手段】入力信号Viの振幅の最大値を検出してトリガTRGを出力するピーク検出回路5と、測定開始信号Vgに応答して動作する3個以上の複数のアナログ信号発生部1〜4と、アナログ信号発生部1〜4の動作タイミングを制御する制御部6と、トリガTRGの出力時点におけるアナログ信号発生部の少なくとも1つの出力電圧を用いて、測定開始信号Vgの出力時刻を起点としたトリガTRGの出力時刻を算定する算定部7とを備えている。

(もっと読む)

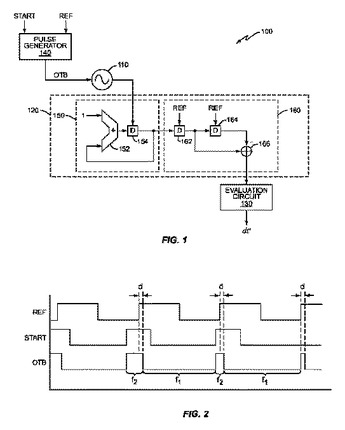

ノイズシェーピング時間測定回路

時間測定回路のある実施形態では、リファレンス信号期間の第1の部分においてデジタル制御発振器(DCO)を第1の周波数で動作させ、前記対象信号と前記リファレンス信号との時間差に応じて前記リファレンス信号期間中に動作周波数を前記第1の周波数から第2の周波数に変更することにより、対象信号とリファレンス信号の時間差が測定される。時間測定回路は、前記リファレンス信号期間において前記デジタル制御発振器の出力で何回の信号遷移が発生したかを継続的に計数する。対象信号とリファレンス信号の時間差は、前記リファレンス信号期間において計数された前記信号遷移の回数に基づいて推定される。

(もっと読む)

(もっと読む)

カウンタ回路

【課題】本発明は、簡単な回路構成で検査時間が短縮できコストアップを抑えることができるカウンタ回路を提供することを目的とする。

【解決手段】、発振器の出力するクロック信号をカウントして計時を行うカウンタ回路において、前記カウンタ回路を構成する複数段のフリップフロップ11−1〜11−nの全部をバイパスするヒューズ13を有する。

(もっと読む)

第1の事象と第2の事象との間の時間差を求める方法

【課題】2つの事象間の時間差の測定を高い時間分解能で測定し、時間測定に起因する電磁障害を低減する。

【解決手段】位置測定装置の測定信号評価ユニット(3)を用いて第1の事象(A)と第2の事象(B)との間の時間差(T)を求める方法であって、単一または複数の周期信号(x1(t),x2(t))から位置値が求められ、第1の事象(A)の発生時に第1の位置値(φA)が測定信号評価ユニット(3)により求められ、第1の事象(B)の発生時に第2の位置値(φB)が測定信号評価ユニット(3)により求められ、第1および第2の位置値(φA,φB)により時間差(T)が求められる。

(もっと読む)

矩形信号の期間幅を予測する回路

【課題】矩形信号のレベルが同一である期間の長さを予測することのできる技術を提供する。

【解決手段】

矩形信号のレベルが同一である期間の長さである期間幅を予測する期間幅予測回路598は、矩形信号のレベルが変化する時間的位置を変化位置として検出する変化位置検出部706と、変化位置から次の変化位置までの長さを期間幅として計測する期間幅計測部594と、期間幅計測部によって計測された複数の期間幅を過去期間幅として記憶する過去期間幅記憶部702,704と、過去期間幅の変化に基づいて、次の期間幅の予測値である予測期間幅RAを算出する予測期間幅算出部710と、を備える。

(もっと読む)

時間測定回路

【課題】三角波の頂点付近での影響が無く、正確に時間の測定を行うことが可能な時間測定回路を提供する。

【解決手段】一定の周期でクロック信号を発生させるクロック発生手段と、前記クロック発生手段により発生したクロック信号に基づいて、それぞれ互いに所定の位相差を有する第1及び第2のクロック信号を出力する位相クロック出力手段と、前記位相クロック出力手段により出力された第1のクロック信号に従って三角波を発生させる第1の三角波発生手段と、前記位相クロック出力手段により出力された第2のクロック信号に従って三角波を発生させる第2の三角波発生手段と、時間を測定するために用いる被測定パルスを出力するパルス出力手段と、前記パルス出力手段により出力された被測定パルスに応じて、前記第1および第2の三角波発生手段により発生した三角波の振幅をサンプルする振幅サンプル手段と、前記振幅サンプル手段によりサンプルされた三角波の振幅のうちのいずれか1つに基づいて時間を測定する時間測定手段とを備えたことを特徴とするもの。

(もっと読む)

タイマ装置

【課題】時間分解能を高めたタイマにより低消費電力で精度よく時間計測するタイマ装置を提供する。

【解決手段】入力信号を反転して出力する反転手段10と、反転手段10からの入力信号を所定時間遅延させて出力する遅延手段11と、遅延手段11に接続され所定の制御信号により出力を所定の状態に保持する保持手段19とを備え、計測開始信号と計測停止信号が入力されたとき、その指示信号を前記保持手段19の制御端子に所定の形態で入力する保持選択手段22及びラッチ手段21を有し、反転手段10と遅延手段11と保持手段19とで1組の信号生成手段を構成すると共に、この信号生成手段を複数段設けリング状に接続してHi/Loのクロック信号を生成するリングオシレータを構成し、最終段の信号生成手段の出力をカウントして時間計測を行う構成としたものである。

(もっと読む)

時間測定回路およびそれを用いたIC検査装置

【課題】 電圧信号と基準電圧を比較回路で比較し、この比較回路の出力を短周期でメモリに保存して、この保存した値が変化する位置を検出して立ち上がり時間を測定していた。そのため、大きな容量のメモリが必要になり、かつ時間分解能を高くすることが困難であったという課題を解決する。

【解決手段】 電圧信号と基準電圧を比較回路で比較し、この比較回路の出力が反転したタイミングで、クロックをカウントするカウンタのカウント値をメモリに保存するようにした。必要なメモリ容量が少なくて済み、かつ時間分解能を高くすることができる。

(もっと読む)

遅延時間評価方法及び回路、及び半導体装置

【課題】本発明は、遅延時間評価回路及び半導体装置に関し、遅延測定対象回路と遅延時間評価回路の独立性、即ち、非干渉性を向上することを目的とする。

【解決手段】複数段のゲート回路から構成されており接続段数が切り替え可能である被測定回路内の信号の伝播遅延時間を評価する遅延時間評価回路において、入力信号と、この入力信号を接続段数が任意の段数に切り替えられた被測定回路を通した信号の位相差を検出する位相差検出回路と、位相差に応じたパルス列を生成して外部へ出力する変換回路部と、被測定回路と位相差検出回路との間を容量結合又は非接触結合により結合する結合部とを備えるように構成する。

(もっと読む)

時間計測回路

【課題】短い時間幅の高分解能な計測と長い時間幅の低分解能な計測とを、回路規模を大幅に増大させることなく、いずれも実現させることが可能な時間計測回路を提供する。

【解決手段】駆動電圧VDDLに応じた遅延時間で信号を遅延させる遅延ユニットDUをM(Mは正整数)段直列接続してなり、起動用パルスPAの入力により起動され、各遅延ユニットDUにてパルス信号を順次遅延させながら伝送するパルス遅延回路10と、計測用パルスPBが入力されると、パルス遅延回路10内でのパルス信号の位置を検出(ラッチ)し、その検出結果を、起動用パルスPAの入力から計測用パルスPBの入力までの時間Tm内にパルス信号が通過した遅延ユニットDUの段数を表す所定ビットのデジタルデータDTに変換して出力するラッチ&エンコーダ12と、電圧設定データDVに従った大きさの駆動電圧VDDLを発生させる駆動電圧設定回路14とを備える。

(もっと読む)

遅延時間評価方法及び回路、及び半導体装置

【課題】本発明は、遅延時間評価回路及び半導体装置に関し、回路面積を増大させることなく、少数段で構成されるゲート回路等の遅延時間を短時間で精度よく評価することを目的とする。

【解決手段】複数段のゲート回路から構成されており接続段数が切り替え可能である被測定回路内の信号の伝播遅延時間を評価する遅延時間評価回路において、入力信号と、この入力信号を接続段数が任意の段数に切り替えられた被測定回路を通した信号の位相差を検出する位相差検出回路と、位相差に応じたパルス列を生成して外部へ出力する変換回路部とを備え、パルス列のパルス数は被測定回路内での入力信号の遅延時間に相当するように構成する。

(もっと読む)

タイムインターバル測定装置、タイムインターバル測定方法

【課題】タイムインターバル測定装置の構成の簡易化及び高精度な測定の実現

【解決手段】

時間差を求める対象となる第1,第2の信号について、第1の信号の変化点からの時間経過に相当する電圧値を第2の信号のタイミングでサンプリングしてデジタル値に変換すし、そのデジタル値から時間差を算出する。また、基準クロック信号CKrと校正用信号を用いて時間−電圧変換回路5の電圧出力の変動に対する構成情報を生成し、校正情報を用いて時間差を精度良く算出できるようにする。

(もっと読む)

1 - 20 / 24

[ Back to top ]