Fターム[2G132AD06]の内容

Fターム[2G132AD06]に分類される特許

1 - 20 / 617

出力制御スキャンフリップフロップ、それを備えた半導体集積回路及び半導体集積回路の設計方法

半導体装置及びそのテスト方法

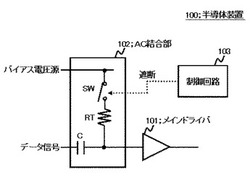

【課題】データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置のDCテストの実施には、振幅を維持できないという問題がある。そのため、データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置であって、DCテストを可能にする半導体装置が、望まれる。

【解決手段】半導体装置は、データ信号を外部に出力するメインドライバと、データ信号が伝達する配線と接続されているコンデンサと、一端がコンデンサと接続され、他の一端がバイアス電圧源に接続されている終端抵抗と、バイアス電圧源と終端抵抗との間に接続されている第1のスイッチと、を含むAC結合部と、テストモード時にAC結合部のバイアス電圧源と終端抵抗との接続を、第1のスイッチにより遮断する制御回路と、を備える。

(もっと読む)

半導体装置およびその検査方法

【課題】ウエハ検査時に必要なプローブピンを削減可能にした半導体装置を提供する。

【解決手段】第1のデータを記憶する記憶素子と、データ読み出しの指示が入力されると、記憶素子から第1のデータを読み出して出力するデータ入出力制御部と、データ入出力制御部から出力される第1のデータを第1の端子に出力し、第1のデータを第1の端子に出力するとき、自装置の第2の端子と他の半導体装置の第1の端子とを接続するプローブカードを介して他の半導体装置から受信する第2のデータを保持し、その後、第2のデータを自装置の第1の端子に出力するデータラッチ部とを有する。

(もっと読む)

自己診断機能付き装置

【課題】自己診断する論理の範囲を比較回路以外の検査論理、更にはメイン論理に広げ、検査論理、メイン論理に異常がある場合、比較回路が不一致を発生する前に検出し装置の交換ができるようにする。

【解決手段】同じ入力が与えられ、同じ論理演算を実施する第1と第2の論理部、第1と第2の論理部のいずれかにエラー信号を与えるエラー注入回路、第1と第2の論理部の出力を入力し選択した信号を与える選択回路と第1と第2の論理部の出力を比較し、比較不一致信号を与える比較回路とを備えた比較補正回路から構成され、比較補正回路は、第1と第2の論理部のいずれかにエラー信号を与えた時、第1と第2の論理部の出力が不一致にならない場合、または、第1と第2の論理部にエラー信号を与えないときに、第1と第2の論理部の出力が不一致になる場合に異常があると判断する。

(もっと読む)

半導体メモリ装置および半導体システム

【課題】PVT変動によってスキューが発生しても、不良に関する情報を適切に格納できるようにした半導体メモリ装置を提供する。

【解決手段】書き込み動作のために書き込みコマンドおよびデータを印加し、読み出し動作のために読み出しコマンドを印加し、前記読み出し動作によって出力データが入力されるテスト回路と、前記書き込みコマンドに応答して前記データをメモリセルに格納し、前記読み出しコマンドに応答して不良に関する情報を含む情報データを内部的に格納するが、前記情報データの格納は、前記情報データのレベルが遷移する場合に発生するパルスに同期して行われる。

(もっと読む)

半導体メモリ装置及びそのためのテスト回路

【課題】本発明は、テスト速度を向上させることができる半導体メモリ装置及びそのためのテスト回路に関するものである。

【解決手段】本発明に係る半導体メモリ装置は、複数のメモリセルを含むメモリセルアレイ;データ入出力パッドに接続され、テストモード信号に応じて前記データ入出力パッドに印加されたデータの伝達経路を制御するスイッチング部;ノーマルモード時、前記スイッチング部から伝達されるデータを駆動して、前記メモリセルアレイに書き込むライトドライバ;及び、テストモード時、前記スイッチング部から伝達されるデータを前記メモリセルに伝達するコントローラを含む。

(もっと読む)

スキャン・チェーン用動的クロック領域バイパス

【課題】スキャン・テスト回路およびスキャン・テスト回路を使用して試験を受けるさらなる回路を備える集積回路を提供すること。

【解決手段】スキャン・テスト回路は、それぞれ別個のクロック領域に関連した複数のサブチェーンを有する少なくとも1つのスキャン・チェーン、および1つまたは複数のサブチェーンを選択的にバイパスするように構成されたクロック領域バイパス回路を備える。スキャン・チェーンは、スキャン・シフト・モードの動作において、サブチェーンを全部よりは少なく含む直列シフト・レジスタを形成するように構成可能であり、サブチェーンの少なくとも残りの1つが、スキャン・シフト・モードにおいて直列シフト・レジスタの部分でないように、クロック領域バイパス回路によりバイパスされる。特定のクロック領域に関連するスキャン・チェーンの部分を選択的にバイパスすることにより、クロック領域バイパス回路は、スキャン・テスト期間の試験時間と電力消費を減らす役割を果たす。

(もっと読む)

論理回路の故障検出方法、テスト回路挿入方法、テスト回路挿入装置および半導体集積回路

【課題】 論理ゲートの一方の入力を含む信号パスの遅延故障と、論理ゲートの他方の入力を含む信号パスの遅延故障とを、1つの制御点により検出する。

【解決手段】 第1および第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、第1論理ゲートの出力に接続された第3ユーザロジックと、第2ユーザロジックと第1論理ゲートとの間に挿入された制御点とを有する。制御点は、第1または第3ユーザロジックの第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する。

(もっと読む)

再構築したメモリ空間の回収方法

【課題】廃棄されたダイから使用可能なメモリ空間を回収するメモリ容量を有するメモリを回収する方法を提供する。

【解決手段】再構築したメモリ空間の回収方法は、廃棄されたダイを回収し、使用可能なメモリ空間に応用し、規格化又は非規格化のメモリ容量を有するメモリを形成する。再構築したメモリ空間の回収方法は、ブロックエリア、ページエリア及びセルエリアを有するダイを準備するステップと、ダイのブロックエリア、ページエリア及びセルエリアのうちの1つを走査し、ダイに対応したエリア中にテストデータを書き入れ、ダイによりテストデータの読み書き及び比較を行ってテスト結果を得て、このテスト結果に基づき、正常及び異常なブロックエリア、ページエリア又はセルエリアを標記するステップとを含む。

(もっと読む)

スキャンチェーン検査装置及び検査方法

【課題】 スキャンチェーンの検査を好適に行うことが可能なスキャンチェーン検査装置及び検査方法を提供する。

【解決手段】 半導体装置10のスキャンチェーンに検査信号を供給する検査信号供給部18と、スキャンチェーンの各レジスタでの検査信号の信号レベルの時間変化を測定するレジスタ測定部20と、測定部20による測定結果に基づいて各レジスタにレジスタ番号を付与するレジスタ番号解析部51を有する検査解析装置50とによってスキャンチェーン検査装置1Aを構成する。供給部18は、信号長nが異なるm種類の検査信号列を供給する。解析部51は、信号長nの検査信号列を用いた測定結果からスキャンチェーンの複数のレジスタをn個のグループに分けるグループ分けをm種類の検査信号列のそれぞれについて行い、その結果に基づいて各レジスタにレジスタ番号を付与する。

(もっと読む)

半導体集積回路の検査方法および半導体集積回路

【課題】半導体集積回路のクロックに一定周波数のクロックのみを供給しつつ半導体集積回路の内部クロックを動的に変化させて半導体集積回路のランダム・ロジックを検査する。

【解決手段】複数の組み合わせ回路と当該複数の組み合わせ回路のスキャンテストを行うためのスキャンチェーンを構成する複数のスキャンフリップフロップとを有する半導体集積回路、の検査方法を、クロック生成装置から前記半導体集積回路に一定周波数の第1クロックを入力する入力工程と、前記半導体集積回路の内蔵する分周器が前記第1クロックを分周して第2クロックを生成する分周工程と、前記複数のスキャンフリップフロップに入力するクロックを、前記第1クロックと前記第2クロックとの間で動的に切り替えつつ前記半導体集積回路を検査する検査工程と、により構成する。

(もっと読む)

擬似障害発生方法と装置

【課題】電子回路装置に対する擬似障害発生を容易化し、試験・評価等の作業を効率化する装置、方法の提供。

【解決手段】

電子回路装置(100)を構成する回路基板(105)上のIC(104)のON/OFF端子に接続部103を介して接続する制御部102が、ケーブルコネクタ部(101)を介してPC(110)の制御により、IC(104)のON/OFF端子に動作中の第1の値とは異なる第2の値を設定することで擬似障害を発生させる。

(もっと読む)

半導体集積回路及び半導体集積回路の設計方法

【課題】半導体集積回路の回路面積を小さくする。

【解決手段】被試験回路2の観測対象の複数の信号線TA1〜TA4上の観測点TP1〜TP4を複数の入力端子に接続し、複数の信号線TA1〜TA4を伝搬する値の、論理積、論理和、否定論理積、または否定論理和の何れかを演算し、複数の信号線TA1〜TA4の何れかを伝搬する値に応じた出力値を出力する論理回路(NOR回路3,NAND回路4)を設けることで、複数の観測点をEOR回路を用いて共用する半導体集積回路より回路面積を小さくできる。

(もっと読む)

評価システム

【課題】製品ボードに搭載される製品FPGAの端子数に制限されず、内部信号の観測を可能とし、製品FPGAを製品ボードに搭載された実使用状態で論理検証することが可能な評価システムを提供することを課題とする。

【解決手段】評価システム1は、製品ボード2、評価ボード3、およびそれらを接続するシリアル・インターフェース5を備える。製品ボード2に搭載される製品FPGA6はコアロジック60に入力される外部入力信号を分岐する分岐回路61を備える。評価ボード3は観測FPGA8を備える。観測FPGA8はコアロジック60と論理的に等価な観測コアロジック81および観測コアロジック81の内部信号を取得する内部信号取得回路82を備える。コアロジック60の実動作に供される外部入力信号が評価ボード3に送られ観測コアロジック81がコアロジック60の実動作と等価に動作する。その時の内部信号を取り出し論理検証を行う。

(もっと読む)

半導体試験装置および半導体試験装置のタイミング調整方法

【課題】複数の被試験デバイスに対して電源供給部から電源の供給を行って試験を行うときに、同時スイッチングノイズの影響を抑制することを目的とする。

【解決手段】本発明の半導体試験装置1は、複数のDUT3に電源を供給するデバイスパワーサプライ5を備える半導体試験装置1であって、DUT3の試験を行うピンエレクトロニクスカード2のドライバ12およびコンパレータ13とDUT3との間の伝送経路15の伝播遅延Tpdを校正するデータをタイミング校正データとして記憶するタイミング校正データ記憶部21と、DUT3を複数のグループに分割して、当該グループごとに異なる遅延量をタイミング校正データに加算する遅延量加算部25と、を備えたことを特徴としている。

(もっと読む)

フリップフロップ回路

【課題】セレクタ付フリップフロップ回路の入力信号がラッチ回路へと伝播するまでに、選択信号により制御されるスイッチ回路とクロック信号により制御されるスイッチ回路とを介するため、入力信号がラッチへと伝播するまでの時間が長い。

【解決手段】セレクタ付フリップフロップ回路100は、選択信号SA、クロック信号CKおよび複数の入力データが入力され、複数の入力データのうち1つを出力するフリップフロップ回路であって、選択信号SAおよびクロック信号CKに基づいて、第1の制御信号CAを生成する第1の論理回路102と、第1の制御信号CAにより制御される第1のスイッチ回路101と、第1のスイッチ回路101を介して、複数の入力データから選択された一の入力データを保持する第1のラッチ回路103とを有する。

(もっと読む)

ROMテスト時間の短縮方法

【課題】 従来の技術においては、ROM3個分のテスト時間を2個分のテスト時間までしか短縮できないという問題、或いは、加算或いは減算をおこなうため、データビット数の変動の虞があると共に、信頼性が低下する虞があった。

【解決手段】 複数個のROMに書き込まれたデータをテストする場合のROMテスト時間の短縮方法に於いて、複数個のROMの二つずつのROMの出力データのビット毎の比較を行う比較手段を備え、該比較手段の出力を複数個のROMに対応してそれぞれ記憶させ、該複数の記憶手段の出力データに対して、演算の順序が異なる少なくとも二つの異なる内容の演算を行い、該演算結果を期待値と比較することでROMデータを検査する。

(もっと読む)

不揮発性半導体記憶装置及びその試験方法

【課題】電源投入により自走的にメモリセルアレイの動作テストを実行する。

【解決手段】一つの実施形態によれば、不揮発性半導体記憶装置は、不揮発性半導体記憶装置は、ロムヒューズブロックを有するメモリセルアレイ、自走テスト部を有するコントローラ、及びコマンドレジスタを有する。不揮発性半導体記憶装置は、電源投入によりメモリセルアレイの自走テストを実行する。

(もっと読む)

半導体集積回路、半導体集積回路の設計支援方法、及び設計支援プログラム

【課題】クロックゲーティング回路を搭載した半導体集積回路の回路規模の増大を抑制しながら、テスト時の消費電力を低減する。

【解決手段】本発明による半導体集積回路は、第1フリップフロップ回路5、第2フリップフロップ回路7、制御回路3、及びクロックゲーティング回路2を具備する。第1フリップフロップ5は、スキャンシフトによって第1データを格納する。第2フリップフロップ7は、スキャンシフトによって第2データを格納する。第3制御回路3は、第1データとスキャンイネーブル信号SMCとの論理演算結果と、第2データと組合せ回路9からの第1イネーブル信号EN1との論理演算結果との論理演算結果をゲート制御信号C1として出力する。クロックゲーティング回路2は、ゲート制御信号C1に応じて次段のフリップフロップ回路1へのクロック信号CLKの伝播を制御する。

(もっと読む)

集積回路及び不揮発性記憶装置書き換え方法

【課題】不揮発性記憶装置内の制御プログラムの書き換え時間を短縮すること。

【解決手段】バウンダリスキャン回路は、不揮発性記憶装置に接続された第1バウンダリスキャンレジスタ装置、及び、不揮発性記憶装置に接続されない第2バウンダリスキャンレジスタ装置を含む回路であって、第1バウンダリスキャンレジスタ装置及び第2バウンダリスキャンレジスタ装置の双方を経由する第1経路と、第1バウンダリスキャンレジスタ装置を経由し第2バウンダリスキャンレジスタ装置を経由しない第2経路とが切り替え可能に接続される。制御信号回路は、TAPコントローラからバウンダリスキャンレジスタ装置に入力される制御信号の入力経路が、第1経路又は第2経路の切り替えに応じて切り替え可能に接続される。

(もっと読む)

1 - 20 / 617

[ Back to top ]