Fターム[2G132AE22]の内容

電子回路の試験 (32,879) | 試験装置(テストヘッドを除く) (4,743) | 制御回路 (1,346)

Fターム[2G132AE22]の下位に属するFターム

プログラムによる制御 (494)

複数試験装置の一括制御(ホストシステム) (60)

Fターム[2G132AE22]に分類される特許

161 - 180 / 792

信号発生装置および試験装置

【課題】簡易な構成で精度良く信号を出力する。

【解決手段】DA変換器と、DA変換器と当該信号発生装置の出力端との間に設けられたサンプルホールド部と、DA変換器の出力電圧を伝搬して入力データに応じた信号を出力するアナログ回路から出力される電圧とDA変換器の出力電圧とを比較する比較部と、ホールド期間において、入力データに代えて比較データをDA変換器に与えて比較データに応じた比較電圧を出力させ、比較部にアナログ回路から出力される信号の電圧と比較電圧とを比較させ、比較部の比較結果に基づいて、入力データに応じてDA変換器から出力される出力電圧を調整する制御部と、を備える信号発生装置を提供する。

(もっと読む)

信号発生装置および試験装置

【課題】精度良く信号を出力する。

【解決手段】DA変換器と、DA変換器から出力される電圧をサンプルしてホールドするサンプルホールド部と、出力信号を伝搬して入力データに応じた信号を出力するアナログ回路から出力される信号の電圧とDA変換器の出力電圧とを比較する比較部と、DA変換器に設定データを与えて設定データに応じた設定電圧を出力させて、サンプルホールド部に設定電圧をサンプルさせ、サンプルホールド部によりホールドされた設定電圧をアナログ回路に与え、設定電圧が与えられてから安定化するまでのアナログ回路から出力される信号の電圧のセットリング波形を測定する測定部と、を備える信号発生装置を提供する。

(もっと読む)

プリント回路基板上の接続をテストする方法および装置

【課題】バウンダリスキャンテストをテスト装置によって自動的に実行する。

【解決手段】PCB31に搭載されたバウンダリスキャン対応デバイス32、33、34、35のバウンダリスキャン対応回路端子を含むリストからデバイス32の第1回路端子37に接続されたバウンダリスキャンセルが、テスト装置42の処理ユニットによってドライバとして作動される。デバイス33の第2回路端子38に接続されたバウンダリスキャンセルが、テスト装置42の処理ユニットによってセンサとして作動される。バウンダリスキャンレジスタから読み出された捕捉データが、ドライバとセンサの間の接続を調べるためにテスト装置42の処理ユニットによって分析される。

(もっと読む)

回路基板検査装置および回路基板検査方法

【課題】小型の集積回路や底面に端子が形成された集積回路が実装された検査対象基板、および内層実装型の検査対象基板を短時間で確実に検査する。

【解決手段】集積回路X1,X2・・が実装された検査対象基板Pの良否を電気的に検査する回路基板検査装置であって、検査対象の集積回路Xに電磁波を選択的に照射した状態において、集積回路Xにおける電源端子Tvが接続されているべき電源パターンPvと信号端子Tsが接続されているべき信号パターンPsとの間の電気的パラメータ、および信号パターンPsと集積回路Xにおけるグランド端子Tgが接続されているべきグランドパターンPgとの間の電気的パラメータを測定し、測定した電気的パラメータに基づいて各導体パターンPv,Ps,Pgに対する各端子Tv,Ts,Tgの接続状態の良否を検査する。

(もっと読む)

半導体試験装置

【課題】複数のDUTを同時測定している場合、同時測定している複数のDUTのうち、誤って意図しないDUTに対しての制御および測定を行っていないかを容易に検証することが可能な半導体試験装置を実現する。

【解決手段】複数の被試験対象デバイスを同時に測定する半導体試験装置において、測定結果が予め分かっている複数の検査済みデバイスを用いて、測定対象となる複数の検査済みデバイスをずらして測定を行うシステム制御部と、同一の検査済みデバイスの測定結果が同じであるか否かを検証し検証結果を出力する実行結果検証手段とを備える。

(もっと読む)

試験装置および試験モジュール

【課題】制御装置を効率良く動作させる。

【解決手段】被試験デバイスを試験する試験装置であって、被試験デバイスを試験する試験ユニットと、試験ユニットに対して処理の実行を要求する制御装置と、を備え、試験ユニットは、制御装置から要求された処理を完了するまでの予測時間を示す状態情報を制御装置に送信し、制御装置は、試験ユニットから受信した状態情報に示された予測時間に基づいて、処理の完了を試験ユニットに確認するタイミングを決定する試験装置を提供する。

(もっと読む)

回路テスト装置、回路テスト方法

【課題】レンジの変更をハードウェアで制御することで、ソフトウェアによるレンジの変更よりも高速にテストを行うことができる回路テスト装置を提供する。

【解決手段】テストすべき電圧値を取得し、取得した電圧値に応じたレンジの値を決定するレンジ決定部22と、テスト対象の回路に印加する電圧のレンジの値を、現在設定されているレンジの値から、レンジ決定部22によって決定されたレンジの値となるように自己の回路構成を変更するレンジ設定部23とを有する回路テスト装置を提供する。

(もっと読む)

半導体試験装置

【課題】半導体試験装置におけるドライバのタイミング調整をより高精度に行うことを目的とする。

【解決手段】DUTに試験信号Sを印加するために設けた1または複数のドライバ31とドライバ31から出力される試験信号Sを入力してドライバ31のタイミング調整を行う調整用コンパレータ32とタイミング調整のための基準信号SSを発生する基準信号発生部16とを有するテストユニット1を備えた半導体試験装置であって、被試験デバイスが接続される接続ピン21に着脱可能に接続され、ドライバ31から出力される試験信号Sの伝播時間と基準信号発生部16から出力される基準信号SSの伝播時間との差分を計測する伝播時間計測ユニット2と、テストユニット1に備えられ、前記差分に基づいてドライバ31の出力タイミングの補正を行うタイミング補正部23と、を備えている。

(もっと読む)

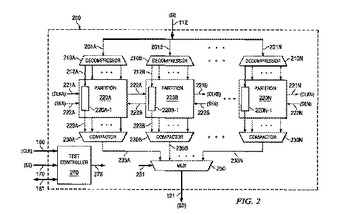

パーティションを設けたスキャン・チェーンを備えた集積回路のスキャンテストにおける向上した制御

パーティションを設けたスキャン・チェーンを備えた集積回路(IC)に実装されたテスト・コントローラが、スキャンテストを実行する際に向上した制御を提供する。一つの側面に従って、テスト・コントローラは、独立しているべき、ICの異なるスキャン・チェーンに対するスキャンテストのスキャンイン、スキャンアウト、及びキャプチャ位相を選択的に制御できる。外部テスターとインタフェースするためにテスト・コントローラに必要なピンの数は、そのテスト・コントローラがサポートし得るパーティションの数より少ない。別の側面に従って、ICは、遷移故障(又はLOS)テストをサポートするため各パーティションに対応するレジスタを含む。別の側面に従って、パーティションを設けたスキャン・チェーンを備えたICが、シリアル−パラレル及びパラレル−シリアル変換器を含み、それにより、スキャンテストをサポートするために必要とされる外部ピンを最小限にする。  (もっと読む)

(もっと読む)

プローブカードアセンブリ用プローブヘッド制御機構

【課題】プローブカードアセンブリを提供すること。

【解決手段】プローブカードアセンブリは、接触要素を有する第1のプローブヘッドであって、接触要素は対応する電子デバイスの対応する端子との電気的接触を形成するためのそれぞれの表面に配置される、第1のプローブヘッドと、接触要素を有する第2のプローブヘッドであって、接触要素は対応する電子デバイスの対応する端子との電気的接触を形成するためのそれぞれの表面に配置される、第2のプローブヘッドと、第1および第2のプローブヘッドに連結された制御機構であって、それぞれの表面に実質的に垂直の第2の方向よりも、それぞれの表面に実質的に平行な第1の方向に第1および第2のプローブヘッドの移動を制御する、制御機構とを備えている。

(もっと読む)

プログラム可能なプロトコル生成器

半導体デバイス試験装置は、被試験半導体デバイスを試験するように構成されるプログラム可能なハードウェアを含む。このプログラム可能なハードウェアは、被試験半導体デバイスへ、及びこれからのデータの流れを制御するための2つ又はそれ以上のパターン生成器でプログラムされる。  (もっと読む)

(もっと読む)

半導体試験装置

【課題】複数の特性が異なる電源部を用いて試験を行った場合でも、印加する電圧の順番を正確に遵守させることを目的とする。

【解決手段】DUT1に電圧を印加するための電源部10は、DUT1に印加する印加電圧を発生する電圧発生部と、電圧発生部が発生した印加電圧を入力して、電圧の印加時には次に動作させる電源部10の印加動作が完了する前に自身の印加動作が完了する電圧として設定した印加設定電圧および電圧の印加停止時には次に動作させる電源部10の停止動作が完了する前に自身の停止動作が完了する電圧として設定した停止設定電圧になっているか否かを監視する電圧監視部19と、電圧監視部19が監視する電圧に基づいて、次に動作させる電源部10に対して動作を許可するトリガ信号を出力するトリガ信号出力部20と、を備えている。

(もっと読む)

処理システムおよび試験装置

【課題】複数の制御部により並列に発生される命令データを動作部が処理する処理システムにおいて、通信量を低減する。

【解決手段】並列に発生される命令データを処理する処理システムであって、それぞれが命令データを発生する複数の制御部と、与えられる命令データに応じて動作する動作部と、動作部に伝送されるべき命令データにおいて、いずれの制御部が発生したデータであるかを示すヘッダ情報を格納するヘッダ情報格納部と、複数の制御部が発生したそれぞれの命令データから、ヘッダ情報格納部が格納したヘッダ情報を除外して動作部に伝送し、動作部から受け取る動作結果データに、ヘッダ情報格納部が格納したヘッダ情報を追加して、制御部に伝送するインターフェース部とを備える処理システムを提供する。

(もっと読む)

処理システムおよび試験装置

【課題】複数の動作部が並列に命令データを処理する処理システムにおいて、各動作部が異常状態となった場合に、他の動作部への影響を排除する。

【解決手段】複数の動作部に対する命令データを受信して格納する共通バッファと、共通バッファが格納した命令データを順次読み出して、対応する動作部に順次振り分けて伝送し、且つ、いずれかの動作部へ命令データを伝送できず、共通バッファから当該命令データを削除できない場合に、当該動作部に代わって当該命令データに応じた処理を行い、共通バッファから当該命令データを削除する振分部とを備える処理システムを提供する。

(もっと読む)

試験装置および試験方法

【課題】複数の試験回路を同期して動作させる試験装置。

【解決手段】被試験デバイスを試験する試験装置であって、複数の試験部と、少なくとも1つの試験部をそれぞれ含む複数のドメインのそれぞれについて、それぞれのドメインに含まれる少なくとも1つの試験部を同期させる第1の同期部および第2の同期部と、を備え、第1および第2の同期部のそれぞれは、当該同期部に接続された試験部からの同期要求をドメイン毎に集約するローカル集約部と、第1の同期部に接続された試験部および第2の同期部に接続された試験部を含む分散ドメインについて、当該同期部内で集約した同期要求を他方の同期部内で集約した同期要求と交換する交換部と、他方の同期部内で集約した同期要求と当該同期部内で集約した同期要求とを集約するグローバル集約部と、当該同期部に接続された試験部のそれぞれに対して、集約した同期要求を分配する分配部と、を有する試験装置を提供する。

(もっと読む)

試験装置、同期モジュールおよび同期方法

【課題】複数の試験モジュールの試験を同期させる。

【解決手段】被試験デバイスを試験する試験装置であって、被試験デバイスを試験する複数の試験モジュールと、複数の試験モジュールのそれぞれに接続されて、複数の試験モジュールを同期させる同期モジュールと、複数の試験モジュールおよび同期モジュールに接続されて、複数の試験モジュールおよび同期モジュールを制御する試験制御部と、を備え、同期モジュールは、複数の試験モジュールのそれぞれから、当該試験モジュールの状態を示す状態信号を受信する受信部と、受信部が受信した各状態信号を集約して集約状態信号を生成する集約部と、集約状態信号に応じた動作を指示する制御信号を複数の試験モジュールに対して送信する送信部と、を有する試験装置を提供する。

(もっと読む)

試験装置および試験方法

【課題】アナログ回路を含む複数の試験回路を同期して動作させる試験装置。

【解決手段】被試験デバイスを試験する試験装置であって、被試験デバイスを試験する複数の試験モジュールと、複数の試験モジュールのそれぞれに接続されて、複数の試験モジュールを同期させる同期モジュールと、を備え、同期モジュールは、被試験デバイスとの間でデジタル信号を授受するデジタルモジュールから受け取った同期信号に基づいて、被試験デバイスのアナログ試験を行うアナログモジュールを前記デジタルモジュールに同期させる試験装置を提供する。

(もっと読む)

除電装置の監視装置、除電装置の監視方法及び除電装置の監視用プログラム

【課題】半導体ウエハWの電気的特性検査を行う際に、被処理体に帯電した静電気を除去する除電装置を監視して信頼性の高い電気的特性検査を行うことができる除電装置の監視装置を提供する。

【解決手段】本発明の除電装置の監視装置(監視回路)22は、メインチャック14とプローブカードが相対的に移動し、メインチャック14上の半導体ウエハWとプローブカード15を接触させて半導体ウエハWの電気的特性検査を行う際に、放電スイッチ回路21を用いてメインチャック14から半導体ウエハWに帯電した静電気を除去する除電装置20を監視する装置であって、除電装置20の放電スイッチ回路21Aと連動し且つ放電スイッチ回路21Aの誤動作を検出する検出スイッチ回路22Aと、検出スイッチ回路22Aを開閉する検出駆動回路22Bと、検出スイッチ回路22Aを介して放電スイッチ回路21Aの誤動作を判定する判定回路22Cと、を備えている。

(もっと読む)

半導体試験方法及び半導体試験装置

【課題】半導体試験の全体の試験時間を短縮する。

【解決手段】半導体試験装置10は、複数の半導体記憶装置のアドレスが所定の順番に配列された第1試験用アドレスを受け付ける受付部と、各半導体記憶装置について第1試験用アドレスに基づく第1試験の試験時間を監視する監視部103aと、監視部103aによって監視された試験時間に基づいて、各半導体記憶装置のアドレスを並び替えることによって、受付部によって受け付けられた第1試験用アドレスを第2試験用アドレスに変換する変換部103bと、変換部103bによって変換された第2試験用アドレスを記憶する記憶部103cと、記憶部103cに記憶された第2試験用アドレスに基づいて、各半導体記憶装置について第2試験を行う試験部102を備える。

(もっと読む)

半導体検査装置、半導体ウエハの検査方法、及び半導体ウエハの検査プログラム

【課題】プローバステージが傾いてしまうことの防止できる、半導体検査装置、半導体ウエハの検査方法、及び半導体ウエハの検査プログラムを提供する。

【解決手段】主面の測定領域に多ピンプローブカードのピン群が当てられる半導体ウエハ、を固定するウエハ固定ステージと、前記半導体ウエハの裏面と当接する当接面を有し、前記当接面により前記半導体ウエハを支持するウエハ測定ステージとを具備する。前記ウエハ測定ステージは、前記当接面の全面が、前記測定領域に対応する領域と当接するように、前記半導体ウエハを支持する。

(もっと読む)

161 - 180 / 792

[ Back to top ]