Fターム[2H092KA03]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子、光導電体層の材料 (8,799) | 素子材料 (4,927) | 結晶状態 (3,186) | 単結晶 (295)

Fターム[2H092KA03]に分類される特許

21 - 40 / 295

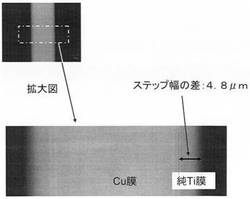

Ti合金バリアメタルを用いた配線膜および電極、並びにTi合金スパッタリングターゲット

【課題】ウエットエッチングによる加工性に優れた特性を有する新規な配線用膜を提供する。

【解決手段】表示装置またはタッチパネルセンサーの配線用膜であって、合金成分としてX群元素(Xは、希土類元素、Ge、Si、Sn、Hf、Zr、Mg、Ca、Sr、Al、Zn、Mn、Co、Fe、及びNiよりなる群から選択される少なくとも一種の元素)を3〜50原子%、および/または酸素を0.2〜3.0質量%含有し、残部Tiおよび不可避不純物からなるTi合金層と、純CuまたはCu合金からなる層とを含む2層以上の積層構造を有することに要旨を有する配線用膜。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタの作製に用いるフォトリソグラフィ工程を従来よりも少なくし、且つ、信頼性の高い半導体装置を提供する。

【解決手段】第1の基板上に酸化物半導体層を有するトランジスタを含む回路と、当該第1の基板とシール材で固定された第2の基板とを有し、当該シール材、当該第1の基板、及び当該第2の基板で囲まれる閉空間は、減圧状態、或いは乾燥空気を充填する半導体装置に関する。当該シール材は、少なくとも前記トランジスタを囲み、閉じられたパターン形状を有する。また当該回路は、酸化物半導体層を有するトランジスタを含む駆動回路である。

(もっと読む)

アクティブマトリクス基板、電気光学装置及び電子機器

【課題】レイアウトの自由度を高め、基板上の熱源による表示品質の低下を防止できるアクティブマトリクス基板を提供する。

【解決手段】走査線22、データ線24及び画素26を含む画素回路と、半導体基板の一辺に沿って形成された複数のパッドを含む入力パッド部30と、高速シリアルインターフェース回路40と、高速シリアルインターフェース回路からの出力に基づいて階調データを生成するロジック回路50と、階調データに基づいて複数のデータ線を駆動するデータ線駆動回路60と、制御信号に基づいて走査線を駆動する走査線駆動回路70とを有し、半導体基板の一辺と画素回路との間で、該一辺側から順に、入力パッド部、高速シリアルインターフェース回路及びロジック回路が配置され、ロジック回路と画素回路との間に、データ線駆動回路及び走査線駆動回路の一方が配置される。

(もっと読む)

反射型液晶表示装置及び液晶プロジェクターシステム

【課題】 遮光だけでは抑制できない、入射してしまう光により生じる電子(ホール)による影響を抑制する。

【解決手段】 トランジスタのドレイン領域34よりも、多数キャリアに対して、ドレイン領域における電圧とQ(単位電荷量)との積の基準値よりも低いポテンシャルとされる領域36を設けるか、もしくはドレイン領域の周りにポテンシャル障壁を設ける。かかる構成により、フローティングとなる反射電極30と接続されたドレイン領域34の回りのポテンシャル制御を行い、半導体基板内に発生した光キャリアがドレイン領域34に導かれにくくする。

(もっと読む)

半導体装置

【課題】基板の大型化に対応し得る金属配線を作製する。

【解決手段】絶縁表面上に少なくとも一層の導電膜12,13を形成し、前記導電膜12,13上にレジストパターンを形成し、前記レジストパターンを有する導電膜にエッチングを行い、バイアス電力密度、ICP電力密度、下部電極の温度、圧力、エッチングガスの総流量、エッチングガスにおける酸素または塩素の割合に応じてテーパー角αが制御された金属配線を形成する。このようにして形成された金属配線は、幅や長さのばらつきが低減されており、基板10の大型化にも十分対応し得る。

(もっと読む)

表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い表示装置を提供する。消費電力が少なく、信頼性の高い表示装置を提供する。

【解決手段】トランジスタの、ゲート電極となる導電層、ゲート絶縁層となる絶縁層、半導体層、およびチャネル保護層となる絶縁層を連続して形成する。ゲート電極(同一層で形成される他の電極または配線を含む)と島状半導体層の形成を、一回のフォトリソグラフィ工程で行う。該フォトリソグラフィ工程と、コンタクトホールを形成するフォトリソグラフィ工程と、ソース電極及びドレイン電極(同一層で形成される他の電極または配線を含む)を形成するフォトリソグラフィ工程と、画素電極(同一層で形成される他の電極または配線を含む)を形成するフォトリソグラフィ工程の、4つのフォトリソグラフィ工程で表示装置を作製する。

(もっと読む)

半導体膜の形成方法、並びに、その半導体膜を用いた半導体装置、ディスプレイ装置。

【課題】結晶欠陥が低減されて結晶性が良好な半導体膜の形成方法及びその成方法を用いて製造された半導体装置並びにディスプレイ装置を提供する。

【解決手段】ガラス基板11上に非晶質シリコン膜12を形成する工程と、非晶質シリコン膜12の表面に、結晶化を促進する触媒物質であるニッケルを含むニッケル薄膜13を形成する工程と、非晶質シリコン膜12を熱処理して、非晶質シリコン膜12を結晶性シリコン膜12に結晶化する工程と、結晶性シリコン膜12に、隣接する各結晶粒の結晶方位角度差が、概略10°以下あるいは58°〜62°を保持する最も高い値になるようなエネルギー密度を有するエキシマレーザーを照射して、結晶性シリコン膜12の結晶性をさらに向上させて多結晶半導体膜とする工程とを包含する。

(もっと読む)

液晶表示装置

【課題】特性劣化に関係するデータ線Di+及びDi-の寄生容量が一番大きいのがウェルであることに着目し、ウェル電圧が揺すれないようにすることで、表示画面の横帯の発生や、フリッカ、焼きつきの発生を防止する。

【解決手段】ソースフォロワ用PMOSトランジスタTr3及びTr4の定電流負荷として機能するPMOSトランジスタTr10は、電流供給端子Xに印加される電源電圧VD2と、PMOSトランジスタTr10及び画素10内の他のPMOSトランジスタの各バックゲートであるNウェル端子に印加される電源電圧VDDとが、互いに異なる電源から印加され、かつ、同一電圧である。これにより、ソースフォロワ・バッファに電流を流す場合において電圧降下が見られる端子は電流供給端子Xのみとなり、PMOSトランジスタのNウェル端子に電圧降下の影響を及ぼすことがなくNウェル電圧を固定できる。

(もっと読む)

半導体膜、半導体素子、半導体装置およびそれらの作製方法

【課題】特性が安定した半導体膜を提供することを目的の一とする。または、特性が安定した半導体素子を提供することを目的の一とする。または、特性が安定した半導体装置を提供することを目的の一とする。

【解決手段】具体的には、絶縁性の表面に一方の面を接する第1の結晶構造を有する結晶を含む種結晶層(シード層)と、当該種結晶層(シード層)の他方の面に異方性の結晶が成長した酸化物半導体膜を有する構成とすれば良く、このようなヘテロ構造とすることにより、当該半導体膜の電気特性を安定化することができる。

(もっと読む)

発光装置の作製方法

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って剥離することを可能とする。

【解決手段】基板上に金属層を形成する工程と、前記金属層上に酸化物層を形成する工程と、前記酸化物層上に絶縁層を形成する工程と、前記絶縁層上に薄膜トランジスタを形成する工程と、前記薄膜トランジスタ上に発光素子を形成する工程と、人間の手又は前記薄膜トランジスタを引き剥がす装置を用いることにより、前記酸化物層の層内または界面において前記基板から前記薄膜トランジスタを剥離する工程とを有する。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】混相粒の粒径の均一性が高く、且つ結晶性の高い微結晶半導体膜を作製する。または、電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】粒径の均一性が高く、且つ高い結晶性を有する混相粒を低い粒密度で与える第1の条件により、非晶質シリコン領域と、単結晶とみなせる微小結晶である結晶子とを含む混相粒を有する種結晶を絶縁膜上にプラズマCVD法により形成した後、当該種結晶上に、混相粒を成長させて混相粒の隙間を埋める第2の条件で、種結晶上に微結晶半導体膜をプラズマCVD法により積層形成する。

(もっと読む)

可変容量素子、及び液晶表示装置

【課題】制御性が良く、安定して動作する可変容量素子を提供する。消費電力が少なく、表示品位の良い液晶表示装置を提供する。

【解決手段】印加される電界により、n型またはi型となる半導体、もしくは、p型またはi型となる半導体を用いて可変容量素子を構成する。容量素子を構成する第1の電極と第2の電極の間に、誘電体層として絶縁層と上記半導体層の積層を設ける。第1の電極を誘電体層側に設け、第2の電極を半導体層側に設けた時に、第1の電極と半導体層が重畳する面積C1よりも、第1の電極と半導体層と第2の電極が重畳する面積C2の方を小さくなるようにする。動画像表示と静止画像表示で駆動方法を切り替える液晶表示装置に可変容量素子を適用することで、消費電力が少なく、表示品位の良い液晶表示装置を実現できる。

(もっと読む)

反射型液晶表示装置及び反射型液晶表示装置用の基板

【課題】画素サイズが小さくなったときでも、信号線と保持容量端との間のクロストークを減少させ、良好な出力画像が得られる反射型液晶表示装置を提供する。

【解決手段】各画素に画像信号を伝送する信号線2を第2メタル層で形成し、保持容量を構成する容量電極10と信号線2との間に第1メタル層でシールド線12を配置し、固定電位を与え、シールドを施しクロストークの発生を防ぐ。保持容量は半導体基板上に形成された拡散層からなる共通電極11と容量電極10とで構成される。信号線下に半導体基板上に形成された拡散層からなる容量電極と、固定電位とされた共通電極を配置し、シールドを施しクロストークの発生を防ぐ。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

液晶表示素子及びその駆動方法

【課題】ランプ信号を用いることなくDA変換を行う構造とすることでランプ信号の波形の変形による表示画像の不具合を解消する。

【解決手段】1H内において、表示する映像信号の画素値と一定周期のクロックを計数するカウンタのカウンタ値とを比較し、画素値とカウンタ値とが一致した時に、データ線VDjの電位がそれまでのaからbに変化する。蓄積ゲートGSは、ゲート線AGiの電圧が、電位aよりも低い電位cから電位よりも高い電位dに変化した時に、VDjから一定量の電荷を転送されて蓄積する。転送ゲートGTは、ゲート線TGiの電圧が、電位cよりも低い電位eから電位cよりも高い電位fに変化した時に、上記の蓄積電荷を保持容量CSに転送して保持させる。データ線VDjの電位がbに変化するまで、上記の蓄積と転送の動作を巡回的に繰り返し、その繰り返し回数に応じた電荷量を保持容量CSに保持する。

(もっと読む)

補助蓄積コンデンサを有するCMOS技術における透過型液晶ディスプレイ

【課題】補助蓄積コンデンサを有するCMOS技術における透過型液晶ディスプレイを提供する。

【解決手段】本発明は、能動マトリックスの液晶ディスプレイによる画像表示に関する。それはとりわけ、例えば(LCOS、すなわちLiquid Crystal on Silicon技術=シリコン上の液晶技術により、)シリコン基板上に作られる小型ディスプレイに適用可能である。

補助蓄積コンデンサ(Cst)は画素の駆動トランジスタ上に形成され、すなわち駆動トランジスタは液晶と蓄積コンデンサとの間に形成される。蓄積コンデンサは、各々がそれぞれの金属化階層(M1〜M5)において相互に入り込んだ構造を有する、複数で並列の部分的コンデンサから形成される。金属化(アルミニウム及び/又は銅)は不透明で、コンデンサは従ってトランジスタを光から保護し、その保護レベルは相互に入り込んだ構造を形成するために使用される金属化階層の数が多いほど良好である。

(もっと読む)

半導体装置及びその作製方法

【課題】マスク枚数を増加させることなく、積層構造の導電層の下層が露出した構造を有する半導体装置の作製方法を提供する。

【解決手段】ソース電極及びドレイン電極層を形成する導電膜を2層の積層構造で形成し、該導電膜上にエッチングマスクを形成し、該エッチングマスクを用いて該導電膜をエッチングし、該エッチングマスクを残した状態で該導電膜の上層をサイドエッチングして該導電膜の下層の一部を露出させてソース電極及びドレイン電極層とする。このように形成したソース電極及びドレイン電極層と画素電極層は、露出された下層の部分において接続される。ソース電極及びドレイン電極層を形成する導電膜は、例えば、下層をTi層とし、上層をAl層とすればよい。エッチングマスクに開口部が複数設けられていてもよい。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

表示装置及びその製造方法

【課題】アクティブマトリクス表示装置に形成される平坦化膜に局所的な厚みの違いを設けてパネル構造を改善する。

【解決手段】一対の基板1,2と電気光学物質3とからなるパネル構造を有し、一方の基板1には薄膜トランジスタの集合と平坦化膜5と画素電極の集合とが形成されており、各画素電極には異なった表示色が割り当てられている表示装置の製造方法であって、平坦化膜5を形成する工程は、感光性材料から成る平坦化膜5を一方の基板上に塗工する塗工工程と、露光量の平面分布に変化をつけた状態で平坦化膜5の感光処理を行う露光工程と、感光した平坦化膜5を現像して平坦化膜5の厚さを露光量の平面分布に応じて異なるように加工し、以て、平坦化膜5の各画素電極に対応する部分の厚さを、各画素電極に割り当てられた表示色の波長に応じて異ならせる加工工程とを含む。

(もっと読む)

液晶表示装置

【課題】各画素内の正極性信号側画素回路部と負極性信号側画素回路部で互いに対になっている回路構成要素及び配線同士を、仮想の画素中心線に対して線対称で配置構成することにより、画素ピッチを増大させることなく液晶素子に正常な駆動電圧を印加する。

【解決手段】Vdd配線102、Cs1接続配線104、データ線Di+用配線106などの正極性信号側画素回路部の配線と、Vdd配線103、Cs2接続配線105、データ線Di-用配線107などの負極性信号側画素回路部の配線とは、画素中心線II−II’に対して対応する配線同士が線対称位置に配置されている。Vdd配線102とVdd配線103とは、1画素内の左右両端に配置されているため、左右両隣の画素のCs1接続配線、又はCs2接続配線からのクロストークを抑制するガードパターンの役割を果たしている。データ線Di+用配線106及びデータ線Di-用配線107は、画素の中心部付近に配置されている。

(もっと読む)

21 - 40 / 295

[ Back to top ]