Fターム[2H092NA27]の内容

液晶−電極、アクティブマトリックス (131,435) | 目的 (17,448) | その他 (8,438) | 製造方法の簡略化 (2,391)

Fターム[2H092NA27]に分類される特許

1 - 20 / 2,391

粘着テープの貼着装置及び貼着方法

液晶装置、液晶装置の製造方法及びプロジェクター

【課題】光の利用効率に優れると共に、容易に製造可能な液晶装置、液晶装置の製造方法及びプロジェクターを提供すること。

【解決手段】対向配置され、複数の画素領域が設けられた一対の基板と、前記一対の基板に挟持された液晶層と、前記一対の基板のうち第一基板において複数の前記画素領域のそれぞれに対応して設けられたスイッチング素子と、前記一対の基板のうち前記第一基板において前記スイッチング素子よりも前記液晶層側に設けられ、前記画素領域ごとに配置された複数の第一光屈折部と、前記一対の基板のうち前記第一基板とは異なる第二基板に設けられ、前記画素領域ごとに配置された複数の第二光屈折部とを備え、前記第一光屈折部及び前記第二光屈折部のうち、一方は曲面状に形成されており、他方は平面視で前記画素領域の中央部へ向けて傾斜する複数の平面によって形成されている。

(もっと読む)

トランジスタ、表示装置および電子機器

【課題】良好な歩留りで製造可能なトランジスタ、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層に電気的に接続された一対のソース・ドレイン電極と、前記一対のソース・ドレイン電極それぞれと前記半導体層との間のキャリア移動経路に設けられ、その端面が前記ソース・ドレイン電極に覆われたコンタクト層と、を備えたトランジスタ。

(もっと読む)

コンタクトホールの形成方法および電気光学装置の製造方法

【課題】シュリンク技術を利用して、コンタクトホールとして利用できる複数の凹部を1回のレジストマスク工程で異なる深さ寸法に形成することのできるコンタクトホールの形成方法、および電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置の素子基板10上にコンタクトホールを形成するにあたって、まず、第1開口部17aおよび第2開口部17bを備えたレジストマスク17を層間絶縁膜42の表面に形成した後、第1開口部17aおよび第2開口部17bから層間絶縁膜42および絶縁膜49をエッチングする。その後、シュリンク工程において、レジストマスク17を変形させて第2開口部17bを塞ぐ一方、第1開口部17aの開口面積を狭める。次に、第1開口部17aから層間絶縁膜41およびゲート絶縁層2をエッチングする。

(もっと読む)

液晶表示装置

【課題】コストの削減を可能とするとともに表示品位の劣化を抑制することを可能とする。

【解決手段】 第1方向に延出した第1補助容量線及び第2補助容量線と、第1補助容量線と第2補助容量線との間に位置し第1方向にゲート配線と、画素の略中央でゲート配線の上方に位置する半導体層と、半導体層とコンタクトし第2方向にソース配線と、半導体層にコンタクトし第1補助容量線及び第2補助容量線の上方に延出したドレイン電極と、ドレイン電極と電気的に接続され第1補助容量線と対向し第1方向に延出した第1主画素電極及びドレイン電極と電気的に接続され第2補助容量線と対向し第1方向に延出した第2主画素電極を備えた画素電極と、を備えた第1基板と、第1主画素電極を挟んだ両側及び第2主画素電極を挟んだ両側に位置し第1方向に延出した主共通電極を備えた共通電極を備えた第2基板と、を備えた液晶表示装置。

(もっと読む)

電気光学装置および電子機器

【課題】製造コストを大幅に増大させずに情報を記録することができるとともに、情報を容易に再生することのできる電気光学装置、および電子機器を提供すること。

【解決手段】電気光学装置100の素子基板10において、外周領域10cに複数の容量素子56を形成しておき、外部からいずれの容量素子56に高い電圧を印加して絶縁破壊させるかによって、電気光学装置100の一つ一つにID等情報を記録する。容量素子56は、ダミー画素100bに設けた蓄積容量55であり、データ線6a、走査線3aおよび容量線5bのうち、外周領域10cで延在している部分を配線として利用して、容量素子56への電圧印加および信号検出を行う。

(もっと読む)

表示装置

【課題】製造容易な表示装置を提供する。

【解決手段】複数の導光部のそれぞれは、一端と、他端と、一端から他端に向かう第1方向に沿って延在する側面と、を有する。複数の導光部は、第1方向に対して交差する第2方向に、互いに離間しつつ並ぶ。光源は、導光部の一端から導光部中に光を入射させる。支持基板は、導光部の側面に接する第1主面と、第1主面とは反対側の第2主面と、を有し、前記側面に接する部分が透明である。第1電極は、第2主面に設けられた光透過性の電極である。対向基板は、第2主面と対向し、第1電極と離間して設けられる。第2電極は、対向基板の前記第2主面と向かい合う面に設けられた光透過性の電極である。複数のスペーサは、支持基板と対向基板との間に設けられ、第1方向及び第2方向に対して平行な平面に射影したときに、複数の導光部間に配置される。

(もっと読む)

半導体装置の作製方法

【課題】本発明の一態様は、スパッタ法でトランジスタ、ダイオード等の半導体用途に好

適な材料を提供することを課題の一とする。

【解決手段】下地部材上に、第1の酸化物部材を形成し、第1の加熱処理を行って表面か

ら内部に向かって結晶成長し、下地部材に少なくとも一部接する第1の酸化物結晶部材を

形成し、第1の酸化物結晶部材上に第2の酸化物部材を形成し、第2の加熱処理を行って

第1の酸化物結晶部材を種として結晶成長させて第2の酸化物結晶部材を設ける積層酸化

物材料の作製方法である。

(もっと読む)

液晶表示装置、表示モジュール及び電子機器

【課題】アクティブマトリクス型基板において、薄膜トランジスタと、その端子接続部を同時に作り込み、少ないマスク数で歩留まりの良い表示装置を提供する。

【解決手段】画素部および外部入力端子を有する表示装置であって、画素部は、ゲート電極と、半導体膜と、ゲート電極上に形成された絶縁膜、および絶縁膜上に半導体膜と電気的に接続された電極を有するTFTを有し、外部入力端子は、ゲート電極と同じ層に形成された第1の配線と、電極と同じ層に形成され、絶縁膜に形成されたコンタクトホールを介し第1の配線と接続された第2の配線と、第2の配線に接続され、第2の配線上に形成された透明導電膜と、第2の配線と透明導電膜が接続している位置で透明導電膜と電気的に接続するフレキシブルプリント配線板を有する表示装置。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極や走査線(ゲート線)及びデータ線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供する。

【解決手段】半導体膜107と基板との間に第1の絶縁膜を介して設けられた第1の配線102を、半導体膜107と重ねて設け、遮光膜として用いる。さらに半導体膜上にゲート絶縁膜として用いる第2の絶縁膜を形成し、第2の絶縁膜上にゲート電極と第2の配線134を形成する。第1及び第2の配線は、第1及び第2の絶縁膜を介して交差する。第2の配線134の上層には、層間絶縁膜として第3の絶縁膜を形成し、その上に画素電極147を形成する。画素電極147は、第1の配線及び第2の配線とオーバーラップさせて形成することが可能であり、反射型の表示装置において画素電極147の面積を大型化できる。

(もっと読む)

液晶表示装置の製造方法

【課題】 製造工程を単純化して第1の金属膜上に第2の金属層が積層された積層構造を有する領域および第1の金属膜のみで形成されている領域からなるゲート配線を製造することができる液晶表示装置の製造方法を提供する。

【解決手段】 液晶表示装置の製造方法であって、第1の金属膜3b上に第2の金属膜3cが積層された積層構造を有する領域および第1の金属膜3bのみで形成されている領域からなるゲート配線3を、多階調マスクを用いて、感光性樹脂膜12を、積層構造となる領域では膜厚の厚い厚膜部12aになり、ゲート電極3aの少なくとも半導体層5と重なっている領域では厚膜部12aよりも膜厚の薄い薄膜部12bになるようにそれぞれ複数のゲート配線3のパターンにするとともに、隣接するゲート配線3のパターン間の領域では第2の金属膜3cが露出するようにパターニングする工程を含んでいる。

(もっと読む)

液晶表示装置

【課題】コストの削減を可能とするとともに表示品位の劣化を抑制することを可能とする。

【解決手段】第1方向に沿って延出した第1補助容量線及び第2補助容量線と、第1補助容量線と第2補助容量線との間に位置し第1方向に沿って延出したゲート配線と、第2方向に沿って延出したソース配線と、半導体層と、ゲート配線と電気的に接続されたゲート電極と、半導体層にコンタクトしソース配線と電気的に接続されたソース電極と、半導体層にコンタクトした第1電極部、第1電極部に繋がり第1補助容量線と対向し第1方向に沿って延出した第2電極部、及び、第1電極部に繋がり第2補助容量線と対向し第1方向に沿って延出した第3電極部を備えたドレイン電極と、を備えた第1基板と、第2電極部を挟んだ両側及び第3電極部を挟んだ両側にそれぞれ位置し第1方向に沿ってそれぞれ延出した主共通電極を備えた第2基板と、を備えた液晶表示装置。

(もっと読む)

液晶表示装置及びその製造方法

【課題】フォトリソグラフィ工程を増やすことなく液晶表示装置を製造することを目的とする。

【解決手段】液晶表示装置は、第1透明電極14の端部に載る第1絶縁層30と、第1絶縁層30下のゲート電極18と、第1絶縁層30上の半導体層34と、半導体層34上から第1透明電極14上に至るように形成されて第1透明電極14に電気的に接続する第1配線46と、第1配線46から間隔をあけて半導体層34上から引き出された第2配線48と、第1配線46、第2配線48、半導体層34及び第1透明電極14を覆う第2絶縁層54と、第2絶縁層54上に形成された第2透明電極60と、第2透明電極60の上に配置された液晶層66と、を有する。第1透明電極14と第2透明電極60の間に印加される電圧によって、基板10の面方向に電界を加えて、液晶層66の液晶分子を基板10と平行な面内で回転させる。

(もっと読む)

電気光学装置、及び電子機器

【課題】液晶装置等の電気光学装置において、保持容量を十分に確保することができ、高品質な画像を表示可能とする。

【解決手段】ゲート電極30gと電気的に接続された走査線3aと、データ線側ソースドレイン領域30sと電気的に接続されたデータ線6aと、画素電極側ソースドレイン領域30dと電気的に接続された画素電極27と、容量線3bに電気的に接続された第1容量電極16aと、第1容量電極16aと対向して設けられた第2容量電極16cと、第1容量電極16aと第2容量電極16cとに挟持された誘電体層16bと、を有する容量素子16と、を備え、層間絶縁膜11eに設けられた複数の第1コンタクトホールCNT4を介して第1容量電極16aと容量線3bとは電気的に接続される。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

中継部材及び接続方法

【課題】電極数が多く、かつ、その電極の配置間隔が狭い電子デバイスを他の電子デバイスに実装する際、簡便に行うことが可能な中継部材及び接続方法を提供する。

【解決手段】中継部材は、複数の第1電極部を有する第1電子デバイスと、複数の第2電極部を有する第2電子デバイスとを電気的に接続する。中継部材は、第1電極部に接続される複数の入力電極部と、所定ピッチで周期的に配置される複数の第2電極部に接続される複数の出力電極部とを有し、複数の出力電極部は、n個のグループに分類され、複数の出力電極部は、所定ピッチの略1/nのピッチで周期的に配置され、一のグループに属する出力電極部は、他のグループに属する出力電極部と隣接するように周期的に配置されるとともに、グループごとに異なるように設定された接続位置のうちのいずれか一つに配置された入力電極部に連結されている。

(もっと読む)

保護膜溶液組成物、薄膜トランジスター表示板及び薄膜トランジスター表示板の製造方法

【課題】保護膜溶液組成物を提供すること。

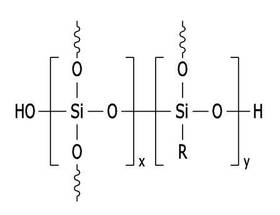

【解決手段】下記の化学式1で表わされる有機シロキサン樹脂を含む保護膜溶液組成物:

・・・化学式1

(式中、Rは1乃至25個の炭素を有する飽和炭化水素または不飽和炭化水素から選ばれた少なくとも一つの置換基であり、x、yはそれぞれ1乃至200であり、各波線は水素原子、xシロキサン単位またはyシロキサン単位との結合を示すか、あるいは、xシロキサン単位、yシロキサン単位またはこれらの組み合わせを含む他の有機シロキサン鎖のxシロキサン単位またはyシロキサン単位との結合を示す)。

(もっと読む)

ACF貼付装置及びFPDモジュール組立装置

【課題】搭載部材の位置に合わせてACFを移動させ、搭載部材に正確にACFを貼り付けることを提供する。

【解決手段】ACF貼付装置は、撮像部216と、位置検出部と、制御部223と、ACFを切断する切断部と、ACF貼付部239と、を備える。位置検出部は、撮像部216により撮像された搭載部材7の端部の画像とアライメントマークの画像から、搭載部材7の端部の位置とアライメントマークの位置を検出する。制御部223は、検出されたアライメントマークの位置と搭載部材7の端部の位置から搭載部材7に対するACFの貼り付け位置を算出する。ACF貼付部239は、制御部223が算出したACFの貼り付け位置に合わせて、切断部により切断されたACFを搭載部材7に貼付する。

(もっと読む)

半導体装置、モジュール、及び電子機器

【課題】大量生産上、大型の基板に適している液滴吐出法を用いた製造プロセスを提供す

る。

【解決手段】液滴吐出法で感光性の導電膜材料液を選択的に吐出し、レーザ光で選択的に

露光した後、現像またはエッチングすることによって、レーザ光で露光した領域のみを残

し、吐出後のパターンよりも微細なソース配線およびドレイン配線を実現する。TFTの

ソース配線およびドレイン配線は、島状の半導体層を横断して重ねることを特徴としてい

る。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 光リーク電流を抑制した高い耐光性を有するTFTを、製造工程を簡素化することにより低コストで実現する。

【解決手段】 TFT100は、絶縁基板107としてのガラス基板上に形成された遮光膜113と、遮光膜113上に形成された絶縁膜112と、絶縁膜112上に形成された半導体膜111と、半導体膜111上に形成されたゲート絶縁膜104とを基本的に有する。遮光膜113、絶縁膜112及び半導体膜111の三層から成る積層体100aは、各層が同時にパターニングされている。そして、積層体100aの各層がシリコン又はシリコンを含む材料から成る。

(もっと読む)

1 - 20 / 2,391

[ Back to top ]