Fターム[4G077BE46]の内容

結晶、結晶のための後処理 (61,211) | 材料−〜化物 (3,360) | 3−5化合物(5族元素はP、As、Sb) (368) | As化物 (195) | GaAs (176)

Fターム[4G077BE46]に分類される特許

81 - 100 / 176

半導体結晶の製造方法及びその製造装置

【課題】引上げ法により結晶を成長させる際に、成長初期から成長完了までに亘って、融液の温度制御精度を安定に保ち、原料を無駄なく活用しつつ、外径の制御性の良い結晶を成長させる方法を提供する。

【解決手段】ルツボ5内に収容した原料8を加熱、融解し、ルツボ5内に得られた原料融液12に種結晶10を接触させつつ、種結晶10を引上げて単結晶13を得る、CZ法、LEC法を含む半導体結晶の製造方法において、ルツボ5とルツボ5を支持する支持部材4の間に、ルツボ5、原料とは異なる材質の介在物6を挿入する。

(もっと読む)

単結晶製造方法

【課題】ルツボの径に合った最適なルツボの回転数が決定できる単結晶製造方法を提供する。

【解決手段】原料を入れたルツボ4を回転させつつ該ルツボ4を外周側から加熱して上記原料を融液化させ、上記ルツボ4の中央部で原料融液3の液面に種結晶9を接触させた後、該種結晶9を液面から離していくことにより、該種結晶9の下部に単結晶10を成長させる際に、上記ルツボ4の回転数n(rpm)を上記ルツボ4の半径r(m)に対して

n≧4.3e8.0r(eは自然対数の底)

とするものである。

(もっと読む)

量子ドット作製法と量子ドット半導体

【課題】従来に望むことの出来ない高密度で、かつサイズ揺らぎの少ない均一な量子ドットの作成が可能な方法を提供する。

【解決手段】従来のGaAs(100)基板でなく、GaAs(311)A基板上にガリウムのみを供給して液状のガリウム金属微粒子を作製し、その液滴に砒素分子線を照射してガリウム砒素に結晶化することにより、サイズ揺らぎの少ない量子ドットを作製する。

(もっと読む)

半導体素材から欠陥を除去する方法

ヘリウム低温槽を用い基板ウェハ(群)の温度を24時間かけて2.2Kまで低下させる。浸漬段階では、基板ウェハの温度を96時間に亘り2.2Kに保持することで、分子間結合距離を収縮させ、ひいてはGaAs、InP、GaP等の合金に生じる分子双極子モーメントを内部磁力線沿いに再整列させる。24時間かけてその基板ウェハの温度を室温に戻したら、その基板ウェハ内に生じる温度勾配を小さな値に保ちながら、その基板ウェハを組成している単結晶素材に応じた温度、例えば華氏300〜1100度域内のある温度まで、その基板ウェハを一時昇温させる。一時保温段階ではその基板ウェハ全体に一時昇温の効果を行き渡らせる。  (もっと読む)

(もっと読む)

原料の溶融物から結晶を製造するための構成および方法、ならびに単結晶

【課題】原料の溶融物から結晶を製造するための構成および単結晶を提供すること。

【解決手段】原料の溶融物(16)から結晶を製造するための構成(1)は、第1の方向(18)に指向する勾配温度領域(T)を発生するように構成される1つ以上の加熱要素を有する加熱装置(20、21)を含む炉と、勾配温度領域(T)に並べて配置され、溶融物(16)を収容する少なくとも2つの複数のルツボ(14)と、少なくとも2つのルツボ(14)内において、第1の方向(18)に垂直な面内の温度領域(T)を均一化するための装置(21a、21b、46、26)とを備える。その装置は、ルツボ(14)間の空間(23)内に配置される充填材料(24)を含み、径方向に向けた熱移動を発生させるため、充填材料(24)に異方性熱伝導率を生じさせる。その構成は、充填材料(24)に協同する移動磁界を発生させる装置でもよい。

(もっと読む)

エッチピット密度(EPD)が低い半絶縁性のIII−V族ウェハ

【解決手段】 EPDが低くなるような結晶成長プロセスを用いてウェハを製造するシステムおよび方法が開示されている。また、デバイス収率を高め得る第III−V族/GaAsウェハを形成する、ウェハアニーリングプロセスが提供されている。一実装例によると、エッチピット密度(EPD)が低い第III族ベースの材料を製造する方法が提供される。さらに、当該方法は、多結晶第III族ベース化合物を形成する段階と、当該多結晶第III族ベース化合物を用いて垂直温度勾配凝固による結晶成長を実行する段階とを備える。その他の実装例は、第III族ベース結晶を形成する際に温度勾配を制御して、エッチピット密度を非常に低くする段階を備えるとしてよい。 (もっと読む)

半絶縁性GaAsウエハ及びその製造方法

【課題】 処理後のウエハの不良品発生率を低減することが可能な半絶縁性GaAsウエハ及びその製造方法を提供する。

【解決手段】 直径Φが4インチ以上の半絶縁性GaAsウエハであって、ウエハの半径Rに対してウエハ中心から(2/3)・Rの半径を有する円の部分を中心部とし、前記ウエハ面内の中心部以外の部分である外周部の平均転位密度が、前記中心部の平均転位密度より大きい。

(もっと読む)

中赤外光用半導体デバイスの製造方法

【課題】良質でなおかつ既存のものに比べて高性能な半導体デバイスを、安価に製造することができる、中赤外光領域で作動する半導体デバイスの製造方法を提供する。

【解決手段】

結晶基板1上にバッファ層2を積層して形成した基本積層体3上に、特定のエッチング液により選択的に除去可能な薄厚の犠牲層4を積層する犠牲層積層ステップと、その犠牲層上にデバイス層5を形成した後、犠牲層4のみをエッチング除去して前記デバイス層5を前記基本積層体3から分離するデバイス層分離ステップと、前記デバイス層分離ステップにおいてデバイス層5とともに分離された前記基本積層体3に対し、前記犠牲層積層ステップ及びデバイス生成ステップを再度施す再利用ステップと、を有するようにした。

(もっと読む)

化学蒸着によりウェハ上にエピタキシャル層を成長させる装置および方法

【課題】固体基板上のCVDリアクタとそのウェハ上にエピタキシャル層を蒸着させる装置のリアクタ・サイクルの低減と、構成部品の低コストおよび長寿命と、高精度の温度制御とを提供する。

【解決手段】リアクタ内にウェハ・キャリヤ110を装着し、装着位置と蒸着位置Dの間を移動する。蒸着位置では、ウェハ・キャリヤは、中間サセプタを必要とせずに、回転式スピンドル120の上端に取り外し可能に取り付けられる。リアクタは、単一ウェハまたは同時に複数のウェハを処理できる。1つの変形形態では、スピントルを通るウェハ支持アセンブリの熱放散の低減と、そのための新規の加熱機構。

(もっと読む)

半導体結晶

【課題】低コストで製造することができる大型で良質な半導体結晶を提供する。

【解決手段】化合物からなる半導体結晶50であって、直径が6インチ以上であり、平均転位密度が1×104cm-2以下である。半導体結晶50においては、平均転位密度が5×103cm-2以下であることが好ましく、また、直径が8インチ以上であることが好ましい。化合物の材料としては、GaAsとするか、または、CdTe、InAsおよびGaSbからなる群から選ばれるいずれか1つとする。

(もっと読む)

III−V族半導体基板からのバルク金属汚染の除去方法

【課題】III−V族半導体基板からバルク金属汚染を除去するための単一工程の方法を提供する。

【解決手段】該方法は、金属汚染したIII−V族半導体基板を、体積比x:y H2SO4:H2O2(xは3〜9、yは1)を有する硫酸および過酸化物の混合物の中に浸漬することを含む。本発明の実施形態に係る方法を用いてIII−V族半導体基板を処理した後、バルク金属汚染は、基板からほぼ完全に除去できるとともに、処理後の基板の表面粗さは、2μm×2μmの表面グリッドに関して0.5nmRMS未満とすることができる。本発明は、半導体デバイスを製造する更なる処理ステップを実施する前に、本発明の実施形態に係るバルク金属汚染を除去する方法を用いて、半導体デバイスを製造するための方法を提供する。

(もっと読む)

SiドープGaAs単結晶

【課題】良好なキャリア濃度分布を有するSiドープGaAs単結晶並びにその製造方法及び装置を提供する。

【解決手段】液体封止剤を用いた縦型ボート法によるSiドープGaAs単結晶の製造方法による結晶育成過程において、適正な時期に液体封止剤層を撹拌することにより、GaAs原料融液層中のSi濃度を制御し、単結晶中の位置を結晶育成過程における結晶の固化率gで表して(1−g)の対数値を横軸にとり、各固化率で特定される位置における単結晶中のキャリア濃度の対数値を縦軸にとったグラフに表される曲線が、固化率gが0.1〜0.8の範囲において、勾配が負の値を持ち、かつその勾配の絶対値が0.6より大きい直線と勾配の絶対値が0.6以下の直線とが接続されたものであるSiドープGaAs単結晶を得る。

(もっと読む)

III族金属窒化物単結晶の育成方法およびテンプレート基板

【課題】テンプレート基板の種結晶膜上にIII 族金属窒化物単結晶を育成するのに際して、III 族金属窒化物単結晶のクラックや反りを抑制し、その生産性を向上させることである。

【解決手段】単結晶基板9と、この単結晶基板9の表面9aに形成された種結晶膜10とを備えているテンプレート基板8に、III 族金属窒化物単結晶を育成する方法を提供する。単結晶基板9の背面9bに、種結晶膜10の劈開面に平行な方向と異なる方向A(またはB)に向かって延びる凹部11(または12)を形成する。次いでIII 族金属窒化物単結晶を育成する。

(もっと読む)

多層構造ウエハーおよびその製造方法

【課題】シリコン基板上に、γ−Al2O3層を島状あるいは網状に形成することにより、一枚のシリコン基板から、高品質なSOI基板を提供する。

【解決手段】シリコン基板2の上面には、γ−Al2O3層4が島状あるいは網状に形成されている。熱処理を行なうことにより、γ−Al2O3層4の間から酸化シリコン層6が成長する。次に、γ−Al2O3層4の上面より単結晶シリコン層8が上方向に成長し、結晶欠陥の少ないSOI基板を得ることができる。

(もっと読む)

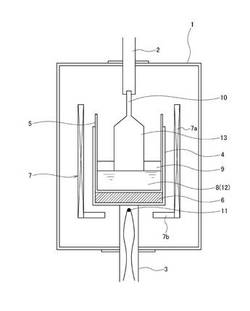

化合物半導体の製造方法及び装置

【課題】液体封止チョクラルスキー法によるGaAs等の化合物半導体単結晶の製造方法において、転位等の結晶欠陥の少ない良質な化合物半導体単結晶の収率を大幅に向上させる化合物半導体の製造方法を提供する。

【解決手段】容器内に原料融液Lと封止剤Mを収納し、その原料融液Lに種結晶Cを接触させ、容器あるいは種結晶Sを移動し、種結晶Sに化合物半導体の単結晶Cを成長させる製造方法において、少なくとも結晶成長初期に固液界面Fが原料融液側Lに凸化するように、種結晶Sの頭部を強制冷却手段12により強制冷却する。

(もっと読む)

化合物半導体エピタキシャルウェハの製造方法及び化合物半導体エピタキシャルウェハ

【課題】化合物半導体ウェハに温度歪みによる結晶欠陥を生じさせないための化合物半導体エピタキシャルウェハの製造方法及び化合物半導体エピタキシャルウェハを提供する。

【解決手段】化合物半導体ウェハの表面に、有機金属気相成長法を用いて化合物半導体結晶を成長させる方法において、上記化合物半導体ウェハの外周部の表面温度が、上記化合物半導体ウェハの中心部の表面温度の+15℃〜+30℃の範囲内となるように面内温度分布を制御する。

(もっと読む)

半絶縁性GaAsウエハ及びその製造方法

【課題】デバイス製造時アニール処理後にスリップが発生しない半絶縁性GaAsウエハ及びその製造方法を提供する。

【解決手段】半絶縁性GaAs単結晶を成長させた後に、前記半絶縁性GaAs単結晶をスライス加工して得られた半絶縁性GaAsウエハにおいて、前記半絶縁性GaAsウエハ面内の転位密度(以下、EPDと称する)が、

30,000個/cm2≦EPD≦100,000個/cm2

であり、かつ、前記半絶縁性GaAsウエハの半径方向歪をSr、円柱接線方向歪をStとするとき、前記半絶縁性GaAsウエハ面内の残留応力|Sr−St|が、

|Sr−St|≦1.8×10-5

である。

(もっと読む)

電子および/または光電子デバイスおよび関連する製造プロセス実現化に適した半導体基板

特に単結晶シリコンからなる少なくとも1つの基板(3)および単結晶シリコンの覆い層シリコン(5)を有するタイプの電子および/または光電子デバイスを実現するのに適している半導体基板(1)について記載する。有利なことに、本発明によれば、半導体基板(1)は、使われた材料の差違に関連した欠陥を減らすのに適している少なくとも1つの機能的カップリング層(10)を有している。特に、機能的カップリング層10は、単結晶シリコンからなる層(5)に形成され前述の使われた材料の結晶格子の差違に関連した欠陥を減らすのに適した波形状または山谷形状の部分(6)を有している。他の実施形態として、機能的カップリング層(10)は、単結晶シリコンからなる基板(3)および単結晶シリコンからなる層(5)の間に配置され、使われた材料の熱膨張率の差違によって生じたストレスを減らすのに適した多孔質層(4)を有している。前述の半導体基板の製造プロセスも記載されている。  (もっと読む)

(もっと読む)

気相成長方法

【課題】薄い半導体結晶層を成長する場合にも、半導体結晶層の層厚を均一化できる気相成長方法を提供する。

【解決手段】基板(1)を保持した自転サセプタ(2)を公転サセプタ(3)に設置して前記基板(1)を自公転させ、加熱された前記基板(1)上に原料ガス(G)を供給して基板(1)上に半導体

結晶を成長させる気相成長方法において、前記基板(1)上に一つの半導体結晶層を成長さ

せるのに要する基板(1)の自転回数が16回未満の場合に、前記一つの半導体結晶層を成

長させる時間を前記基板(1)の自転周期の整数倍とした。

(もっと読む)

化合物半導体単結晶基板及びその製造方法

【課題】VB法、VGF法によって製造された化合物半導体単結晶基板において、化合物半導体単結晶基板面内のキャリア濃度をより均一化した化合物半導体単結晶基板を提供する。

【解決手段】容器2の底部に予め配置した種結晶Sより結晶成長を開始し、徐々に上方に結晶化を進行させ、容器2内に収納した原料融液M全体を結晶化させ、得られた結晶を切断する方法によって製造された化合物半導体単結晶基板において、

以下の条件A〜条件Cのうち、

条件A:基板面内のキャリア濃度の平均値が1.0×1018〜5.0×1019/cm3 条件B:基板面内のキャリア濃度の最大値、最小値が、基板面内のキャリア濃度の平均値から±5%のばらつきの範囲内

条件C:基板面内の転位密度の平均値が0〜50個/cm2 の少なくとも2つの条件を満たすものである。

(もっと読む)

81 - 100 / 176

[ Back to top ]