Fターム[4G077FD02]の内容

結晶、結晶のための後処理 (61,211) | 後処理−電磁波、粒子線照射によるドーピング (69) | イオン注入によるもの (52)

Fターム[4G077FD02]の下位に属するFターム

イオン注入方法、イオン発生、加速装置 (18)

Fターム[4G077FD02]に分類される特許

1 - 20 / 34

化合物半導体の形成方法

【課題】高電圧駆動素子の為にSiCやGaNの基板の簡素化が重要な課題となっている。

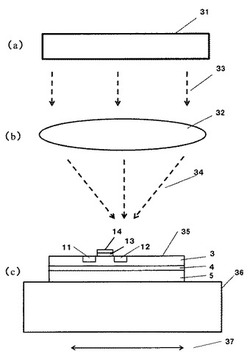

Si基板上のシリコン酸化膜の上に単結晶のSiC膜やGaN膜に形成したMOSFETなどの素子をアニールする手法を開示する。

【解決手段】光学ランプからの光をレンズで集光する手段、或いはレーザ光など高温度を発生させる手段によりSiCなど化合物半導体の表層部はSi基板の融点を越えるような高温度として、Si基板部はその融点よりも十分低い温度となるような冷却部を設けてSi基板を保持するステージを設けたことを特徴とするアニーリング装置。

(もっと読む)

自立基板の製造方法

【課題】反り及びクラックが発生することなく自立基板を製造することのできる自立基板の製造方法を提供する。

【解決手段】本発明は、異種基板上に第1薄膜を成長させる第1ステップ;イオンを注入して前記第1薄膜内にイオン注入層を形成する第2ステップ;前記イオン注入層を基準に、前記第1薄膜を上部薄膜と下部薄膜とに分離する第3ステップ;及び、前記上部薄膜上に第2薄膜を成長させる第4ステップを含むことを特徴とする自立(Free‐Standing)基板の製造方法を提供し、反り及びクラックが発生することなく自立基板を製造することができ、異種基板と成長した自立基板とを分離するためのレーザー(Laser)分離工程等の追加的な工程を必要としない効果を有する。

(もっと読む)

蛍光ナノダイヤモンド

【課題】ナノダイヤモンドに水素イオンやヘリウムイオンをイオン注入したナノダイヤモンドに比べて所定波長範囲内の波長の励起光に対して所定波長範囲内の波長の蛍光の光強度を大きくする。

【解決手段】ナノダイヤモンドに所定の元素がイオン注入されて形成され、波長範囲700〜900nm内の波長の励起光により励起されたときに、波長範囲700〜1400nm内の波長の蛍光を発することを特徴とする。

(もっと読む)

半導体デバイスの製造方法

【課題】支持基板と半導体層とを分離するために照射される光について、支持基板と半導体層との間に形成される中間層の光熱変換層で吸収されない光が半導体層に透過するのを防止する半導体デバイスの製造方法を提供する。

【解決手段】本半導体デバイスの製造方法は、光熱変換層21と第1の透明層23とを含む中間層20を有する積層支持基板1の作製工程と、積層貼り合わせ基板2の作製工程と、エピ成長用積層支持基板3の作製工程と、デバイス用積層支持基板4の作製工程と、デバイス用積層支持基板4の光熱変換層21で吸収され第1の透明層23で全反射されるように光照射することによるデバイス用積層ウエハ5の作製工程と、透明半導体積層ウエハ6を含む半導体デバイス7の作製工程と、を備える。

(もっと読む)

シリコンウェーハの製造方法

【課題】デバイス製造工程における熱処理を経た後にも高抵抗を維持するとともに、ウェーハの機械的強度及びゲッタリング能力が高い高抵抗シリコンウェーハを製造する方法を提供する。

【解決手段】チョクラルスキー法により設定抵抗率に応じてドーパントを添加してシリコンインゴットを成長させ、該シリコンインゴットをスライスして設定抵抗率を有するシリコンウェーハを製造するに当たり、設定抵抗率毎に、シリコンウェーハを供するデバイス作製工程における熱処理後の当該シリコンウェーハの熱処理後抵抗率と当該シリコンウェーハが切り出されたシリコンインゴットの酸素濃度との相関を予め求めておき、シリコンインゴットの成長を、該インゴットの設定抵抗率に対する相関において、導電型が逆転する酸素濃度未満となる条件にて行う。

(もっと読む)

シリコンウェーハの製造方法

【課題】デバイス製造工程における熱処理を経た後にも高抵抗を維持するシリコンウェーハを高い生産性を以て製造する方法を提供する。

【解決手段】設定抵抗率に応じてドーパントを添加してシリコンインゴットをチョクラルスキー法により成長させ、該シリコンインゴットをスライスして前記設定抵抗率を有するシリコンウェーハを製造するに当たり、設定抵抗率毎に、シリコンウェーハを供するデバイス作製工程における熱処理後の該シリコンウェーハの熱処理後抵抗率のウェーハ厚み方向のプロファイルを、複数のシリコンインゴット酸素濃度において予め求めておき、前記プロファイルにおいて、熱処理後抵抗率がピークとなる深さまでのウェーハ表面からの厚みが、デバイスのチップ形成領域より厚いプロファイルを有する、酸素濃度となる条件にてシリコンインゴットの成長を行うようにする。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】室温(300K)以上において正孔濃度が1.0×1015cm‐3以上で、かつ、ドーパント原子濃度が1.0×1021cm‐3以下である実用的なp型ダイヤモンド半導体デバイスとその製造方法を提供すること。

【解決手段】単結晶ダイヤモンド基板1−1の上に形成された単結晶ダイヤモンド薄膜1−2の中には、二次元の正孔または電子チャンネル1−3が形成される。基板1−1の面方位と基板1−1の結晶軸「001」方向との成す角度をαs、ダイヤモンド薄膜1−2の面方位と単結晶ダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαd、チャンネル1−3の面方位とダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαcとする。単結晶ダイヤモンド薄膜1−2の表面上には、ソース電極1−4、ゲート電極1−5、ドレイン電極1−6が形成される。

(もっと読む)

ダイヤモンド半導体及び作製方法

【課題】従来技術と比較して、室温で十分に高いキャリア濃度を有するダイヤモンド半導体及び作製方法を提供すること。

【解決手段】ダイヤモンド基板11(図5(a))上にマイクロ波プラズマCVD装置を用い、メタンを反応ガスとし、基板温度700℃でダイヤモンド薄膜12を1ミクロン積層する(図5(b))。ダイヤモンド薄膜12にイオン注入装置を用い、不純物1(VI族又はII族元素)を打ち込む(図5(c))。その後、不純物2(III族又はV族元素)を打ち込んだが(図5(d))、注入条件は、打ち込んだ不純物がそれぞれ表面から0.5ミクロンの厚さの範囲内で、1×1017cm-3となるようにシミュレーションにより決定した。その後、2種類のイオンが注入されたダイヤモンド薄膜13をアニールすることにより(図5(e))、イオン注入された不純物の活性化を行い、ダイヤモンド半導体薄膜15を得た(図5(f))。

(もっと読む)

シリコン半導体基板の製造方法

【課題】単結晶炭化シリコン層からなる半導体基板を製造する技術に関し、特にシリコン基板の表層部がさらに応力緩和炭化シリコン層を有する半導体基板を製造する技術を提供する。

【解決手段】下記のステップ:(1)シリコン半導体基板を用意し(2)シリコン基板内に炭素イオンを注入してケイ素と炭素の混在した炭素含有層を形成するステップと(3)基板を熱処理して炭素含有層を応力緩和炭化シリコン膜層と酸化膜キャップを形成するステップと(4)酸化膜キャップを除去するステップと(5)第2の酸化膜キャップを形成するステップと(6)応力緩和炭化シリコン膜層と第2の酸化膜キャップとの間のシリコン層に炭素イオンを注入して、ケイ素と炭素の混在した炭素含有層を形成するステップと(7)基板を熱処理して炭素含有層を結晶成長炭化ケイ素膜層とするステップと(8)基板の表面に形成された酸化膜キャップを除去するステップを順次実施する。

(もっと読む)

シリコンウェーハおよびその製造方法

【課題】表面に適度の濃度の酸素が残存し、空孔欠陥や微小酸素析出物等が消失した無欠陥層を有し、しかもゲッタリング能力をも発揮し得るシリコンウェーハを提供する。

【解決手段】チョクラルスキー法により製造されたシリコン単結晶から得られるシリコンウェーハに、塩素が含まれる酸化性雰囲気にて熱処理を施し、少なくとも表層域における欠陥を消失させる。

(もっと読む)

ダイヤモンド半導体及び作製方法

【課題】従来技術と比較して、室温で十分に高いキャリア濃度を有するダイヤモンド半導体及び作製方法を提供すること。

【解決手段】ダイヤモンド基板11(図5(a))上にマイクロ波プラズマCVD装置を用い、メタンを反応ガスとし、基板温度700℃でダイヤモンド薄膜12を1ミクロン積層する(図5(b))。ダイヤモンド薄膜12にイオン注入装置を用い、不純物1(VI族又はII族元素)を打ち込む(図5(c))。その後、不純物2(III族又はV族元素)を打ち込んだが(図5(d))、注入条件は、打ち込んだ不純物がそれぞれ表面から0.5ミクロンの厚さの範囲内で、1×1017cm-3となるようにシミュレーションにより決定した。その後、2種類のイオンが注入されたダイヤモンド薄膜13をアニールすることにより(図5(e))、イオン注入された不純物の活性化を行い、ダイヤモンド半導体薄膜15を得た(図5(f))。

(もっと読む)

圧電性複合基板の製造方法

【課題】圧電体の単結晶基材が再利用可能になり、圧電体の単結晶基材の配置方向に応じた結晶軸の配向方向の均質な厚みの単結晶薄膜を得られ、効率的にマイクロキャビティを形成できる圧電性複合基板の製造方法の提供を図る。

【解決手段】圧電体の単結晶薄膜を備える圧電性複合基板の製造方法であって、イオン注入工程(S1)と剥離工程(S2)とを含む。イオン注入工程(S1)では、圧電体の単結晶基材1へHe+イオンを注入する。これにより、単結晶基材1の表面から内部に離れた剥離層3に、マイクロキャビティを集積して形成する。そして、剥離工程(S2)では、イオン注入工程(S1)で形成したマイクロキャビティに熱応力を作用させる。これにより、単結晶基材1を剥離層3で分断して単結晶薄膜4を剥離する。

(もっと読む)

半導体基板及びその製造方法

【課題】SOI構造を有するSOI基板を製造する際に用いられる表面に比較的小さなサイズの欠陥が無い半導体基板、及び、この半導体基板の製造方法を提供する。

【解決手段】本発明の半導体基板は、シリコン基板の表面に、シリコン酸化膜、シリコン単結晶層を順次備えてなるSOI構造を有するSOI基板を製造する際に用いられる半導体基板1であり、その表面1aの近傍に、厚みが10μm以下のシリコン単結晶層からなる窒素を含有しない領域2が形成され、この領域2を除く部分である窒素を含有する領域3の窒素濃度は1×1013〜5×1015atoms/cm3の範囲内である。

(もっと読む)

ソリッドステート材料

ホスト材料と量子スピン欠陥とを含むソリッドステートシステムであって、量子スピン欠陥が室温で約300μs以上のT2を有し、ホスト材料が、約20ppb以下の全窒素濃度を有する単結晶CVDダイヤモンドの層を含み、量子スピン欠陥が形成されている所に最も近い表面上の点に中心がある約5μmの半径の円によって定義される領域内の単結晶ダイヤモンドの表面粗さRqが約10nm以下であるソリッドステートシステム、ソリッドステートシステムの調製方法及び約20ppb以下の全窒素濃度を有する単結晶ダイヤモンドのスピントロニクス用途での使用を開示する。 (もっと読む)

ダイヤモンド材料

高い化学的純度、すなわち低い窒素含量と、高い同位体純度、すなわち低い13C含量とを有する単結晶ダイヤモンド、その製造方法及び該単結晶ダイヤモンドを含むソリッドステートシステムを開示する。 (もっと読む)

半導体基板の製造方法

【課題】CMP処理を実施することなく、0.5nm(RMS)以下の表面粗さの単結晶炭化シリコン層を有するSiCウエハを製造することができる製造方法を提供する。

【解決手段】シリコン基板1の表面に緩衝層2を形成する(S1)。緩衝層2を通して炭素イオンC+を注入することによりシリコン基板1内にシリコンと炭素の混在した炭素含有層3を形成する(S2)。シリコン基板1から緩衝層2を選択的に除去することにより炭素含有層3を露出させる(S3)。シリコン基板1を熱処理して炭素含有層3を単結晶化させることにより単結晶炭化シリコン層4を形成する(S4)。熱処理の過程で単結晶炭化シリコン層4の表面に形成された酸化層5を除去することにより単結晶炭化シリコン層4を露出させる(S5)。

(もっと読む)

厚膜材料劈開工程中の温度制御装置および温度制御方法

【課題】厚膜材料製造中における温度制御の方法および装置を提供する。

【解決手段】温度制御装置100は、注入され続いて劈開されるバルク材料110を支持する平面122を有するステージ120を備え、バルク材料は表面領域112、側部領域117、および底部領域118を有する。装置はさらに、バルク材料とステージの界面領域を通じて熱エネルギーの移動をするためにバルク材料が平面と接触する一方で表面領域が露出されるよう構成された機械的クランプ装置130と、表面領域の温度値を測定し、入力データを生成するセンサ装置150と、バルク材料の表面領域の一つまたは複数の部分に複数の粒子を注入する注入装置と、少なくともステージの平面とバルク材料の底部領域の間の界面領域を通じて表面領域の温度値を上昇および/または下降させるよう入力データを受信し、処理する制御装置160とを備える。

(もっと読む)

結晶欠陥の回復方法、結晶体の作製方法、パターン形成方法、X線量の検出体

【課題】温度上昇を伴わずに結晶欠陥の回復を行うこと、非金属の結晶欠陥を容易に制御すること。

【解決手段】酸化マグネシウム単結晶からなる基板1の中央部分12に、イオン注入を行う。これにより、この部分が着色領域2となる。この基板1の着色領域2が形成された面に、中央に円形の孔を開けたマスクを載せた状態でX線を照射する。これにより、着色領域2のX線が照射された円形部分の色が薄くなって、円形のパターン3が形成される。

(もっと読む)

SiC結晶の質を向上させる方法およびSiC半導体素子

【課題】高温アニーリングにより、キャリア捕獲中心を効果的に減少または除去するSiC層の質を向上させる方法、および該方法により作製されたSiC半導体素子を提供する。

【解決手段】(a)最初のSiC結晶層(E)における浅い表面層(A)に炭素原子(C)、珪素原子、水素原子、またはヘリウム原子をイオン注入して、注入表面層に余剰な格子間炭素原子を導入する工程と、(b)当該層を加熱することにより、注入表面層(A)からバルク層(E)へ格子間炭素原子(C)を拡散させるとともにバルク層における電気的に活性な点欠陥を不活性化する工程と、を含む、幾つかのキャリア捕獲中心を除去または減少することによりSiC層の質を向上させる方法および該方法により作製された半導体素子。上記工程の後、表面層(A)を、エッチングするかまたは機械的に除去してもよい。

(もっと読む)

酸化亜鉛材料及びそれらの調製方法

p型酸化亜鉛(ZnO)を調製する方法が記載される。p型ZnOは、n型ZnO基材に低エネルギーのアクセプタイオンを注入し、そしてアニールすることによって調製される。別の実施態様では、n型ZnO基材が低エネルギーのドナーイオンを注入することによって予備ドーピングされる。p型ZnOは種々の光電子素子において用途を有することができ、また、上記のようにして調製されたp型ZnO及びバルクn型ZnO基材から形成されたp−n接合が記載される。 (もっと読む)

1 - 20 / 34

[ Back to top ]