Fターム[4M104AA03]の内容

Fターム[4M104AA03]の下位に属するFターム

Fターム[4M104AA03]に分類される特許

1,381 - 1,400 / 1,500

絶縁ゲート電界効果トランジスタおよびその製造方法

【課題】エクステンション部に関し、その形状が安定で急峻なPN接合を有し、かつ、チャネルが形成される基板面に対して実効的な接合深さを精度よく十分に小さくする。

【解決手段】Pウェル3nおよびNウェル3pに、ゲート絶縁膜4n,4pを介してゲート電極5n,5pが形成され、Pウェル3nおよびNウェル3pのチャネルが形成される領域に各々接し互いに離れた第1エピタキシャル成長層により、2つのエクステンション部12nと12n(12pと12p)が形成されている。エクステンション部の対向端から互いに離反する向きにさらに離れた位置の第1エピタキシャル成長層上に、第2エピタキシャル成長層が形成され、これによりPMOSとNMOSの各々の側で2つのソース・ドレイン領域10nと10n(10pと10p)が形成されている。この構造では深くまで不純物を導入するイオン注入を用いないので、その活性化アニールによりエクステンション部内の不純物が基板側に熱拡散することがない。

(もっと読む)

半導体素子および電界効果トランジスタ

【課題】 良好なショットキー特性を有する電極を備えた半導体素子を提供する。また、良好なショットキー特性を有するゲート電極を備えた電界効果トランジスタを提供する。

【解決手段】 n型GaN層3の上に形成されたショットキー電極6は、WNx層4を有し、n型GaN層3とWNx層4とが接触する面において、n型GaN層3の結晶面は六方晶の(0001)面であり、WNx層4の結晶面は(111)面に配向している。WNx層4は、Zr、Ha、Nb、Ta、MoおよびWよりなる群から選ばれる少なくとも1種の元素と、窒素および炭素の少なくとも一方の元素とからなる塩化ナトリウム型構造の電極層であればよい。また、電極層の格子定数は、n型GaN層3におけるa軸格子定数を2(1/2)倍した値の0.95倍〜1.05倍であることが好ましい。

(もっと読む)

n−FET用途のためのHfSiN金属を形成する方法

【課題】 高k誘電体及び界面層を含むゲート・スタック上に、熱的に安定した新しい金属化合物を提供すること。

【解決手段】 高k誘電体及び界面層を含むゲート・スタック上に、約4.0eVから約4.5eVまで、好ましくは約4.3eVの仕事関数を有する、熱的に安定したn型金属であるHfSiNを含む金属化合物である。さらに、(約1000℃のオーダーの)高温でHfSiN/高k誘電体/界面層のスタックをアニールした後、界面層が減少され、よって、ゲート・スタックは、TaSiNを用いて達成することができない、非常に薄い等価酸化物厚(伝統的には、12Å)をもたらす。

(もっと読む)

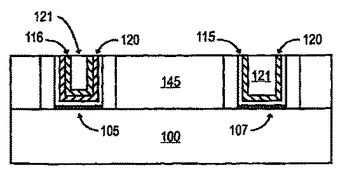

CMOSデバイスの自己形成金属シリサイド化ゲート

【課題】 CMOSデバイスの自己形成金属シリサイド化ゲートを提供すること。

【解決手段】 シリサイドが自己形成され(すなわち、別個の金属/シリコン反応ステップを必要とせずに形成され)、シリコン材料のCMP又はエッチ・バックを必要としない、金属シリサイド・ゲートをFETデバイスに形成するためのプロセス。第1のシリコン材料層(3)(ポリシリコン又はアモルファス・シリコン)が、ゲート誘電体(2)の上に形成され、次いで、金属層(4)が第1のシリコン材料層(3)の上に形成され、金属層(4)の上に第2のシリコン材料層(5)が形成される。その後、ソース/ドレイン活性化アニールのような高温(700℃より高い)処理ステップが実施され、このステップは、金属層(4)の金属を第1のシリコン材料層(13)におけるシリコン材料と反応させることにより、ゲート誘電体(2)の上にシリサイド層(30)を形成するのに有効である。第2の高温処理ステップ(ソース/ドレインのシリサイド化のような)を実施することができ、これは第2のシリコン材料層(5)におけるシリコン材料から第2のシリサイド層(50)を形成するのに有効である。シリサイド層の厚さは、高温処理において、第1のシリコン材料層の実質的にすべて及び第2のシリコン材料層の少なくとも一部が、シリサイド材料で置き換えられるような厚さである。従って、完全シリサイド化ゲート構造体を生成することができる。

(もっと読む)

半導体装置の作製方法

【課題】従来のCMPプロセスを用いることなく、高アスペクト比の開口を有する接続孔にも良好な埋め込みが可能である半導体装置の作製方法を提供する。また、従来よりも少ない工程数で、配線形成が可能な方法を提供することを目的とする。更には、高集積化された半導体装置の歩留まり高い作製方法を提案する。

【解決手段】複数の空孔を有する絶縁膜表面に撥水表面を有する膜を形成し、撥水表面を有する膜の一部に光を照射して、親水表面を有する領域を形成した後、親水表面を有する領域に導電性粒子を有する液状物質を吐出し、焼成して導電膜を形成することを特徴とする。

(もっと読む)

ナノチューブ/ナノワイヤFETのための自己整合プロセス

【課題】 ナノチューブ及びナノワイヤのような一次元ナノ構造体を含むCMOSデバイスを製造するための自己整合プロセスを提供すること。

【解決手段】 半導体構造体は、少なくとも1つのゲート領域が上に配置され、少なくとも1つのゲート領域が少なくとも1つの一次元ナノ構造体の層を含む、基板と、基板の表面上に配置され、少なくとも1つの一次元ナノ構造体の層の縁と整合される、金属カーバイド・コンタクトと、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 パッド電極下に能動層が配置されている場合においても、パッド電極下における密着性を確保しつつ、バリアメタル構造を能動面上に安定して形成できるようにする。

【解決手段】 不純物拡散層5a、5bの表面が覆われるようにして層間絶縁膜6上にバリアメタル膜8を形成し、フォトリソグラフィー技術を用いることにより、開口部7が覆われるようにしてパッド電極16下に配置されるバリアメタル膜8の表面を露出させるレジストパターンRを形成し、レジストパターンRをマスクとして、バリアメタル膜8をエッチングすることにより、パッド電極16下に配置される層間絶縁膜6上のバリアメタル膜8を除去し、バリアメタル膜8を介してゲート電極4および不純物拡散層5a、5bに接続された配線層9を層間絶縁膜6上に形成し、ゲート電極4および不純物拡散層5a、5b上に配置されたパッド電極16を形成する。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程でNiシリサイドを形成する。

【解決手段】基板上に半導体膜を形成し、前記基板を加熱しながら前記半導体膜上にNi膜を成膜することにより、前記半導体膜にNiシリサイドを形成することを特徴とする。また基板上に半導体膜を形成し、前記基板を450℃以上に加熱しながら前記半導体膜上にNi膜を成膜することにより、前記半導体膜にNiシリサイドを形成することを特徴とする。また基板上に半導体膜を形成し、前記基板を450℃以上に加熱しながら前記半導体膜上にNi膜を10nm以上成膜することにより、前記半導体膜にNiシリサイドを形成することを特徴とする。

(もっと読む)

炭化ケイ素半導体デバイスのためのエッジ終端構造及びその製造方法

炭化ケイ素デバイスのためのエッジ終端構造は、炭化ケイ素ベースの半導体接合に近接し、この半導体接合から間隔をおいて配置された、炭化ケイ素層中の複数の同心円のフローティングガードリングを有する。酸化膜などの絶縁層が、これらのフローティングガードリング上に設けられ、炭化ケイ素表面電荷補償領域が、これらのフローティングガードリング間に設けられ、この絶縁層に隣接している。かかるエッジ終端構造の製造方法もまた提供される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 優れた特性を有するとともに信頼性が向上し、またSiCウエハを用いることができると。

【解決手段】 SiCチップ9には、複数個のショットキーバリアダイオードのユニット10が形成され、各ユニット10は独立した外部出力電極4を持っている。SiCチップ9に形成されたユニット10のうち良品ユニットの外部出力電極4のみに、バンプ11(直径が数10〜数100μm)が形成され、耐圧がなかったりリーク電流が多かったりする不良品ユニットの外部出力電極4の上にはバンプは形成されていない。不良品ユニットにはバンプが形成されていないので、ショットキーバリア側電極3は外部出力電極4からバンプ11、配線基板12の配線層13、外部リード13aへと外部と並列接続され、良品のユニット10の外部出力電極4のみが並列に接続されている。

(もっと読む)

半導体装置

【課題】製造工程が容易で且つ充分な耐圧特性を得ることが可能なJTE構造を得る。

【解決手段】半導体装置は、SiC基板1に形成されたn型のドリフト層2にショットキ接続するアノード電極3とその外周部に形成されたJTE領域6を有する。JTE領域6は、ドリフト層2の上部におけるアノード電極3のエッジの下を含む領域に形成された第1のp型領域6aと、その外側に形成され第1のp型領域6aよりも不純物面濃度が低い第2のp型領域6bとから成る。第2のp型領域6bは、アノード電極3のエッジから15μm以上外側に配設される。第1のp型領域6aの不純物面濃度は、1.8×1013〜4×1013cm-2であり、第2のp型領域6bの不純物面濃度は、1×1013〜2.5×1013cm-2である。

(もっと読む)

表面改質によるパターン化方法

(a)再配置可能なアパーチャマスクを基板の近くに配置する工程と、(b)基板の部分を表面改質処理に選択的に曝す工程であって、曝された部分が、アパーチャマスクの1つ以上のアパーチャによって画定される工程とによって表面改質をパターン化する方法。 (もっと読む)

電界効果型トランジスタ

【課題】新規なトランジスタを提供する。

【解決手段】ソース電極708、ドレイン電極709、ゲート電極712、及び電子キャリア濃度が1018/cm3未満である非晶質酸化物を含む活性層を備え、且つ該ゲート電極と、該ソース及びドレイン電極が自己整合していることを特徴とする。

(もっと読む)

半導体基板およびその製造方法

【課題】基板裏面の略全面を覆うコンタクト電極膜の成膜後に高温処理を必要とする場合であれ、基板の膜厚によることなく同処理の加熱に起因する基板の反りを抑制することのできる半導体基板およびその製造方法を提供する。

【解決手段】この半導体基板は、基板1の表面に所望の半導体素子を形成するための領域を有し、基板裏面側には略全面にわたって同面を被覆するコンタクト電極膜2が設けられる。そして、コンタクト電極膜2は、そのコンタクト領域が基板裏面の略全面にわたって細分化される態様でパターニングされ、詳しくは基板裏面の略全面にわたる多数の正方形からなる集合パターンをもって形成される。

(もっと読む)

半導体装置およびその作製方法、並びに電子機器

【課題】アクティブマトリクス型の半導体装置のゲート電極とゲート配線の配置を工夫することにより、画面の大面積化を可能とする。

【解決手段】表示領域に設けられた画素TFTが含むゲート電極は、第1の導電層により形成されている。また、表示領域に設けられたゲート配線は、第2の導電層で形成されている。ゲート電極はゲート配線と接続部で電気的に接触している。接続部は、画素TFTが含む半導体層の外側に設けられている。

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】 後続するコンタクト・ホール工程で使用される層間絶縁(ILD)エッチング停止層を有する高電圧用トランジスタ・デバイスを提供する。

【解決手段】 エッチング停止層は、10Ω−cmより大きい抵抗を有する高抵抗膜である。この結果、ゲート部において5Vより大きい高電圧を駆動する場合のリークを防止し、破壊電圧は向上する。高電圧用デバイスの製造方法は、現在の低電圧デバイスの製造工程と中電圧デバイスの製造工程と混載可能である。

(もっと読む)

半導体装置

【課題】基板強度を保持しつつオン抵抗を低減し得る半導体装置を提供する。

【解決手段】網目状の凸部により形成された複数の凹部を裏面に有し、第1の不純物濃度を有する半導体からなる支持体21と、前記支持体の前記裏面に対向する表面に形成され、前記第1の不純物濃度よりも低い第2の不純物濃度を有する半導体層3と、前記半導体層3に形成された半導体素子とを具備することを特徴とする。

(もっと読む)

高誘電率ゲート誘電体および金属ゲート電極をもつ半導体デバイスの作成方法

半導体デバイスを作成する方法に関する。該方法は、基板上で二酸化ケイ素層に窒素を加えて窒化二酸化ケイ素層を形成することを含む。窒化二酸化ケイ素層の上に犠牲層を形成したのち、犠牲層が除去されて溝が生成される。窒化二酸化ケイ素層の上で溝の中に高誘電率ゲート誘電体層が形成され、該高誘電率ゲート誘電体層の上に金属ゲート電極が形成される。

(もっと読む)

(もっと読む)

トランジスタおよびその作製方法、並びに半導体装置

【課題】アクティブマトリクス型の半導体装置のゲート電極とゲート配線の配置を工夫することにより、画面の大面積化を可能とする。

【解決手段】表示領域に設けられた画素TFTが含むゲート電極は、第1の導電層により形成されている。また、表示領域に設けられたゲート配線は、第2の導電層で形成されている。ゲート電極はゲート配線と接続部で電気的に接触している。接続部は、画素TFTが含む半導体層の外側に設けられている。

(もっと読む)

熱処理システム

【課題】

半導体ウェーハなどの熱処理工程で使用する、1000℃以上まで使用可能な小型の炉体と、これを用いて小型で省スペースに優れる枚葉式熱処理システムを提供する。

【解決手段】

蓄熱板と、蓄熱板の裏側に配置する加熱ヒーターと、さらに前記加熱ヒーターの裏側に配置する熱遮蔽体とで加熱ユニットを構成し、前記加熱ユニットと大略同一構造のもう一つの加熱ユニットを、互いに蓄熱板が対向するようにして間隔をあけて配置し、前記蓄熱板間の間隙に被加熱物を配置して加熱処理をすることを特徴とする炉体ユニットを用いて熱処理システムを構成する。

炉体ユニットには、大規模な断熱材などが存在せず、小型化が可能となる。

(もっと読む)

1,381 - 1,400 / 1,500

[ Back to top ]