Fターム[4M104AA03]の内容

Fターム[4M104AA03]の下位に属するFターム

Fターム[4M104AA03]に分類される特許

1,461 - 1,480 / 1,500

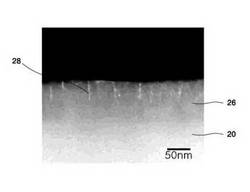

ワイヤー形態の金属シリサイドを備えるSiベースの物質層及びその製造方法

【課題】ワイヤー形態の金属シリサイドを備えるSiベースの物質層及びその製造方法を提供する。

【解決手段】複数のグレインを備え、グレイン境界に金属シリサイドが形成されたSiベースの物質層である。また、Siベースの基板に所定厚さの非晶質層を形成する工程と、非晶質層に所定の金属イオンをドーピングする工程と、金属イオンがドーピングされた非晶質層をアニーリングする工程とを含むSiベースの物質層の製造方法である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 SiC基板に対して良好なオーミック接触を得ることができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】 n+型SiC層1の露出面の状態を荒らす工程と、荒らされたn+型SiC層1の露出面に電極を形成する工程とを有し、前記荒らす工程は、前記露出面についての研磨処理又はレーザー照射Lを有することを特徴とする。

(もっと読む)

SIC半導体デバイス用のシリコン・リッチのニッケル珪素化合物オーミック・コンタクト

本方法は、炭化珪素面上に、ニッケル及びシリコンのデポジット膜を、これらいずれかの元素が炭化珪素と反応する温度未満において、デポジット膜におけるシリコンの原子分率がニッケルの原子分率よりも大きくなるようなそれぞれの割合で形成するステップと、ニッケル及びシリコンのデポジット膜を、シリコンの原子分率がニッケルの原子分率よりも大きいニッケル−シリコン化合物が形成する温度であるが、いずれかの元素が炭化珪素と反応する温度未満で加熱するステップとを含む。本方法は更に、ニッケル−シリコン化合物を、デポジット膜の加熱温度よりも高い温度まで、自由炭素が存在しない状態図の領域において、アニールするステップを含むことができる。  (もっと読む)

(もっと読む)

SiC半導体装置およびSiC半導体装置の製造方法

【課題】 n型SiCに対して良好なオーミック接触を得ることができるSiC半導体装置およびSiC半導体装置の製造方法を提供することを目的とする。

【解決手段】 第1の主面と該第1の主面に背向する第2の主面とを有するn+型SiC基板11と、第2の主面上に形成されたエピタキシャル層13と、エピタキシャル層13上に形成されると共に、エピタキシャル層13とオーミック接触した電極14とを有することを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 SiC基板に対して良好なオーミック接触を得ることができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】 n+型SiC層1の露出面の状態を荒らす工程と、荒らされたn+型SiC層1の露出面に電極9を形成する工程とを有することを特徴とする。

(もっと読む)

半導体素子および半導体素子の製造方法

【課題】 n型SiCに対して良好なオーミック接触を得ることができる半導体素子および半導体素子の製造方法を提供する。

【解決手段】 n型SiC基板1上に、1b族と8族のFe列以外とのいずれかに属する元素のうち、いずれか1つ又は2つ以上からなる第1の貴金属膜2を形成し、第1の貴金属膜2上に、4a族と5a族と6a族と7a族と8族のFe列とのいずれかに属する元素のうち、いずれか1つ又は2つ以上からなる耐熱金属膜3を形成し、耐熱金属膜3上に、1b族と8族のFe列以外とのいずれかに属する元素のうち、いずれか1つ又は2つ以上からなる第2の貴金属膜4を形成し、その後、これらを960℃から1000℃までの範囲で加熱する。

(もっと読む)

半導体装置及びその製造方法

【課題】炭化珪素層に対する良好なコンタクトを確保しつつ、炭化珪素層に接続された電極の剥離を抑制する。

【解決手段】炭化珪素層11を有する半導体装置の製造方法であって、(A)炭化珪素層11の上に導電層21を形成する工程と、(B)導電層21と炭化珪素層11を反応させて、炭化珪素層11に接する反応層12およびシリサイド層23からなる合金層を形成する工程と、(C)シリサイド層23の少なくとも一部を除去することにより、反応層12の表面の少なくとも一部を露出させる工程と、露出させた反応層12の表面上に電極層13を形成する工程とを含む。

(もっと読む)

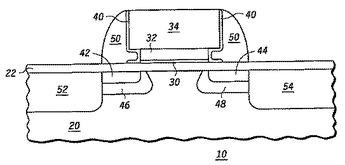

ナノクラスタ電荷蓄積デバイスの形成方法

一実施形態では、ナノクラスタ電荷蓄積デバイスを形成する方法が提供される。半導体装置(10)の第1の領域(26および30)が1つまたは複数の非電荷蓄積デバイスを配置するために特定される。この半導体装置の第2の領域(28)が1つまたは複数の電荷蓄積デバイスを配置するために特定される。この1つまたは複数の非電荷蓄積デバイスのゲート絶縁体として使用されるゲート酸化物(22)がこの半導体装置の第1の領域(26および30)中に形成され、引き続きナノクラスタ電荷蓄積層がこの半導体装置の第2の領域(28)中に形成される。  (もっと読む)

(もっと読む)

バリア層を含む発光ダイオードおよびその製造方法

発光ダイオードなどの半導体発光素子は、基板と、基板上に設けられ、発光ダイオード領域などの発光領域を含むエピタキシャル領域と、エピタキシャル領域上に設けられ、反射層を含む多層導電スタックとを含む。反射層上にはバリア層が設けられ、反射層の側壁上に延びている。多層導電スタックは、反射体とエピタキシャル領域の間にオーミック層も含むことができる。バリア層はさらに、オーミック層の側壁上に延びている。バリア層は、多層導電スタック外部のエピタキシャル領域上へも延びていてもよい。バリア層は、交互に重ねた一連の第1および第2の副層として製作できる。  (もっと読む)

(もっと読む)

半導体材料の予めパッシベーション化された表面を金属被覆するための方法及びその方法によって得られる材料

本発明は、半導体材料の予めパッシベーション化した表面を金属被覆するための方法及びその結果得られる材料に関する。本発明は、マイクロエレクトロニクスに適用可能であり、材料(2)の表面を前処理することにより、材料内に水素原子又は金属元素を吸着可能な結合を形成するステップ、表面をパッシベーション化化合物に露出することにより、好ましくは表面の直下に位置する一又は複数の層をパッシベーション化するステップ、及び表面(4)を水素原子へ又は金属元素に露出することにより、該表面を金属被覆するステップを含むことを特徴とする。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】 ナノインプリント法を用いることでコストを抑えることができる、半導体装置の作製方法の提案を課題とする。

【解決手段】 本発明は、島状の半導体膜上にゲート絶縁膜と、導電膜と、レジストとを順に形成し、パターンが形成されたモールドをレジストに押し付けた状態でレジストの硬化を行なうことで、パターンをレジストに転写し、導電膜の一部が露出するまでパターンが転写されたレジストの表面をアッシングし、アッシングされたレジストをマスクとして用い、導電膜をエッチングすることを特徴とする。

(もっと読む)

半導体装置及びその作製方法

【課題】本発明は、低コストで大量生産が可能である半導体装置及びその作製方法を提供する。また、非常に膜厚の薄い集積回路を用いた半導体装置、及びその作製方法を提供する。更には、低消費電力である半導体装置及びその作製方法を提供する。

【解決手段】本発明は、絶縁表面上に半導体不揮発性記憶素子トランジスタを有し、メモリトランジスタのフローティングゲート電極が、複数の導電性粒子又は半導体粒子で形成されていることを特徴とする半導体装置である。

(もっと読む)

ニッケルゲルマノシリサイド化したゲートを組み込んだMOSFETおよびこれらのMOSFETを形成する方法

MOSFETのゲートまたはMOSFETのソースまたはドレイン領域は、シリコンゲルマニウムまたは多結晶シリコンゲルマニウムを含む。好ましくはニッケルシリサイドのモノシリサイドフェーズを含むニッケルゲルマノシリサイド(62、64)を形成すべく、ニッケルでのシリサイデーションを実行する。

ニッケルモノシリサイドによって呈される優れたシート抵抗を実質的に保持する一方、シリサイド中にゲルマニウムを含むことは、モノシリサイドフェーズが形成され得るより温度領域をより広くする。その結果、ニッケルゲルマノシリサイドは、後続のプロセスの間、ニッケルモノシリサイドよりも、より高い温度に耐えることができる。しかしながら、ニッケルモノシリサイドとほぼ同一のシート抵抗および他の有益な特性を提供する。  (もっと読む)

(もっと読む)

炭化ケイ素への電極形成方法、電極形成装置、電極を用いた半導体素子およびその製造方法

【目的】炭化ケイ素基板に対して、メッキ法によりニッケル−炭化ケイ素基板間に汚染物質の少ないニッケル電極形成方法および装置を提供することにある。

【構成】炭化ケイ素基板にメッキによりニッケル電極を形成する前に、炭化ケイ素のバンドギャップよりも大きなエネルギーを有する波長領域の光を照射しつつ、陽極側に電圧を印加することでエッチングを行う。このとき電解液の温度を60℃以上に上昇させることで、エッチングが効果的に行える。エッチング後、炭化ケイ素基板に陰極側の電圧を印加することでニッケルのメッキを行う。これにより、ニッケル−炭化ケイ素界面に汚染物質の少ないニッケル電極を形成することができる。さらに、本発明の電極形成方法を半導体素子の製造工程において、ニッケルショットキー電極の形成、ニッケルオーミック電極の形成に適用することにより、良質の半導体素子を効率的に製造することができる。

(もっと読む)

複数の半導体層を備えた半導体デバイス

半導体デバイス構造(10)では、N及びPチャネルトランジスタキャリア移動度を別々に最適化するため、二つの半導体層(16、20)が使用される。これを決定する導電特性は、半導体の材料の種類、結晶面、配向性及び歪みの組み合わせである。シリコンゲルマニウムの半導体材料、圧縮性歪み、(100)の結晶面及び<100>の配向性を特徴とする導電特性の場合、Pチャネルトランジスタ(38)においてホール移動度が向上する。また、結晶面は(111)であってもよく、この場合、配向性は重要ではない。N型伝導に適した基板は、P型伝導に適した(又は最適)基板とは異なる。Nチャネルトランジスタ(40)は、好ましくは、引っ張り歪み、シリコン半導体材料及び(100)面を有する。別の半導体層(16、20)では、N及びPチャネルトランジスタ(38、40)はいずれもキャリア移動度に対し最適化される。  (もっと読む)

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】電極が形成される半導体層の表面平坦性や、シート抵抗などが何れも優れた、高性能化や小型化に好適な電界効果トランジスタを実現すること。

【解決手段】ノンドープのGaN結晶から成る半導体層103(バッファ層)の上には、厚さ約40nmのノンドープのAl0.2 Ga0.8 Nから成る半導体層104が積層されている。この半導体層104は、本発明に基づく厚さ約30nmの急峻界面提供層1041と、本発明に基づく厚さ約10nmの電極接続面提供層1042の計2層の半導体層から構成されている。これらは双方共に上記の通りノンドープのAl0.2 Ga0.8 Nから形成されているが、急峻界面提供層1041を結晶成長させる際には、キャリアガスとしてH2 を使用した。また、電極接続面提供層1042を結晶成長させる際には、キャリアガスとしてN2 を使用した。

(もっと読む)

再成長オーミックコンタクト領域を有する窒化物ベースのトランジスタの製作方法及び再成長オーミックコンタクト領域を有する窒化物ベースのトランジスタ

トランジスタ製作は、基板上に窒化物ベースのチャネル層を形成すること、窒化物ベースのチャネル層上に障壁層を形成すること、窒化物ベースのチャネル層のコンタクト領域を露出させるように障壁層にコンタクト凹部を形成すること、例えば、低温堆積プロセスを使用して、窒化物ベースのチャネル層の露出されたコンタクト領域上にコンタクト層を形成すること、コンタクト層上にオーミックコンタクトを形成すること、及びオーミックコンタクトに隣接した障壁層上に配置されたゲートコンタクトを形成すること、を含んでいる。また、高電子移動度トランジスタ(HEMT)及びHEMTの製作方法が提供される。HEMTは、基板上の窒化物ベースのチャネル層と、窒化物ベースのチャネル層上の障壁層と、チャネル層の中まで延びる、障壁層のコンタクト凹部と、コンタクト凹部の中の窒化物ベースのチャネル層上の窒化物ベースのn型半導体材料のコンタクト領域と、窒化物ベースのコンタクト領域上のオーミックコンタクトと、このオーミックコンタクトに隣接した障壁層上に配置されたゲートコンタクトと、を含んでいる。窒化物ベースのn型半導体材料のコンタクト領域及び窒化物ベースのチャネル層は、表面積拡大構造を含んでいる。  (もっと読む)

(もっと読む)

フィールドプレートに接続されたソース領域を有する、ワイドバンドギャップ電界効果トランジスタ

本発明に係る電界効果トランジスタは、基板(12)上に連続的に形成されるバッファ及びチャネル層(16)を備える。ソース電極(18)、ドレイン電極(20)、並びに、ソース及びドレイン電極間にあるゲート(22)はすべて、チャネル層に電気的に接続して形成される。スペーサ層(26)は、前記ゲートと前記ドレイン電極との間にあるチャネル層の表面の少なくとも一部の上に形成され、フィールドプレート(30)は、前記ゲート及びチャネル層から絶縁されるスペーサ層上に形成される。フィールドプレート(30)は、少なくとも1つの導電性パスによってソース電極に電気的に接続され、金属半導体電界効果トランジスタ内におけるピーク操作電界を低減する。  (もっと読む)

(もっと読む)

有機金属前駆体化合物

本発明は、式i−PrN=Ta(NR1R2)3[式中、R1及びR2は、同じか又は異なり、1〜3個の炭素原子を有するアルキルであり、但し、(i)R1がエチルの場合、R2はエチル以外であり、(ii)R2がエチルの場合、R1はエチル以外である]により表される有機金属前駆体化合物、並びに前記有機金属前駆体化合物から被膜、コーティング又は粉末を製造する方法に関する。 (もっと読む)

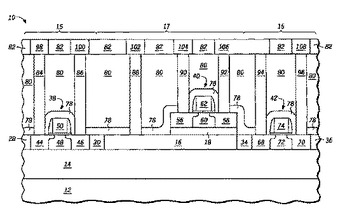

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

1,461 - 1,480 / 1,500

[ Back to top ]